Abstract

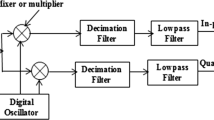

Design of Reversible logic gate enabled Reconfigurable Direct digital synthesizer is evaluated here. The need for Direct Digital Synthesizers (DDS) inherently finds application in the area of radio frequency communication. DDS is a method of producing an analog waveform—usually a sine wave—by generating a time-varying signal in digital form and then performing a digital-to-analog conversion. The proposed design presents an important analysis based on Reversible logic gates for the application of DDS which is a powerful device employed to produce standard signal sweeps from lowest frequency to highest frequency. The sweeps of DDS frequency depends on the configurable frequency words produced by high speed Field Programmable Gate Array (FPGA) platforms. Because operations within DDS devices are primarily digital, it can offer fast switching between output frequencies, fine frequency resolution, and operation over a broad spectrum of frequencies. With advances in design and process technology, today’s DDS devices are very compact and draw little power. Here the proposed system focuses on development of DDS through Artificial Intelligence (AI) with Field Programmable Gate Array (FPGA) devices. The primary need for FPGA and AI combination provides the replacement of analog Phase Locked Loop (PLL) in traditional DDS circuits. The fully digital architecture enable the system able to configure the digital PLL developed inside the FPGA core. Low noise and Low power factor is being achieved through low power techniques utilized in the architecture development part. The proposed system increase the sweep frequency resolution, Reverse fluctuations through leakage voltage etc.

Similar content being viewed by others

References

Hung WNN, Song X, Yang G, Perkowski M (2004) Quantum logic synthesis by symbolic reachability analysis. Proc Design Auto Conf (San Diego, California, USA: 838-841

Allahyari-Abhari A, Wille R, Drechsler R (2015) An examination of the NCV-|v1| Quantum library based on minimal circuits. Proc 45th Int Symp Multiple-Valued Logic (Waterloo, Canada)

Al-Rabadi AN (2009) Closed–System quantum logic network implementation of the viterbi algorithm. Facta Universitatis Ser Elec Energy 22, Pg.11-13.

Feynman R (1985) Quantum mechanical computers. Optics News 11, Pg. 11-20.

Barenco A, Bennet CH, Cleve R, Di Vinchenzo D, Margolus N, Shor P, Sleator T, Smolin J, Weinfurter H (1995) Elementary gates for quantum computation. Am Phys Soc 52:3457–3467

Bennet CH (1973) Logical reversibility of computation. IBM J Res Dev 17:525

Abbasalizadeh S, Forouzandeh B, Aghababa (2013), H. 4 bit comparator design based on reversible logic gates. Lect Notes Inform Theory

Landauer R (1961) Irreversibility and heat generation in the computing process. IBM J Res Dev 5:183

Garipelly R, Kiran PM, Kumar AS (2013) A review on reversible logic gates and their implementation. Int J Emerg Technol Adv Eng 3

Kharchenko HV, Tkalich IO, Vdovychenko YI (2009) Design ASIC-based frequency synthesizer. CADSM’2009: 164–165

Kerntopf P, Perkowaski MA, Khan MHA (2004) On universality of general reversible multiple-valued logic gates. Proc 34th Int Sym Multiple-Valued Logic: 68–73. doi:https://doi.org/10.1109/ISMVL.2004.1319922

Fredkin E, Toffoli T (1982) Conservative logic. Intl J Theor Phys 21:219–253

Christo MS, Meenakshi S (2017) Enhancing rumor riding protocol in P2P network with Cryptographic puzzle through challenge question method. Comput Electr Eng

Wang M, Wen Z, Chen L, Zhang Y (2008) A novel Dll-based configurable frequency synthesizer. IEEE Int Conf Neural Netw Sign Process Zhenjiang, China

Omran H, Sharaf K, Ibrahim M (2009) An All-Digital Direct Digital Synthesizer Fully Implemented on FPGA. In: IEEE

Khilar S, Parmar K, S, Dasgupta KS (2008) Design and analysis of direct digital frequency synthesizer. 2008 First Int Conf Emerg Trends Eng Technol. https://doi.org/10.1109/icetet.2008.60

Rust J, Paul S (2012) A direct digital frequency synthesizer based on automatic nonuniform piecewise function generation. 20th Eur Sign Process Conf (EUSIPCO 2012)

Mehra R, Kamboj B (2012) Efficient FPGA implementation of direct digital frequency synthesizer for software radios. Int J Comput Appl (0975 – 8887) 37(10)

Omran QK, Islam MT, Misran N (2013) A new approach to the design of low-complexity direct digital frequency synthesizer. PRZEGLĄD ELEKTROTECHNICZNY, ISSN 0033-2097, R. 89 NR 5

Jianga Z, Xub R, Huangc H, Dongd C (2013) Design of a ROM-less direct digital frequency synthesizer on FPGA. Int J Signal Process Image Process Pattern Recogn 8(5):327–340

Spencer DT, Drake T, Briles TC, Stone J, Sinclair LC, Fredrick C, Papp SB (2018) An optical-frequency synthesizer using integrated photonics. Nature 557(7703):81–85

A Technical Tutorial on Digital Data Synthesizer, Analog Devices. https://www.analog.com/media/.../tutorials/450968421DDS_Tutorial_rev12-2-99

Naguboina GC, Anusudha K (2017) Design and synthesis of combinational circuits using reversible decoder in Xilinx. IEEE Int Conf Comput Commun Signal Process (ICCCSP-2017)

Vankka J (2005) Digital synthesizers and transmitters for software radio. Springer

Brown J (2000) The quest for the quantum computer. Touchstone, New York

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Bommi, R.M., Raja, S.S. High Performance Reversible Direct Data Synthesizer for Radio Frequency Applications. Mobile Netw Appl 24, 224–233 (2019). https://doi.org/10.1007/s11036-018-1200-2

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11036-018-1200-2