Abstract

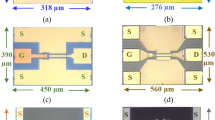

Specific HEMTs (High Electron Mobility Transistors) with different gate geometries have been realized on the same AlGaAs/GaAs heterojunction. Under the same operating conditions with a power consumption of 30 μW, experimental results at 4.2 K and low frequency range show that the input voltage noise is almost inversely proportional to the square root of the input capacitance: a noise value as low as \(0.46~\mathrm{nV}/\sqrt{\mathrm{Hz}}\) at 1 kHz has been obtained with an input capacitance of about 100 pF.

Similar content being viewed by others

References

F. Ayela, J.L. Bret, J. Chaussy, Rev. Sci. Instrum. 62, 2816 (1991)

D.V. Camin, C.F. Colombo, V. Grassi, J. Phys., IV 12(3), 37 (2002)

E. Gremion, D. Niepce, A. Cavanna, U. Gennser, Y. Jin, Appl. Phys. Lett. 97, 233505 (2010)

N. Oukhanski, M. Grajcar, E. Il’ichev, H.-G. Meyer, Rev. Sci. Instrum. 74, 1145 (2003)

A.M. Robinson, V.I. Talyanskii, Rev. Sci. Instrum. 75, 3169 (2004)

R. Plana, L. Escotte, O. Llopis, H. Amine, T. Parra, M. Gayral, J. Graffeuil, IEEE Trans. Electron Devices 40, 852 (1993)

F.N. Hooge, Phys. Lett. 29A, 139 (1969)

T. Lucas, Y. Jin, J. Phys., IV 12(3), 113 (2002)

To be published

Acknowledgements

This work was supported in part by the Réseau RENATECH, “le RTRA Triangle de la Physique” grants No. 2008-015T and No. 2009-004T and European FP7 grant No. 263455. Q.D. is funded by the BDI CNRS/CEA. We acknowledge stimulating discussions with H. Bouchiat, D.C. Glattli, C. Pigot, F. Pierre and A. Anthore. We thank E. Cambril and L. Couraud for technical help.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Dong, Q., Liang, Y.X., Gennser, U. et al. The Role of the Gate Geometry for Cryogenic HEMTs: Towards an Input Voltage Noise Below \(0.5~\mathrm{nV}/\sqrt{\mathrm{Hz}}\) at 1 kHz and 4.2 K. J Low Temp Phys 167, 626–631 (2012). https://doi.org/10.1007/s10909-012-0459-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10909-012-0459-0