Abstract

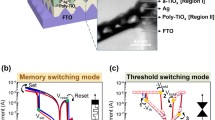

The study presents a non-volatile memory (NVM) device created from an axial NiO-nanowire (NW)/β-Ga2O3-NW heterostructure (HS) using GLAD within the RF/DC sputtering chamber. The device performance of the axial NiO-NW/β-Ga2O3-NW HS was compared to the NiO-thin film (TF)/β-Ga2O3-TF HS device. Moreover, the axial NiO-NW/β-Ga2O3-NW HS sample superior crystallinity as compared to its 2-D HS counterpart confirming a high degree of structural alignment in case of axial HS NW. The axial NiO-NW/β-Ga2O3-NW HS device showed a high accumulation capacitance of 25 pF and a conductance of 28 × 10−6 S measured at 1 MHz frequency. Furthermore, the axial NiO-NW/β-Ga2O3-NW HS memory device displayed good characteristics including a low interface state density (\({D}_{it}\)) of 1.13 × 1011 eV−1 cm−2 and a significant memory window of 2.84 V at ± 8 V sweeping voltage as compared to the TF HS (\({D}_{it}\) of 1.42 × 1011 eV−1 cm−2 and memory window of 0.56 V at ± 8 V). Additionally, the axial NiO-NW/β-Ga2O3-NW HS memory device exhibited good endurance over 1000 programming/erasing cycles as well as reliable retention properties (memory window stays constant up to 3 × 104 s). Therefore, axial NiO-NW/β-Ga2O3-NW HS memory device, benefiting from the high-quality type-II junction emerges as a promising choice for future NVM applications.

Similar content being viewed by others

Data availability

The data will be made available on reasonable request.

References

P. Li, Z. Zhang, Z. Zhuang, J. Guo, Z. Fang, S.L. Fereja, W. Chen, Pd-doping-induced oxygen vacancies in one-dimensional tungsten oxide nanowires for enhanced acetone gas sensing. Anal. Chem. 93(20), 7465–7472 (2021). https://doi.org/10.1021/acs.analchem.1c00568

M. Dhananjaya, N.G. Prakash, A.L. Narayana, O.M. Hussain, Microstructural and supercapacitive properties of one-dimensional vanadium pentoxide nanowires synthesized by hydrothermal method. Appl. Phys. A 124, 1–7 (2018). https://doi.org/10.1007/s00339-017-1522-0

I. Chakraborty, A. Jaiswal, A.K. Saha, S.K. Gupta, K. Roy, Pathways to efficient neuromorphic computing with non-volatile memory technologies. Appl. Phys. Rev. (2020). https://doi.org/10.1063/1.5113536

Q.F. Ou, B.S. Xiong, L. Yu, J. Wen, L. Wang, Y. Tong, In-memory logic operations and neuromorphic computing in non-volatile random-access memory. Materials. 13(16), 3532 (2020). https://doi.org/10.3390/ma13163532

Y. Zhai, Y. Dou, D. Zhao, P.F. Fulvio, R.T. Mayes, S. Dai, Carbon materials for chemical capacitive energy storage. Adv. Mater. 23(42), 4828–4850 (2011). doi.org/10.10 02/adma.201100984

G. Choi, H.H. Yoon, S. Jung, Y. Jeon, J.Y. Lee, W. Bahng, K. Park, Schottky barrier modulation of metal/4H-SiC junction with thin interface spacer driven by surface polarization charge on 4H-SiC substrate. Appl. Phys. Lett. (2015). https://doi.org/10.1063/1.4938070

F. Mo, T. Saraya, T. Hiramoto, M. Kobayashi, Reliability characteristics of metal/ferroelectric-HfO2/IGZO/metal capacitor for non-volatile memory application. Appl. Phys. Express (2020). https://doi.org/10.35848/1882-0786/ab9a92

Z.B. Yan, J.M. Liu, Coexistence of high-performance resistance and capacitance memory based on multilayered metal-oxide structures. Sci. Rep. 3(1), 2482 (2013).

D. Sarkar, G.G. Khan, A.K. Singh, K. Mandal, High-performance pseudocapacitor electrodes based on α-Fe2O3/MnO2 core–shell nanowire heterostructure arrays. J. Phys. Chem. C 117(30), 15523–15531 (2013). https://doi.org/10.1021/jp4039573

P. Chen, S. Wu, P. Li, J. Zhai, B. Shen, Great enhancement of energy storage density and power density in BNBT/x BFO multilayer thin film hetero-structures. Inorg. Chem. Front. 5(9), 2300–2305 (2018). https://doi.org/10.1039/C8QI00487K

Z.T. Xu, K.J. Jin, L. Gu, Y.L. Jin, C. Ge, C. Wang, H.Z. Guo, H.B. Lu, R.Q. Zhao, G.Z. Yang, Evidence for a crucial role played by oxygen vacancies in LaMnO3 resistive switching memories. Small. 8(8), 1279–1284 (2012). https://doi.org/10.1002/smll.201101796

R. Lahiri, A. Mondal, Superior memory of Er-doped TiO2 nanowire MOS capacitor. IEEE Electron Device Lett. 39(12), 1856–1859 (2018).

P. Chetri, J.C. Dhar, 2022, February. Capacitive memory using GLAD synthesized annealed SnO2 nanowires array as a dielectric. In 2022 IEEE VLSI Device Circuit and System (VLSI DCS) (pp. 139–142). https://doi.org/10.1109/VLSIDCS53788.2022.9811450

N. Miyata, J. Nara, T. Yamasaki, K. Sumita, R. Sano, H. Nohira, 2018, December. Interface dipole modulation in HfO2/SiO2 MOS stack structures. In 2018 IEEE International Electron Devices Meeting (IEDM) (pp. 7 – 6). https://doi.org/10.1109/IEDM.2018.8614674

R. Khosla, E.G. Rolseth, P. Kumar, S.S. Vadakupudhupalayam, S.K. Sharma, J. Schulze, Charge trapping analysis of metal/Al2O3/SiO2/Si, gate stack for emerging embedded memories. IEEE Trans. Device Mater. Reliab. 17(1), 80–89 (2017). https://doi.org/10.1109/TDMR.2017.2659760

S.A. Lee, S.Y. Jeong, J.Y. Hwang, J.P. Kim, M.G. Ha, C.R. Cho, Dielectric characterization of metal-oxide-semiconductor capacitor using Ga2O3 dielectrics on p-Si (100). Integr. Ferroelectr. 74(1), 173–180 (2005). https://doi.org/10.1080/10584580500414192

H. Wong, H. Iwai, On the scaling issues and high-K replacement of ultrathin gate dielectrics for nanoscale MOS transistors. Microelectron. Eng. 83(10), 1867–1904 (2006). https://doi.org/10.1016/j.mee.2006.01.271

R. Rajkumari, C. Ngangbam, N.K. Singh, Presence of capacitive memory in GLAD-synthesized WO3 nanowire. J. Mater. Sci.: Mater. Electron. 32, 3191–3200 (2021). https://doi.org/10.1007/s10854-020-05067-y

J. Zhao, Y. Tian, A. Liu, L. Song, Z. Zhao, The NiO electrode materials in electrochemical capacitor: a review. Mater. Sci. Semiconduct. Process. 96, 78–90 (2019). https://doi.org/10.1016/j.mssp.2019.02.024

J. Zhang, J. Shi, D.C. Qi, L. Chen, K.H. Zhang, Recent progress on the electronic structure, defect, and doping properties of Ga2O3. APL Mater. (2020). https://doi.org/10.1063/1.5142999

M.C. Pedapudi, J.C. Dhar, Improved UV photodetection based on β-Ga2O3-NiO 1D–1D heterostructure arrays. IEEE Sens. Lett. (2022). https://doi.org/10.1109/LSENS.2022.3225724

Y.M. Juan, H.T. Shoou-Jinn Chang, S.H. Hsueh, W.Y. Wang, T.C. Weng, Cheng, Effects of humidity and ultraviolet characteristics on β-Ga2O3 nanowire sensor. RSC Adv. 5, 8477684781 (2015). https://doi.org/10.1039/C5RA16710

M.C. Pedapudi, J.C. Dhar, A novel high performance photodetection based on axial NiO/β-Ga2O3 pn junction heterostructure nanowires array. Nanotechnology. 33(25), 255203 (2022). https://doi.org/10.1088/1361-6528/ac5b54

P. Ravikumar, D. Taparia, P. Alagarsamy, Thickness-dependent thermal oxidation of Ni into NiO thin films. J. Supercond. Novel Magn. 31, 3761–3775 (2018). https://doi.org/10.1007/s10948-018-4651-6

H. Miyata, K. Kuroda, Preferred alignment of mesochannels in a mesoporous silica film grown on a silicon (110) surface. J. Am. Chem. Soc. 121(33), 7618–7624 (1999). https://doi.org/10.1021/ja990758m

P. Nwaokafor, K.B. Okeoma, O.K. Echendu, A.C. Ohajianya, O. Kingsley, Egbo. X-ray diffraction analysis of a class of AlMgCu Alloy using Williamson–Hall and Scherrer methods. Metallogr. Microstruct. Anal. (2021). https://doi.org/10.1007/s13632-021-00792-0

J.C. Dhar, A. Mondal, N.K. Singh, P. Chinnamuthu, Low-leakage TiO2 Nanowire Dielectric MOS device using Ag Schottky Gate Contact. IEEE Trans. Nanotechnol. 12(6), 948–950 (2013). https://doi.org/10.1109/TNANO.2013.2277600

S. Alagha, A. Shik, H.E. Ruda, I. Saveliev, K.L. Kavanagh, S.P. Watkins, Space-charge-limited current in nanowires. J. Appl. Phys. (2017). https://doi.org/10.1063/1.4982222

M.C. Pedapudi, J.C. Dhar, A novel high performance photodetection based on axial NiO/β-Ga2O3 pn junction heterostructure nanowires array. Nanotechnology (2022). https://doi.org/10.1088/1361-6528/ac5b54

S. Panigrahy, J.C. Dhar, Non-volatile memory application of glancing angle deposition synthesized Er2O3 capped SnO2 nanostructures. Semicond. Sci. Technol. (2020). https://doi.org/10.1088/1361-6641/ab7b0b

P.N. Meitei, N.K. Singh, Effect of annealing on forming-free bipolar resistive switching of Gd2O3 thin films. J. Alloys Compd. 941, 168900 (2023). doi.org/10.10 16/j.jallcom.2023.168900

A. Mondal, J.C. Dhar, P. Chinnamuthu, N.K. Singh, K.K. Chattopadhyay, S.K. Das, S.C. Das, A. Bhattacharyya, Electrical properties of vertically oriented TiO2 nanowire arrays synthesized by glancing angle deposition technique. Electron. Mater. Lett. 9, 213–217 (2013). https://doi.org/10.1007/s13391-012-2136-5

B. Wu, H. Yuan, Q. Xu, J.A. Steele, D. Giovanni, P. Puech, J. Fu, Y.F. Ng, N.F. Jamaludin, A. Solanki, S. Mhaisalkar, Indirect tail states formation by thermal-induced polar fluctuations in halide perovskites. Nat. Commun. 10, 484 (2019)

V. Schmidt, J.V. Wittemann, S. Senz, U. Gösele, Silicon nanowires: a review on aspects of their growth and their electrical properties. Adv. Mater. 21(25–26), 2681–2702 (2009). https://doi.org/10.1002/adma.200803754

S. Nakazawa, T. Okuda, J. Suda, T. Nakamura, T. Kimoto, Interface properties of 4H-SiC and MOS structures annealed in NO. IEEE Trans. Electron. Devices. 62(2), 309–315 (2014). https://doi.org/10.1109/TED.2014.2352117

Z. Zhang, Y. Zeng, C.S. Jiang, Y. Huang, M. Liao, H. Tong, M. Al-Jassim, P. Gao, C. Shou, X. Zhou, B. Yan, Carrier transport through the ultrathin silicon-oxide layer in tunnel oxide passivated contact (TOPCon) c-Si solar cells. Sol. Energy Mater. Sol. Cells. 187, 113–122 (2018). https://doi.org/10.1016/j.solmat.2018.07.025

A. Nath, B.K. Mahajan, M.B. Sarkar, Ag nanoparticles sheltered In2O3 nanowire as a capacitive MOS memory device. IEEE Trans. Nanotechnol. 19, 856–863 (2020). https://doi.org/10.1109/TNANO.2020.3035179

D. Zhou, J. Xu, Q. Li, Y. Guan, F. Cao, X. Dong, J. Müller, T. Schenk, U. Schröder, Wake-up effects in Si-doped hafnium oxide ferroelectric thin films. Appl. Phys. Lett. (2013). https://doi.org/10.1063/1.4829064

C.C. Lin, Y. Kuo, Temperature effects on nanocrystalline molybdenum oxide embedded ZrHfO high-k nonvolatile memory functions. ECS J. Solid State Sci. Technol. 2(1), Q16 (2012). https://doi.org/10.1149/2.027301jss

R.K. Gupta, S. Krishnamoorthy, D.Y. Kusuma, P.S. Lee, M.P. Srinivasan, Enhancing charge-storage capacity of non-volatile memory devices using template-directed assembly of gold nanoparticles. Nanoscale. 4(7), 2296–2300 (2012). https://doi.org/10.1039/C2NR12134D

C. Zhou, P. Peng, Y. Yang, T. Ren, 2011, February. Characteristics of metal-Pb (Zr 0.53 Ti 0.47) O3-TiO2-Si capacitor for nonvolatile memory applications. In 2011 6th IEEE International Conference on Nano/Micro Engineered and Molecular Systems (pp. 134–137). https://doi.org/10.1109/NEMS.2011.6017313

S. Gandhi, L. Li, H.Y. Hui, P. Chakraborti, H. Sharma, P.M. Raj, C.P. Wong, R. Tummala, 2014, May. Nanowires-based high-density capacitors and thin film power sources in ultrathin 3D glass modules. In 2014 IEEE 64th Electronic Components and Technology Conference (ECTC) (pp. 1492–1497). https://doi.org/10.1109/ECTC.2014.6897491

H.F. Haneef, A.M. Zeidell, O.D. Jurchescu, Charge carrier traps in organic semiconductors: a review on the underlying physics and impact on electronic devices. J. Mater. Chem. C 8(3), 759–787 (2020). https://doi.org/10.1039/C9TC05695E

W. Lu, C.M. Lieber, Semiconductor nanowires. J. Phys. D: Appl. Phys. (2006). https://doi.org/10.1088/0022-3727/39/21/R01

D. Tsoukalas, From silicon to organic nanoparticle memory devices. Philos. Trans.Royal Soc. A: Math. Phys. Eng. Sci. (2009). https://doi.org/10.1098/rsta.2008.0280

C.H. Tu, T.C. Chang, P.T. Liu, H.C. Liu, S.M. Sze, C.Y. Chang, Improved memory window for Ge nanocrystals embedded in SiON layer. Appl. Phys. Lett. (2006). https://doi.org/10.1063/1.2362972

K.K. Kashyap, L.H.J. Jire, P. Chinnamuthu, A perspective study on Au-nanoparticle adorned TiO2-nanowire for non-volatile memory devices. Mater. Today Commun. 33, 104469 (2022). https://doi.org/10.1016/j.mtcomm.2022.104469

S. Kundu, D. Maurya, M. Clavel, Y. Zhou, N.N. Halder, M.K. Hudait, P. Banerji, S. Priya, Integration of lead-free ferroelectric on HfO2/Si (100) for high performance non-volatile memory applications. Sci. Rep. 5(1), 8494 (2015). https://doi.org/10.1038/srep08494

Funding

We would like to thank the SERB project (EMR/2017/00 1863), DST Govt. of India for providing fabrication facilities, NCPRE, IIT Bombay and CSIR-NEIST JORHAT for FE-SEM. And also, NIT Nagaland for XRD facility and TEQIP-III FOR funding this research.

Author information

Authors and Affiliations

Contributions

MCP involved in writing original draft, validation, formal analysis, conceptualization. JCD involved in writing, review & editing, supervision, methodology, investigation, formal analysis, conceptualization.

Corresponding author

Ethics declarations

This article does not contain any studies involving human/animals participants performed by any of the authors.

Competing interests

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Pedapudi, M.C., Dhar, J.C. Design of non-volatile capacitive memory using axial type-II heterostructure nanowires of NiO/β-Ga2O3. J Mater Sci: Mater Electron 35, 571 (2024). https://doi.org/10.1007/s10854-024-12309-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10854-024-12309-w