Abstract

The increasing demand over the higher density and smaller form factor of memory packages have become a mainstream due to the boom of artificial intelligence and 5G/6G. While form factor of memory packages moves toward smaller and thinner geometry with higher pin counts, the package overall thermal–mechanical behavior is one of a key concern due to the harsh environment of field usage. In the paper, solder joint reliability test is conducted to understand the thermal–mechanical performance between the direct chip-attach (DCA) and fan-out chip scale package (FOCSP). It is observed the overall reliability of DCA package performs better than FOCSP, which is likely because of coefficient of thermal expansion (CTE) mismatch. Inside the FOCSP structure, the results indicate that higher Cu stud height and thinner base die thickness would contribute to better reliability performance. In failure analysis, the failure modes of signal and power net inside FOCSP packages occur either at Cu RDL (Redistribution Layers) crack or IMC (Interface Metallic Compound)/solder crack. In terms of DCA package, the signal net is likely to occur slight electrical short, and the power net exhibit the IMC/solder crack near package side. In addition, the thermal interface analysis of warpage behavior between PCB and package has been studied to correlate with the solder joint reliability performance inside FOCSP case. In thermal warpage analysis of DCA package and board, when under colling stage profile, the package sits at center location exhibit more thermal stress then the edge one, shifting JFFS warpage from negative to positive value, and thus lead to earlier failure. Last, the study will list out a table to discuss the pros and cons of DCA and FOCSP package in terms of reliability, cost, and signal integrity perspective.

Similar content being viewed by others

Data availability

The datasets generated during and/or analyzed during the current study are available from the corresponding author on reasonable request.

References

R. R. Tummala, 2019 Moore’s Law for Packaging to Replace Moore’s Law for ICS," 2019 Pan Pacific Microelectronics Symposium (Pan Pacific), Kauai, HI, USA, https://doi.org/10.23919/PanPacific.2019.8696409.

J.H. Lau, Fan-Out Wafer-Level Packaging (Springer, New York, 2018)

J.H. Lau et al., Fan-Out wafer-level packaging for heterogeneous integration. IEEE Trans. Comp. Packag. Manuf. Technol. 8(9), 1544–1560 (2018). https://doi.org/10.1109/TCPMT.2018.2848649

J. A. Lim, B. -C. Kim, R. Valencia-Gacho and B. Dunlap, 2022 "Component Level Reliability Evaluation of Low Cost 6-Sided Die Protection versus Wafer Level Chip Scale Packaging with 350um Ball Pitch," 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 2022, pp. 1791-1797, doi: https://doi.org/10.1109/ECTC51906.2022.00282.

M. -C. Hsieh and S. -L. Tzeng (2014) Solder joint fatigue life prediction in large size and low cost wafer-level chip scale packages, In: 2014 15th International Conference on Electronic Packaging Technology, Chengdu, China, pp. 496–501, https://doi.org/10.1109/ICEPT.2014.6922704.

T. Henttonen, P. Mescher, D. Scott, H. Park, Y. Ko, K. Engel (2018) Board Level Reliability Study of Next Generation Large Die Wafer Level Chip Scale Package Structures. International Wafer Level Packaging Conference (IWLPC), San Jose, CA, USA pp. 1-9, doi: https://doi.org/10.23919/IWLPC.2018.8573297

Y.S. Chan, S.W.R. Lee, F. Song, C.C.J. Lo, T. Jiang, Effect of UBM and BCB layers on the thermo-mechanical reliability of wafer level chip scale package (WLCSP)," 2009 4th International Microsystems. Packaging, Assembly and Circuits Technology Conference, Taipei, Taiwan 2009, 407–410 (2009). https://doi.org/10.1109/IMPACT.2009.5382204

V. Liu et al., "Solder Joint Reliability Assessment on FO-CSP for Next Generation DDR6," 2022 IEEE 24th Electronics Packaging Technology Conference (EPTC), Singapore, Singapore, 2022, pp. 969–972, doi: https://doi.org/10.1109/EPTC56328.2022.10013142.

Lau, J.H., & Pao, Y.H. (1996). Solder Joint Reliability of BGA, CSP, Flip Chip, and Fine Pitch SMT Assemblies.

R. Arnold, “Chip scale package versus direct chip attach (CSP vs. DCA),”, Proceedings. 50th Electronic Components and Technology Conference (Cat. No.00CH37070). Las Vegas, NV, USA 2000, 822–828 (2000). https://doi.org/10.1109/ECTC.2000.853256

J. H. Lau, "Electronics Packaging Technology Update: BGA, CSP, DCA, And Flip Chip," IEMT/IMC Symposium, 1st [Joint International Electronic Manufacturing Symposium and the International Microelectronics Conference], Tokyo, Japan, 1997, pp. 32–36, doi: https://doi.org/10.1108/03056129710370277.

Guotao Wang, P. S. Ho and S. Groothuis, "Packaging effect on reliability of Cu/low k interconnects," 2004 IEEE Workshop on Microelectronics and Electron Devices, 2004, pp. 28–30, doi: https://doi.org/10.1109/WMED.2004.1297342.

Z. -J. Wu et al., "Chip-Package Interaction Challenges for Large Die Applications," 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), 2018, pp. 656–662, doi: https://doi.org/10.1109/ECTC.2018.00104.

Z.-J. Wu, M. Nayini, C. Carey, S. Donovan, D. Questad, E. Blackshear, CPI Reliability Challenges of Large Flip Chip Packages and Effects of Kerf Size and Substrate. IEEE International Reliability Physics Symposium (IRPS) 2019, 1–7 (2019). https://doi.org/10.1109/IRPS.2019.8720530

K. Hu, C. P. Yeh, B. Doot, A. F. Skipor and K. W. Wyatt, "Die cracking in flip chip on board assembly", Proc. 45th Electron. Compon. Technol. Conf., pp. 293–299, 1995-May.

T. Xu, Z. -J. Wu, H. Zhang, C. Graas and P. Justison, "Die Edge Crack Propagation Modeling for Risk Assessment of Advanced Technology Nodes," 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), 2018, pp. 2260–2266, doi: https://doi.org/10.1109/ECTC.2018.00340.

T. Henttonen, P. Mescher, D. Scott, H. Park, Y. Ko, K. Engel, Board Level Reliability Study of Next Generation Large Die Wafer Level Chip Scale Package Structures. International Wafer Level Packaging Conference (IWLPC) 2018, 1–9 (2018). https://doi.org/10.23919/IWLPC.2018.8573297

S. Raghavan, I. Schmadlak, G. Leal, S.K. Sitaraman, Study of Chip-Package Interaction Parameters on Interlayer Dielectric Crack Propagation. IEEE Trans. Device Mater. Reliab. 14(1), 57–65 (2014). https://doi.org/10.1109/TDMR.2013.2288255

Z.-J. Wu, H. Zhang, J. Malinowski, Understanding and Improving Reliability for Wafer Level Chip Scale Package: A Study Based on 45nm RFSOI Technology for 5G Applications. IEEE Journal of the Electron Devices Society 8, 1305–1314 (2020). https://doi.org/10.1109/JEDS.2020.3023007

S. Lip Teng, M. Devarajan, “Thermo-Mechanical Reworkable Epoxy Underfill in Board-Level Package: Material Characteristics and Reliability Criteria,”, IEEE 72nd Electronic Components and Technology Conference (ECTC). San Diego, CA, USA 2022, 1750–1753 (2022). https://doi.org/10.1109/ECTC51906.2022.00275

D. Yong, L. Chunchao, Z. Peiqiang, Z. Bingjie, L. zilian and Z. zhanping, "Reliability evaluation and selection of underfill adhesives," 2019 20th International Conference on Electronic Packaging Technology(ICEPT), Hong Kong, China, 2019, pp. 1–4, doi: https://doi.org/10.1109/ICEPT47577.2019.245256.

“JESD22-B112, “ Thermal Shadow Moire Method,“ JEDEC, May 2005 [Online]

IPC-9701A, Performance Test Methods and Qualifications Requirements for Surface Mount Solder Attachments.

“JESD22-A104-B, “ Temperature Cycling,“ JEDEC, July 2000 [Online]

“IPC-SM-785, “ Guidelines for Accelerated Reliability Testing of Surface Mount Solder Attachments,“ IPC, November 1992 [Online].

I.C. Wu, M.H. Wang, L.S. Jang, (2018), “Experimental location of damage in microelectronic solder joints after a board level reliability evaluation.” Engineering Failure Analysis, Elsevier 83(October), 131–140 (2017)

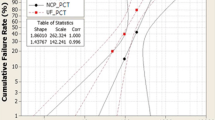

W. Nelson, Weibull analysis of reliability data with few or no failures. J. Qual. Technol. 17, 140–146 (1985)

N. Enkhmunkh, Gwang Won Kim, Kab-Ju Hwang and Seung-Ho Hyun, “A parameter estimation of Weibull distribution for reliability assessment with limited failure data,.” International Forum on Strategic Technology 2007, 39–42 (2007). https://doi.org/10.1109/IFOST.2007.4798514

Gwang Won Kim 'A Study on the'Substation Reliability Assessment Using Weibull Distribution,' Trans. of KIEE, vol. SIA, no.I, pp.7–14, January 2002.

W. Li, Incorporating Aging Failures in Power System Reliability Assessment Evaluation. IEEE Trans. on Power Systems 17(3), 918–923 (2002)

M. Motalab, Z. Cai, J. C. Suhling and P. Lall, "Determination of Anand constants for SAC solders using stress-strain or creep data," 13th InterSociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, San Diego, CA, USA, 2012, pp. 910–922, doi: https://doi.org/10.1109/ITHERM.2012.6231522.

M. R. Chowdhury, S. Ahmed, A. Fahim, J. C. Suhling and P. Lall, "Mechanical characterization of doped SAC solder materials at high temperature," 2016 15th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), Las Vegas, NV, USA, 2016, pp. 1202–1208, doi: https://doi.org/10.1109/ITHERM.2016.7517684.

A. Syed, "Accumulated creep strain and energy density based thermal fatigue life prediction models for SnAgCu solder joints," 2004 Proceedings. 54th Electronic Components and Technology Conference (IEEE Cat. No.04CH37546), Las Vegas, NV, USA, 2004, pp. 737–746 Vol.1, doi: https://doi.org/10.1109/ECTC.2004.1319419.

H. Hamdani, A. El Hami, B. Radi, "Reliability Analsyis based on Metamodels of Chip-Scale Packages (CSP)," Embedded Mechatronic System 2, ISTE, pp. 247–271, 2020, doi: https://doi.org/10.1016/B978-1-78548-190-1.50009-8.

Y.Y. Chen, W.J. Liu, Y.S. Zou, M.H. Chung, C.L. Gan, H. Takiar, “Fault Isolation for Board-Level Solder Joint Failure Using Time-Domain Reflectometry,”, IEEE 24th Electronics Packaging Technology Conference (EPTC). Singapore, Singapore 2022, 795–798 (2022). https://doi.org/10.1109/EPTC56328.2022.10013229

M. K. Chen, C. C. Tai, Y. J. Huang and I. C. Wu, "Failure analysis of BGA package by a TDR approach", Proc 4 th International Symposium on Electronic Materials and Packaging , pp. 112–116, Dec. 2002.

C. Zhong et al., "Interface StressAnalysis Based on Warpage Characterization in a Flip-Chip Package," 2022 23rd International Conference on Electronic Packaging Technology (ICEPT), Dalian, China, 2022, pp. 1–6, doi: https://doi.org/10.1109/ICEPT56209.2022.9873419.

K. Chiavone, "Analyzing package-on-package (PoP) reflow assembly interfaces with interconnect gap analysis," 36th International Electronics Manufacturing Technology Conference, Johor, Malaysia, 2014, pp. 1–6, doi: https://doi.org/10.1109/IEMT.2014.7123136.

I. Ho, P.-Y. Liao, T. Shih, A. Kang, Y.-P. Wang, “Package Warpage of Whole Strip Evaluation with Interface Analysis in the Flip-Chip Die Bonding Process,”, IEEE 73rd Electronic Components and Technology Conference (ECTC). Orlando, FL, USA 2023, 923–928 (2023). https://doi.org/10.1109/ECTC51909.2023.00158

W. Yu, “Substrate Copper Trace Crack Characterization and Simulation,”, et al., IEEE 73rd Electronic Components and Technology Conference (ECTC). Orlando, FL, USA 2023, 699–705 (2023). https://doi.org/10.1109/ECTC51909.2023.00122

A. Deshpande, I. Olatunji, M. Bascolo, A. Dasgupta, U. Becker and J. Gabor, "Copper Trace Failures in Ball Grid Array (BGA) Packages under Sequential Harmonic Vibration and Temperature Cycling," 2022 21st IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (iTherm), San Diego, CA, USA, 2022, pp. 1–5, doi: https://doi.org/10.1109/iTherm54085.2022.9899525.

Gan, C.L., Huang, CY. (2023). Advanced Flip Chip Packaging. In: Interconnect Reliability in Advanced Memory Device Packaging. Springer Series in Reliability Engineering. Springer, Cham. https://doi.org/10.1007/978-3-031-26708-6_4

Gan, C.L., Huang, CY. (2023). Reliability Simulation and Modeling in Memory Packaging. In: Interconnect Reliability in Advanced Memory Device Packaging. Springer Series in Reliability Engineering. Springer, Cham. https://doi.org/10.1007/978-3-031-26708-6_7

Acknowledgements

Despite multiple challenges in the progress of this project, the author would like to pay sincere gratefulness to all PDE members, Micron Technology Inc., who make this project possible.

Funding

Micron Technology, 0000443159, Vance Liu

Author information

Authors and Affiliations

Contributions

All authors whose names appear on the submission made substantial contributions to the conception or design of the work, analysis, interpretation of data, drafted the work, and revised it critically for important intellectual content. All authors approve the version to be published and agree to be accountable for all aspects of the work in ensuring that questions related to the accuracy or integrity of any part of the work are appropriately investigated and resolved.

Corresponding authors

Ethics declarations

Conflict of interest

Vance Liu reports financial support was provided by Micron Technology Inc. Vance Liu reports a relationship with Micron Technology Inc. that includes employment and funding grants. Author and co-authors are all currently employed in Micron Technology Inc.

Research involving human participants and/or animals

The work has not involved with any human participants nor animals.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Liu, V., Sinha, K., Chen, CT. et al. Comparative study of solder joint reliability assessment on fan-out CSP and flip-chip DCA package. J Mater Sci: Mater Electron 34, 2130 (2023). https://doi.org/10.1007/s10854-023-11546-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10854-023-11546-9