Abstract

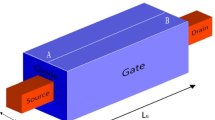

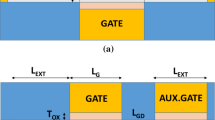

This paper describes a junctionless double-gate FET at nanoscale dimensions that utilizes a ß-Ga2O3 packet to improve and amend the electric field at the device's beginning and in the channel. The fundamental concept behind this design is to place a ß-Ga2O3 packet at the intersection of the source and channel devices. The distribution of the electric field inside the device is amended and the peak of the electric field in the channel area is altered as a result of the characteristics of the ß-Ga2O3 material. Additionally, the electric field's modification has lowered the structure's temperature and improved the carrier's mobility. Also, the performance of the proposed device exhibits an improvement in the short-channel effect. The use of this packet has a significant impact on the device's performance, improving both AC and DC properties in the proposed device. The proposed device's simulation results demonstrate a significant improvement in the features of the lattice temperature, electron mobility, leakage current, hole concentration, drain-induced barrier lowering (DIBL), and subthreshold slope. Additionally, compared to a conventional structure, the AC properties, such as noise and unilateral power gain, as well as the sum of the gate-source and gate-drain capacitors, showed a considerable improvement.

Similar content being viewed by others

Availability of data and materials

The data that support the findings of this study are available from the authors, upon reasonable request.

References

S.A. Bozorgi, A.A. Orouji, A. Abbasi, A novel nanoscale SOI MOSFET by using a P-N junction and an electrically hole free region to improve the electrical characteristics. SILICON 14, 5905–5912 (2022). https://doi.org/10.1007/s12633-021-01304-z

M.K. Anvarifard, A.A. Orouji, Proper electrostatic modulation of electric field in a reliable nano-SOI with a developed channel. IEEE Trans Electron Devices 65, 1653–1657 (2018). https://doi.org/10.1109/TED.2018.2808687

A. Naderi, F. Heirani, A novel SOI-MESFET with symmetrical oxide boxes at both sides of gate and extended drift region into the buried oxide. AEU - Int J Electron Commun 85, 91–98 (2018). https://doi.org/10.1016/j.aeue.2018.01.001

S.K. Gupta, Threshold voltage model of junctionless cylindrical surrounding gate MOSFETs including fringing field effects. Superlattices Microstruct 88, 188–197 (2015). https://doi.org/10.1016/j.spmi.2015.09.001

A. Nandi, N. Pandey, Accurate analytical modeling of junctionless DG-MOSFET by green’s function approach. Superlattices Microstruct 111, 983–990 (2017). https://doi.org/10.1016/j.spmi.2017.07.062

A. Abbasi, A.A. Orouji, A silicon/indium arsenide source structure to suppress the parasitic bipolar-induced breakdown effect in SOI MOSFETs. Mater Sci Semicond Process 16, 1821–1827 (2013). https://doi.org/10.1016/j.mssp.2013.06.022

A. Naderi, K.M. Satari, F. Heirani, SOI-MESFET with a layer of metal in buried oxide and a layer of SiO2 in channel to improve RF and breakdown characteristics. Mater Sci Semicond Process 88, 57–64 (2018). https://doi.org/10.1016/j.mssp.2018.07.035

M.K. Anvarifard, A nanoscale-modified junctionless with considerable progress on the electrical and thermal issue. Int J Numer Model Electron Networks, Devices Fields (2019). https://doi.org/10.1002/jnm.2537

I. Ferain, C.A. Colinge, J.P. Colinge, Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. Nature 479, 310–316 (2011)

S.K. Gupta, A.S. Rawat, Y.K. Verma, V. Mishra, Linearity distortion analysis of junctionless quadruple gate MOSFETs for analog applications. SILICON 11, 257–265 (2019). https://doi.org/10.1007/s12633-018-9850-z

F. Jazaeri, L. Barbut, A. Koukab, J.M. Sallese, Analytical model for ultra-thin body junctionless symmetric double gate MOSFETs in subthreshold regime. Solid State Electron 82, 103–110 (2013). https://doi.org/10.1016/j.sse.2013.02.001

V. Kumari, N. Modi, M. Saxena, M. Gupta, Modeling and simulation of Double Gate Junctionless Transistor considering fringing field effects. Solid State Electron 107, 20–29 (2015). https://doi.org/10.1016/j.sse.2015.01.020

D. Roy, A. Biswas, Analytical model of nanoscale junctionless transistors towards controlling of short channel effects through source/drain underlap and channel thickness engineering. Superlattices Microstruct 113, 71–81 (2018). https://doi.org/10.1016/j.spmi.2017.09.056

H. Zhou, K. Maize, G. Qiu et al., β-Ga 2 O 3 on insulator field-effect transistors with drain currents exceeding 1.5 A/mm and their self-heating effect. Appl Phys Lett 111, 92102 (2017). https://doi.org/10.1063/1.5000735

J. Oh, J. Ma, G. Yoo, Simulation study of reduced self-heating in β-Ga2O3 MOSFET on a nano-crystalline diamond substrate. Results Phys 13, 102151 (2019). https://doi.org/10.1016/j.rinp.2019.02.087

K.J. Liddy, A.J. Green, N.S. Hendricks et al., Thin channel β-Ga 2 O 3 MOSFETs with self-aligned refractory metal gates. Appl Phys Express 12, 126501 (2019). https://doi.org/10.7567/1882-0786/ab4d1c

H.N. Masten, J.D. Phillips, R.L. Peterson, Ternary alloy rare-earth scandate as dielectric for β-Ga 2 O 3 MOS Structures. IEEE Trans Electron Devices 66, 2489–2495 (2019). https://doi.org/10.1109/TED.2019.2911237

D. Madadi, A.A. Orouji, New high-voltage and high-speed β-Ga2O3 MESFET with amended electric field distribution by an insulator layer. Eur Phys J Plus (2020). https://doi.org/10.1140/epjp/s13360-020-00523-4

Z. Ramezani, A.A. Orouji, A silicon-on-insulator metal-semiconductor field-effect transistor with an L-shaped buried oxide for high output-power density. Mater Sci Semicond Process 19, 124–129 (2014). https://doi.org/10.1016/j.mssp.2013.11.011

M.D. Santia, N. Tandon, J.D. Albrecht, Supplementary Material for : Lattice Thermal Conductivity in β-Ga2O3 from first principles. Appl Phys Lett 107, 1–7 (2015)

Z. Guo, A. Verma, X. Wu et al., Anisotropic thermal conductivity in single crystal β-gallium oxide. Appl Phys Lett (2015). https://doi.org/10.1063/1.4916078

H. He, R. Orlando, M.A. Blanco et al., First-principles study of the structural, electronic, and optical properties of Ga2 O3 in its monoclinic and hexagonal phases. Phys Rev B - Condens Matter Mater Phys (2006). https://doi.org/10.1103/PhysRevB.74.195123

M. Higashiwaki, K. Sasaki, A. Kuramata et al., Gallium oxide ( Ga2O3) metal-semiconductor field-effect transistors. Appl Phys Lett 100, 13504 (2012)

K. Sasaki, M. Higashiwaki, A. Kuramata et al., Ga2 O3 schottky barrier diodes fabricated by using single-crystal β-Ga2 O3 (010) substrates. IEEE Electron Device Lett 34, 493–495 (2013). https://doi.org/10.1109/LED.2013.2244057

E.G. Villora, K. Shimamura, Y. Yoshikawa et al., Large-size β-Ga2O3 single crystals and wafers. J Cryst Growth 270, 420–426 (2004). https://doi.org/10.1016/j.jcrysgro.2004.06.027

H. Aida, K. Nishiguchi, H. Takeda et al., Growth of β-Ga2O3 single crystals by the edge-defined, film fed growth method. Jpn J Appl Phys 47, 8506–8509 (2008). https://doi.org/10.1143/JJAP.47.8506

Y. Tomm, P. Reiche, D. Klimm, T. Fukuda, Czochralski grown Ga2O3 crystals. J Cryst Growth 220, 510–514 (2000). https://doi.org/10.1016/S0022-0248(00)00851-4

M. Higashiwaki, K. Sasaki, T. Kamimura et al., Depletion-mode Ga2O3 metal-oxide-semiconductor field-effect transistors on β-Ga2O3 (010) substrates and temperature dependence of their device characteristics. Appl Phys Lett. (2013). https://doi.org/10.1063/1.4821858

K. Zeng, A. Vaidya, U. Singisetti, A field-plated Ga2O3 MOSFET with near 2-kV breakdown voltage and 520 mΩ • cm2 on-resistance. Appl Phys Express (2019). https://doi.org/10.7567/1882-0786/ab2e86

D. Madadi, A.A. Orouji, Investigation of Short Channel Effects in SOI MOSFET with 20 nm Channel Length by a β-Ga 2 O 3 Layer. ECS J Solid State Sci Technol 9, 45002 (2020). https://doi.org/10.1149/2162-8777/ab878b

J. Ma, H.J. Cho, J. Heo et al., Asymmetric Double-Gate β-Ga 2 O 3 Nanomembrane Field-Effect Transistor for Energy-Efficient Power Devices. Adv Electron Mater 5, 1800938 (2019). https://doi.org/10.1002/aelm.201800938

N. Makeswaran, D. Das, V. Zade et al., Size- and phase-controlled nanometer-thick β-Ga2O3 films with green photoluminescence for optoelectronic applications. ACS Appl Nano Mater 4, 3331–3338 (2021). https://doi.org/10.1021/acsanm.1c00378

Sze SM, Ng KK (2007) Physics of Semiconductor Devices. In: SM Sze, KK Ng (eds). Phys Semicond Devices. 3rd Ed, John Wiley Sons, Inc., NJ 164, 682

N.B. Bousari, M.K. Anvarifard, S. Haji-Nasiri, Improving the electrical characteristics of nanoscale triple-gate junctionless FinFET using gate oxide engineering. AEU - Int J Electron Commun 108, 226–234 (2019). https://doi.org/10.1016/j.aeue.2019.06.017

S.A. Bozorgi, A.A. Orouji, High performance nanoscale SOI MOSFET with enhanced gate control. Micro Nanostruct 175, 207523 (2023). https://doi.org/10.1016/j.micrna.2023.207523

Y. Wang, Y. Tang, L.L. Sun, F. Cao, High performance of junctionless MOSFET with asymmetric gate. Superlattices Microstruct 97, 8–14 (2016). https://doi.org/10.1016/j.spmi.2016.06.003

S. Barraud, M. Berthome, R. Coquand et al., Scaling of trigate junctionless nanowire MOSFET with gate length down to 13 nm. IEEE Electron Device Lett 33, 1225–1227 (2012). https://doi.org/10.1109/LED.2012.2203091

D. Madadi, A.A. Orouji, Investigation of tied double gate 4H–SiC junctionless FET in 7 nm channel length with a symmetrical dual p+ layer. Phys E Low-Dimensional Syst Nanostructures (2021). https://doi.org/10.1016/j.physe.2020.114450

V. Pathak, G. Saini, A Graded Channel Dual-Material Gate Junctionless MOSFET for Analog Applications. Procedia Comput Sci 125, 825–831 (2018). https://doi.org/10.1016/j.procs.2017.12.105

Acknowledgements

Not applicable

Funding

The authors received no financial support for the research, authorship, and/or publication of this article.

Author information

Authors and Affiliations

Contributions

M. Heidari contributed to conceptualization, writing—original draft, and software. A. A. Orouji contributed to supervision—review & editing. S. A. Bozorgi contributed to validation, review & editing.

Corresponding author

Ethics declarations

Conflict of interests

The authors declare that they have no conflict of interest.

Ethics approval and consent to participate

Not applicable.

Consent for publication

Not applicable.

Research involving human participants and/or animals

Not applicable.

Informed consent

Not applicable.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Heidari, M., Orouji, A.A. & Bozorgi, S.A. A nanoscale junctionless FET to amend the electric field distribution using a β-Ga2O3 packet. J Mater Sci: Mater Electron 34, 1708 (2023). https://doi.org/10.1007/s10854-023-11104-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10854-023-11104-3