Abstract

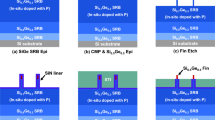

In this paper, shallow trench isolation (STI) liner layer skipping and channel passivation engineering for the SiGe channel FinFET device are investigated in detail. First, to skip the STI liner layer and simplify the integration process, an optimized rapid thermal annealing (RTA) STI densification annealing of 850 °C for 30 s in N2 ambient is developed. And a high quality and thermal stable SiGe fin under STI last strategy can be successfully prepared. Then, combined with the stacked HfO2/Al2O3 gate dielectric, the SiGe film is directly ozone passivated at 300 °C for 30 min to improve its interface quality. As a result, a low interface state density of 4.8 × 1012 eV−1 cm−2 @ E − Ev = 0.33 eV is achieved. Finally, a SiGe channel FinFET device is successfully fabricated utilizing these newly developed processes. In particular, compared with unoptimized SiGe FinFET device, its subthreshold slope can be improved from 149 to 89 mV/dec, which is a key index for the high-quality SiGe fin with improved interface quality. The above results confirm that the STI liner skipping engineering with an optimized RTA STI dentification annealing and the channel passivation engineering can be practicable technologies for the SiGe FinFET device.

Similar content being viewed by others

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

C. H. Lee, S. Mochizuki, R. G. Southwick, J. Li, X. Miao, R. Bao, T. Ando, R. Galatage, S. Siddiqui, C. Labelle, A. Knorr, J. H. Stathis, D. Guo, V. Narayanan, B. Haran, and H. Jagannathan 2017 International Electron Devices Meeting, December 2–6, 2017, San Francisco, CA, USA, p.820

P. Nguyen, S. Barraud, C. Tabone, L. Gaben, M. Cassé, F. Glowacki, J.-M. Hartmann, M.-P. Samson, V. Maffini-Alvaro, C. Vizioz, N. Bernier, C. Guedj, C. Mounet, O. Rozeau, A. Toffoli, F. Alain, D. Delprat, B.-Y. Nguyen, C. Mazuré, O. Faynot, and M. Vinet, 2014 International Electron Devices Meeting, December 15–17, 2014, San Francisco, CA, USA, p.406

Pouya Hashemi, Karthik Balakrishnan, Sebastian U. Engelmann, John A. Ott, Ali Khakifirooz, Ashish Baraskar, Marinus Hopstaken, Joseph S. Newbury, Kevin K. Chan, Effendi Leobandung, Renee T. Mo, and Dae-Gyu Park, 2014 International Electron Devices Meeting, December 15–17, 2014, San Francisco, CA, USA, p.402

H. Mertens, R. Ritzenthaler, H. Arimura, J. Franco, F. Sebaai, A. Hikavyy, B. J. Pawlak, V. Machkaoutsan, K. Devriendt, D. Tsvetanova, A. P. Milenin, L. Witters, A. Dangol, E. Vancoille, H. Bender, M. Badaroglu, F. Holsteyns, K. Barla, D. Mocuta, N. Horiguchi, and A.V-Y Thean, 2015 IEEE Symposium on VLSI Technology, June 16–18, 2015, Kyoto, Japan, p.142

H. Mertens, R. Ritzenthaler, A. Hikavyy, J. Franco, J. W. Lee, D. P. Brunco, G. Eneman, L. Witters, J. Mitard, S. Kubicek, K. Devriendt, D. Tsvetanova, A. P. Milenin, C. Vrancken, J. Geypen, H. Bender, G. Groeseneken, W. Vandervorst, K. Barla, N. Collaert, N. Horiguchi, and A.V-Y Thean, 2014 IEEE Symposium on VLSI Technology, June 9–12, 2014, Honolulu, HI, USA

Z. Zhao, Y. Li, G. Wang, Du. Anyan, Y. Li, Q. Zhang, Xu. Gaobo, Y. Zhang, J. Luo, JunFeng Li, W. Wang, Semicond. Sci. Technol. 34, 125008 (2019)

D. Guo, G. Karve, G. Tsutsui, K-Y Lim, R. Robison, T. Hook, R. Vega, D. Liu, S. Bedell, S. Mochizuki, F. Lie, K. Akarvardar, M. Wang, R. Bao, S. Burns, V. Chan, K. Cheng, J. Demarest, J. Fronheiser, P. Hashemi, J. Kelly, J. Li, N. Loubet, P. Montanini, B. Sahu, M. Sankarapandian, S. Sieg, J. Sporre, J. Strane, R. Southwick, N. Tripathi, R. Venigalla, J. Wang, K. Watanabe, C. W. Yeung, D. Gupta, B. Doris, N. Felix, A. Jacob, H. Jagannathan, S. Kanakasabapathy, R. Mo, V. Narayanan, D. Sadana, P. Oldiges, J. Stathis, T. Yamashita, V. Paruchuri, M. Colburn, A. Knorr, R. Divakaruni, H. Bu, and M. Khare, 2016 IEEE Symposium on VLSI Technology, June 14–16, 2016, Honolulu, HI, USA

W.L. Lee, C.Y. Yu, J.L. Zhang, G.L. Luo, C.H. Chien, IEEE Electron. Device Lett. 40, 678 (2019)

N. Loubet, T. Hook, P. Montanini, C.-W. Yeung, S. Kanakasabapathy, M. Guillom, T. Yamashita, J. Zhang, X. Miao, J. Wang, A. Young, R. Chao, M. Kang, Z. Liu, S. Fan, B. Hamieh, S. Sieg, Y. Mignot, W. Xu, S.-C. Seo, J. Yoo, S. Mochizuki, M. Sankarapandian, O. Kwon, A. Carr, A. Greene, Y. Park, J. Frougier, R. Galatage, R. Bao, J. Shearer, R. Conti, H. Song, D. Lee, D. Kong, Y. Xu, A. Arceo, Z. Bi, P. Xu, R. Muthinti, J. Li, R. Wong, D. Brown, P. Oldiges, R. Robison, J. Arnold, N. Felix, S. Skordas, J. Gaudiello, T. Standaert, H. Jagannathan, D. Corliss, M.-H. Na, A. Knorr, T. Wu, D. Gupta, S. Lian, R. Divakaruni, T. Gow, C. Labelle, S. Lee, V. Paruchuri, H. Bu, and M. Khare, 2017 IEEE Symposium on VLSI Technology, June 5–8, 2017, Kyoto, Japan, p.230

Jungwoo Oh, Prashant Majhi, Raj Jammy, Raymond Joe, Anthony Dip, Takuya Sugawara, Yasushi Akasaka, Takanobu Kaitsuka, Tsunetoshi Arikado, and Masayuki Tomoyasu, 2009 International Symposium on VLSI Technology, Systems, and Applications, April 27–29, 2009, Hsinchu, Taiwan, p.22

Ashish Kumar, Wen Hsi Lee, Y.L. Wang, IEEE Trans. Semicond. Manuf. 34, 177 (2021)

X. Cheng, Y. Li, G. Wang, H. Liu, Y. Zan, H. Lin, Z. Kong, Z. Zhong, Y. Li, H. Wang, Xu. Gaobo, X. Ma, X. Wang, H. Yang, J. Luo, W. Wang, Semicond. Sci. Technol. 35, 115008 (2020)

X. Ma, L. Zhou, J. Xiang, H. Yang, X. Wang, Y. Li, J. Zhang, C. Zhao, H. Yin, W. Wang, T. Ye, Appl. Surf. Sci. 493, 478 (2019)

R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka, and S. Takagi, 2011 IEEE Symposium on VLSI Technology, June 14–16, 2011, Kyoto, Japan, p.56

Y. Li, F. Zhao, X. Cheng, H. Liu, Y. Zan, J. Li, Q. Zhang, Wu. Zhenhua, J. Luo, W. Wang, Nanomaterials 11, 1689 (2021)

Acknowledgements

This work is supported by the Beijing Municipal Natural Science Foundation (Grant no. 4202078).

Funding

Beijing Municipal Natural Science Foundation, 4202078, Yongliang Li

Author information

Authors and Affiliations

Contributions

Conceptualization, methodology, and formal analysis: CL and YL, validation: FZ, writing—original draft preparation: CL and AC, writing—review and editing, JL and WW. All authors have read and agreed to the published version of the manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors maintain that they have no conflict of interest to be described in this communication.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Li, C., Li, Y., Chen, A. et al. SiGe Fin field effect transistor (FET) with STI liner skipping and channel passivation engineering. J Mater Sci: Mater Electron 34, 520 (2023). https://doi.org/10.1007/s10854-023-09945-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10854-023-09945-z