Abstract

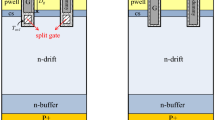

In this study, an insulated gate bipolar transistor (IGBT) with three-layer poly gate is proposed and investigated by TCAD simulation. Here, gate is spilt in two different workfunction materials of N+ poly (\(\phi _{g}\)= 4.17 eV) and P+ poly (\(\phi _{g}\)= 5.25 eV). Lower workfunction poly layer is sandwiched between higher workfunction poly, connected via a single metal. The gate oxide thickness is varied in x-direction. This leads to improvement in transconductance and reduction in miller capacitance. Thin oxide near the emitter serves good control over the charge carriers in the channel. This deployment of dual material gate in proposed device results in 36% reduction in area-specific on-resistance without any degradation in breakdown voltage. In addition to this, proposed device exhibits improved transient characteristics with 18.5% and 60% reduction in turn-off time and delay, respectively, as compared to conventional device. Further, the turn-off energy loss is reduced by 23.5% and 29.09% reduction in on-state voltage drop is achieved. Furthermore, proposed device offers 23%, 58%, and 30% improvement in FOM1, Baliga figure of merit (BFOM), and FOM2, respectively.

Similar content being viewed by others

References

B.J. Baliga, Fundamentals of Power Semiconductor Devices (Springer Science & Business Media, New York, 2010)

F.J. Niedernostheide, H.J. Schulze, T. Laska, A. Philippou, IET Power Electron. 11(4), 646 (2018)

W. Chen, J. Cheng, H. Huang, B. Zhang, X.B. Chen, IEEE Trans. Electron Devices 66(8), 3690 (2019)

K. Ohi, Y. Ikura, A. Yoshimoto, K. Sugimura, Y. Onozawa, H. Takahashi, M. Otsuki, In: 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD) (IEEE, 2015), pp. 25–28

A. Elsayed, J.F. Dick, J. Schulze, In: 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD) (IEEE, 2019), pp. 343–346

M. Antoniou, N. Lophitis, F. Udrea, F. Bauer, U.R. Vemulapati, U. Badstuebner, IEEE Electron Device Lett. 38(8), 1063 (2017)

M. Vaidya, A. Naugarhiya, S. Verma, Semicond. Sci. Technol. 35(2), 025015 (2020). https://doi.org/10.1088/1361-6641/ab6106

N. Gupta, A. Naugarhiya, Silicon pp. 1–10 (2020)

R. Sithanandam, M.J. Kumar, Semicond. Sci. Technol. 25(1), 015006 (2009)

R.S. Saxena, M.J. Kumar, IEEE Trans. Electron Devices 56(6), 1355 (2009). https://doi.org/10.1109/TED.2009.2019371

P. Nautiyal, A. Naugarhiya, S. Verma, Semicond. Sci. Technol. 34(9), 095016 (2019). https://doi.org/10.1088/1361-6641/ab337f

T. Laska, M. Munzer, F. Pfirsch, C. Schaeffer, T. Schmidt, In: 12th International Symposium on Power Semiconductor Devices & ICs. Proceedings (Cat. No. 00CH37094) (IEEE, 2000), pp. 355–358

K.H. Oh, J. Lee, K.H. Lee, Y.C. Kim, C. Yun, IEEE Trans. Electron Devices 53(4), 884 (2006)

B.J. Baliga, M.S. Adler, R.P. Love, P.V. Gray, N.D. Zommer, IEEE Trans. Electron Devices 31(6), 821 (1984). https://doi.org/10.1109/T-ED.1984.21614

K.Y. Na, Y.S. Kim, Jpn. J. Appl. Phys. 45(12), 9033 (2006)

I. Silvaco, Santa Clara, CA. Ver 5, (2011)

K. Nadda, M.J. Kumar, Sci. Rep. 5, 7860 (2015)

J. Huang, H. Huang, X. Lyu, X.B. Chen, IEEE Trans. Electron Devices 65(12), 5545 (2018)

F.D. Bauer, Solid-State Electron. 48(5), 705 (2004)

R.S. Saxena, M.J. Kumar, IEEE Trans. Electron Devices 56(3), 517 (2009). https://doi.org/10.1109/TED.2008.2011723

M.J. Kumar, R. Sithanandam, IEEE Trans. Electron Devices 57(7), 1719 (2010). https://doi.org/10.1109/TED.2010.2049209

A.P.S. Hsieh, G. Camuso, F. Udrea, C. Ng, Y. Tang, R.K. Vytla, N. Ranjan, A. Charles, In: 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD) (IEEE, 2015), pp. 137–140. https://doi.org/10.1109/ISPSD.2015.7123408

J.F. Donlon, E.R. Motto, T. Takahashi, H. Fujii, K. Satoh, In: 2008 IEEE Industry Applications Society Annual Meeting (IEEE, 2008), pp. 1–7. https://doi.org/10.1109/08IAS.2008.368

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gupta, N., Singh, S. & Naugarhiya, A. An insulated gate bipolar transistor with three-layer poly gate for improved figure of merit. J Mater Sci: Mater Electron 31, 15513–15521 (2020). https://doi.org/10.1007/s10854-020-04113-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-020-04113-z