Abstract

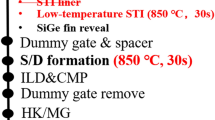

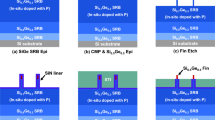

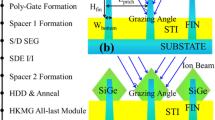

In this work, SiGe Fin formation technique using shallow trench isolation (STI) first or STI last strategy for the high mobility channel FinFET device is systematically investigated. A 20 nm width and 35 nm height high crystalline quality of the Si0.7Ge0.3 Fin formation for STI first scheme is demonstrated by utilizing a new developed Si Fin etching, Si Fin recess and SiGe selective epitaxial growth process. For the STI last strategy, a novel chemical mechanical planarization (CMP) treated three-layer SiGe strain relaxed buffer (SRB) is successfully fabricated and a 50 nm high crystal quality and atomically smooth surface Si0.5Ge0.5 layer on this SRB is attained. Moreover, a spike annealing is employed to avoid the Si0.5Ge0.5 Fin oxidation during STI densification with an acceptable STI etching rate. However, both a spike annealing and a lower temperature of traditional furnace at 850 °C or 750 °C suffer micro-trench issue during the Fin reveal process. Therefore, a new developed process, named as STI recess first, is developed to resolve both thermal instability and micro-trench issue at the same time. A minor Si0.5Ge0.5 Fin loss with a sharp Si0.7Ge0.3 SRB/Si0.5Ge0.5 interfaces for STI last scheme is realized by utilizing this new developed STI recess first process.

Similar content being viewed by others

References

L. Witters, H. Arimura, F. Sebaai, A. Hikavyy, A.P. Milenin, R. Loo et al., Strained germanium gate-all-around pMOS device demonstration using selective wire release etch prior to replacement metal gate deposition. IEEE Trans. Electron. Dev. 64(11), 4587 (2017)

H. Mertens, R. Ritzenthaler, H. Arimura, J. Franco, F. Sebaai, A. Hikavyy, et al., Si-cap-free SiGe p-Channel FinFETs and Gate-All-Around Transistors in a Replacement Metal Gate Process: Interface Trap Density Reduction and Performance Improvement by High-Pressure Deuterium Anneal, in VLSI Technology (2015) Symposium on, pp. T142–T143

M.L. Huang, S.W. Chang, M.K. Chen, Y. Oniki, H.C. Chen, C.H. Lin, et al., High performance In0.53Ga0.47As FinFETs fabricated on 300 mm Si substrate, in Proceedings of IEEE Symposium on VLSI Technology (2016), pp. 1–2

D. Guo, G. Karve, G. Tsutsui, K.-Y. Lim, R. Robison, T. Hook, et al., FINFET Technology Featuring High Mobility SiGe Channel for 10 nm and Beyond, in Proceedings of Symposium on VLSI Technology (2016), pp. 1–2

L. Witters, J. Mitard, R. Loo, S. Demuynck, S.A. Chew, T. Schram, et al., Strained germanium quantum well p-FinFETs fabricated on 45 nm Fin pitch using replacement channel, replacement metal gate and germanide-free local interconnect, in Symposium on VLSI Technology (2015), pp. T56–T57

L. Witters, J. Mitard, R. Loo, G. Eneman, H. Mertens, D.P. Brunco, et al., Strained Germanium Quantum Well pMOS FinFETs Fabricated on in situ Phosphorus-Doped SiGe Strain Relaxed Buffer Layers Using a Replacement Fin Process, in IEEE International Electron Devices Meeting (2013). pp. 534-537

J. Mitard, L. Witters, R. Loo, S.H. Lee, J.W. Sun, J. Franco, et al., 15 nm-WFIN High-Performance Low-Defectivity Strained-Germanium pFinFETs With Low Temperature STI-Last Process, in Proceedings of Symposium on VLSI Technology (2014), pp. 1–2

A.V. de Oliveira, E. Simoen, P.G. Der Agopian, J.A. Martino, J. Mitard, et al., Impact of the low temperature operation on long channel strained Ge pFinFETs fabricated with STI first and last processes, in IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (2016), pp. 1-3

R. Pillarisetty, B. Chu-Kung, S. Corcoran, G. Dewey, J. Kavalieros, H. Kennel, et al., High mobility strained germanium quantum well field effect transistor as the p-channel device option for low power (Vcc = 0.5 V) III–V CMOS architecture, in IEEE International Electron Devices Meeting (2010). pp. 150–153

M. Myronov, X.-C. Liu, A. Dobbie, D.R. Leadley, Control of epilayer thickness during epitaxial growth of high Ge content strained Ge/SiGe multilayers by RP-CVD. J. Cryst. Growth. 318(1), 337 (2011)

Z. Zhao, Y. Li, S. Gu, Q. Zhang, G. Wang, J. Li et al., High crystal quality strained Si0.5Ge0.5 layer with a thickness of up to 50 nm grown on the three-layer SiGe strain relaxed buffer. Mater. Sci. Semicond. Process. 99, 159 (2019)

R. Loo, A.Y. Hikavyy, L. Witters, A. Schulze, H. Arimura, D. Cott et al., Processing technologies for advanced Ge devices electronic materials and processing. ECS J. Solid State Sci. Technol. 6(1), 14 (2017)

Z. Zhao, Y. Li, G. Wang, A. Du, S. Gu, Y. Li et al., A novel three-layer graded SiGe strain relaxed bufer for the high crystal quality and strained Si0.5Ge0.5 layer epitaxial grown. J. Mater. Sci.: Mater. Electron. 30(15), 14130 (2019)

Acknowledgments

This work is supported in part by CAS Pioneer Hundred Talents Program, in part by the National Key Project of Science and Technology of China (Grant No. 2017ZX02315001-002), and in part by the Foundation of President of the Institute of Microelectronics, Chinese Academy of Sciences (Grant No. Y9SR02X001).

Author information

Authors and Affiliations

Corresponding authors

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Zhao, Z., Cheng, X., Li, Y. et al. Investigation on the formation technique of SiGe Fin for the high mobility channel FinFET device. J Mater Sci: Mater Electron 31, 5854–5860 (2020). https://doi.org/10.1007/s10854-019-02661-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-019-02661-7