Abstract

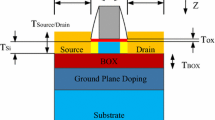

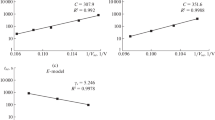

The drain current (ID) transients by switching the biasing condition are examined in FD-SOI MOSFETs with negative biased back gate voltage (VBG). Special attention is paid to the influence of the gate-induced charge/discharge of the floating body on the ID transient. The ID transient appears not only by switching the front gate voltage (VFG) but also by switching VBG. It is also shown that the analysis of a small VFG step transient is useful to examine the lifetime under different bias conditions. All the results can be explained by the transitional change of ID − VFG characteristics at different body-charge conditions.

Similar content being viewed by others

References

T. Skotnicki, G. Merckel, A. Merrachi, in IEDM Technical Digest, (1989), p. 87

M.V. Fischetti, S.E. Laux, in IEDM Technical Digest, (1995), p. 305

A. Mercha, J.M. Rafí, E. Simoen, E. Augendre, C. Claeys, IEEE Trans. on Electron Devices, 50(7), 1675 (2003)

J. Pretet, T. Matsumoto, T. Poiroux, S. Cristoloveanu, R. Gwoziecki, C. Raynaud, A. Roveda, H. Brut, Proc. of ESSDERC (Italy, Sept., 2002), pp. 515–518

K. Hayama, H. Ohyama, J.M. Rafí, A. Mercha, E. Simoen, C. Claeys, Proc. of ULIS 2004 (Leuven, Belgium, 2004), pp. 59–62

J.M. Rafí, A. Mercha, E. Simoen, C. Claeys, Solid-State Electronics, 48(7), 1211 (2004)

D.E. Ioannou, S. Cristoloveanu, M. Mukherjee, B. Mazhari, IEEE Electron Device Lett. 11(9), 409 (1990)

Acknowledgement

This work was partially supported by the Ministry of Education, Culture, Sports, Science and Technology of Japan for Young Scientists (B) 16760051, 2006.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Hayama, K., Takakura, K., Ohyama, H. et al. Carrier lifetime analysis in thin gate oxide FD-SOI n-MOSFETs by gate-induced drain current transients. J Mater Sci: Mater Electron 19, 161–165 (2008). https://doi.org/10.1007/s10854-007-9301-x

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-007-9301-x