Abstract

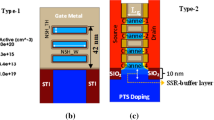

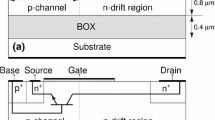

A new lateral bipolar junction transistor that utilises a double-polysilicon self-aligned structure to maximise high-frequency performance is introduced. Silicon-on-oxide (SOI) wafers are used to isolate devices from the substrate and to minimise parasitic substrate capacitances (CJCS0) around 1.3–2.6 fF (substrate is ground). A SOI thickness of 0.2–0.5 μm combined with 0.13–0.25 μm lithography could allow a reduction of transistor dimensions down to (0.2–0.5) × (0.13–0.25) μm2 and give an estimated minimum emitter/base junction capacitance (CJE0) of 0.54–1.36 fF. Simple device isolation is predicted to produce a small collector/base junction capacitance (CJC0) of 0.42–2.00 fF. Furthermore, use of a double base contact can help reduce base resistance (RB) to 0.43–1.17 kΩ and a wide collector window directly contacted to the collector is estimated to result in around 0.66–1.58 kΩ collector resistance (RC). By taking all parameters into account a cut-off frequency (f T ) of 69–116 GHz and maximum oscillation frequency (fmax) of 61–128 GHz is predicted for this design, in addition a gain of 47–101 (using minimum gain enhancement) and roughly 10.6–21.0 ps ECL propagation delay time, at a current of 0.4–1.0 mA could be achieved. Our simulations indicate that this new doubled-polysilicon self-aligned structure could outperform all other silicon bipolar transistors that have been reported.

Similar content being viewed by others

References

A.J. Joseph et al., Proc. IEEE 93(9), 1539 (2005)

I.-S.M. Sun et al., Electron Devices, IEEE Trans., 52, 1376 (2005)

I.-S.M. Sun et al., Silicon Monolithic Integration Circuits in RF System, 2006 Topical Meeting, January 2006

D.J. Roulston, Bipolar Semiconductor Devices (McGraw Hill, 1990) p. 239

P. Ashburn, SiGe Heterojunction Bipolar Transistors. (John Wiley & Sons Ltd, 2003) pp. 111–112, 72–75

W. Fang, IEEE Jnl Solid State Circuits, (1990)

H. Nii et al., Solid-State Device Research Conference, 1999. Proceeding of the 29th European , 13–15 September 1999, vol. 1, pp. 212–215

P. Pengpad et al., 5th International Conference Materials for Microelectronics and Nanoengineering, 13–14 September 2004, University of Southampton, Southampton, UK

J.S. Rieh et al., Electron Devices Meeting, 2002, IEDM 2002. Digest International, 8–11 Dec. 2002

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Pengpad, P., Bagnall, D.M. Double-polysilicon self-aligned lateral bipolar transistors. J Mater Sci: Mater Electron 19, 183–187 (2008). https://doi.org/10.1007/s10854-007-9300-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-007-9300-y