Abstract

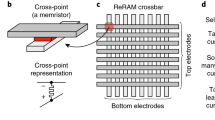

Resistive random-access memory (ReRAM) has several attractive features such as high storage density and high switching frequency with low power consumption. It is hence regarded as the most promising nonvolatile memory material. However, a memristor, which is a primitive component of the ReRAM-based memory, has much lower write endurance. Hence, an error-correcting code (ECC) circuit is indispensable for realizing reliable ReRAM storage. Accordingly, we propose a hybrid CMOS/memristor-based ECC circuit. In the proposed circuit, the blocks with high-frequency write operations are implemented using the conventional CMOS technology and the other blocks are implemented using the memristors to maintain a balance between the area overhead and reliability. Through numerical experiments, we demonstrate that the proposed ECC circuit achieves smaller area and higher reliability than the full memristor-based ECC circuits and achieves much smaller area while preserving the reliability compared with the full CMOS-based ECC circuits.

Similar content being viewed by others

References

Adhikari SP, Yang C, Kim H, Chua L (2012) Memristor bridge synapse-based neural network and its learning. IEEE Trans Neural Netw Learn Syst 23(9):1426–1435

Cai Y, Lin Y, Xia L, Chen X, Han S, Wang Y, Yang H (2018) Long live TIME: improving lifetime for training-in-memory engines by structured gradient sparsification. In: Proceedings of the IEEE/ACM design automation conference, pp 1–6

Chaudhuri A, Yan B, Chen Y, Chakrabarty K (2019) Hardware fault tolerance for binary RRAM crossbars. In: Proceedings of the IEEE international test conference, p 4.3

Chen CY, Shih HC, Wu CW, Lin CH, Chiu PF, Sheu SS, Chen FT (2015) RRAM Defect modeling and failure analysis based on march test and a novel squeeze-search scheme. IEEE Trans Comput 64 (3):180–190

Chua L (1971) Memristor—the missing circuit element. IEEE Trans Circuit Theory 18(5):507–519

Chua L (2011) Resistance switching memories are memristors. Applied Phys A 102:765–783

Das P, Saw SK, Meher P (2019) Design of differential amplifier using current mirror load in 90 nm CMOS technology. In: Information systems design and intelligent applications. Springer, pp 421–429

Dong X, Xu C, Xie Y, Jouppi NP (2012) NVSIm: a circuit-level performance, energy, and area model for emerging nonvolatile memory. IEEE Trans Comput-Aided Des Integr Circuits Syst 31(7):994–1007

Goldman R, Bartleson K, Wood T, Kranen K, Cao C, Melikyan V, Markosyan G (2009) Synopsys’ open educational design kit: Capabilities, deployment and future. In: Proceedings of the IEEE international conference on microelectronic systems education, pp 20–24

Grossi A, Zambelli C, Olivo P, Nowak E, Molas G, Nodin JF, Perniola L (2017) Cell-to-cell fundamental variability limits investigation in oxrram arrays. IEEE Electron Device Lett 39(1):27–30

Gupta I, Serb A, Khiat A, Zeitler R, Vassanelli S, Prodromakis T (2016) Real-time encoding and compression of neuronal spikes by metal-oxide memristors. Nat Commun 7(12805):1–9

Ishizaka M, Shintani M, Inoue M (2018) Area-efficient and reliable hybrid CMOS/memristor ECC circuit for reRAM storage. In: Proceedings of the IEEE asian test symposium, pp 167–172

Kumar UK, Umashankar BS (2007) Improved hamming code for error detection and correction. In: Proceedings of the IEEE international symposium on wireless pervasive computing, pp 498–500

Kvatinsky S, Satat G, Wald N, Friedman EG, Kolodny A, Weiser UC (2014) Memristor-based material implication (IMPLY) logic: Design principles and methodologies. IEEE Trans Very Large Scale Integr (VLSI) Syst 22(10):2054–2066

Liu M, Xia L, Wang Y, Chakrabarty K (2019) Fault tolerance in neuromorphic computing systems. In: Proceedings of the IEEE/ACM asia and south pacific design automation conference, pp 216–223

Merolla P, Arthur J, Akopyan F, Imam N, Manohar R, Modha DS (2011) A digital neurosynaptic core using embedded crossbar memory with 45pJ per spike in 45nm. In: Proceedings of the IEEE custom integrated circuits conference, pp 1–4

Merolla PA, Arthur JV, Alvarez-Icaza R, Cassidy AS, Sawada J, Akopyan F, Jackson BL, Imam N, Guo C, Nakamura Y, Brezzo B, Vo I, Esser SK, Appuswamy R, Taba B, Amir A, Flickner MD, Risk WP, Manohar R, Modha DS (2014) A million spiking-neuron integrated circuit with a scalable communication network and interface. Science 345(6147):668–673

Niu D, Xiao Y, Xie Y (2012) Low power memristor-based reRAM design with error correcting code. In: Proceedings of the IEEE/ACM asia and south pacific design automation conference, pp 79–84

Pouyan P, Amat E, Rubio A (2018) Memristive crossbar memory lifetime evaluation and reconfiguration strategies. IEEE Trans Emerg Topics Comput 6(2):207–218

Qazi M, Stawiasz K, Chang L, Chandrakasan AP (2011) A 512kb 8T SRAM macro operating down to 0.57V with an AC-coupled sense amplifier and embedded data-retention-voltage sensor in 45nm SOI CMOS. IEEE J Solid-State Circuits 46(1):85–96

Raghuvanshi A, Perkowski M (2014) Logic synthesis and a generalized notation for memristor-realized material implication gates. In: Proceedings of the IEEE/ACM international conference on computer-aided design, pp 470–477

Reuben J, Ben-Hur R, Wald N, Talati N, Ali AH, Gaillardon PE, Kvatinsky S (2017) Memristive logic: a framework for evaluation and comparison. In: Proceedings of the international symposium on power and timing modeling, optimization and simulation, pp 1–8

Serb A, Papavassiliou C, Prodromakis T (2017) A memristor-CMOS hybrid architecture concept for on-line template matching. In: Proceedings of the IEEE international symposium on circuits and systems, pp 1–4

Sheu SS, Chang MF, Lin KF, Wu CW, Chen YS, Chiu PF, Kuo CC, Yang YS, Chiang PC, Lin WP, et al. (2011) A 4mb embedded slc resistive-ram macro with 7.2 ns read-write random-access time and 160ns mlc-access capability. In: Digest of technical papers of the IEEE international solid-state circuits conference, pp 200–0202

Strukov DB, Snider GS, Stewart DR, Williams RS (2008) The missing memristor found. Nature 453:80–83

Suzuki K, Swanson S (2015) A survey of trends in non-volatile memory technologies: 2000-2014. In: Proceedings of the IEEE international memory workshop, pp 1–4

(2013) Synopsys, Inc.: Design Compiler User Guide Version I-2013.06

Xia L, Huangfu W, Tang T, Yin X, Chakrabarty K, Xie Y, Wang Y, Yang H (2018) Stuck-at fault tolerance in RRAM computing systems. IEEE Trans Comput-Aided Des Integr Circuits Syst 8 (1):102–115

Xia L, Liu M, Ning X, Chakrabarty K, Wang Y (2017) Fault-tolerant training with on-line fault detection for RRAM-based neural computing systems. In: Proceedings of the IEEE/ACM design automation conference, pp 33:1–33:6

Yang JJ, Strukov DB, Stewart DR (2013) Memristive devices for computing. Nat Nanotechnol 8:13–24

Acknowledgements

This work was partially supported by JSPS KAKENHI Grant No. 18K18025.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: K. Chakrabarty

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Ishizaka, M., Shintani, M. & Inoue, M. Area-Efficient and Reliable Error Correcting Code Circuit Based on Hybrid CMOS/Memristor Circuit. J Electron Test 36, 537–546 (2020). https://doi.org/10.1007/s10836-020-05892-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-020-05892-3