Abstract

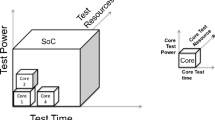

The cost of testing SOCs (systems-on-chip) is highly related to the test application time. The problem is that the test application time increases as the technology makes it possible to design highly complex chips. These complex chips include a high number of fault sites, which need a high test data volume for testing, and the high test data volume leads to long test application times. For modular core-based SOCs where each module has its distinct tests, concurrent application of the tests can reduce the test application time dramatically, as compared to sequential application. However, when concurrent testing is used, resource conflicts and constraints must be considered. In this paper, we propose a test scheduling technique with the objective to minimize the test application time while considering multiple conflicts. The conflicts we are considering are due to cross-core testing (testing of interconnections between cores), module testing with multiple test sets, hierarchical conflicts in SOCs where cores are embedded in cores, the sharing of the TAM (test access mechanism), test power limitations, and precedence conflicts where the order in which tests are applied is important. These conflicts must be considered in order to design a test schedule that can be used in practice. In particular, the limitation on the test power consumption is important to consider since exceeding the system's power limit might damage the system. We have implemented a technique to integrate the wrapper design algorithm with the test scheduling algorithm, while taking into account all the above constraints. Extensive experiments on the ITC'02 benchmarks show that even though we consider a high number of constraints, our technique produces results that are in the range of results produced be techniques where the constraints are not taken into account.

Similar content being viewed by others

References

R.M. Chou, K.K. Saluja, and V.D. Agrawal, “Scheduling Tests for VLSI Systems Under Power Constraints,” IEEE Transactions on VLSI Systems, vol. 5, no. 2, pp. 175–185, 1997.

E. Cota, L. Cairo, M. Lubaszewski, and A. Orailoglu, “Test Planning and Design Space Exploration in a Core-based Environment,” in Proceedings of the Design, Automation and Test in Europe Conference (DATE), Paris, France, 2002, pp. 478–485.

H-S Hsu, J-R Huang, K-L Cheng, C-W Wang, C-T Huang, and C-W Wu, “Test Scheduling and Test Access Architecture Optimization for System-on-Chip,” in Proceedings of IEEE Asian Test Symposium (ATS), Tamuning, Guam, USA, 2002, pp. 411–416.

Y. Huang, S.M. Reddy, W-T Cheng, P. Reuter, N. Mukherjee, C-C Tsai, O. Samman, and Y. Zaidan, “Optimal core wrapper width selection and SOC test scheduling based on 3-D bin packing algorithm,” in Proceedings IEEE of International Test Conference (ITC), Baltimore, MD, USA, 2002, pp. 74–82.

V. Iyengar, K. Chakrabarty, and E.J. Marinissen, “Test Wrapper and Test Access Mechanism Co-Optimization for System-on-Chip,” Journal of Electronic Testing; Theory and Applications (JETTA), pp. 213–230, 2002.

V. Iyengar K. Chakrabarty, and E.J. Marinissen, “Efficient Wrapper/TAM Co-Optimization for Large SOCs,” in Proceedings of Design and Test in Europe (DATE), Paris, France, 2002, pp. 491–498.

V. Iyengar, K. Chakrabarty, and E.J. Marinissen, “On Using Rectangle Packing for SOC Wrapper/TAM Co-Optimization,” in Proceedings of IEEE VLSI Test Symposium (VTS), Monterey, California, USA, 2002, pp. 253–258.

V. Iyengar, S.K. Goel, E.J. Marinissen, and K. Chakrabarty, “Test Resource Optimization for Multi-Site Testing of SOCs under ATE Memory Depth Constraints,” in Proceedings of IEEE International Test Conference, Baltimore, MD, USA, 2002, pp. 1159–1168.

V. Iyengar, K. Chakrabarty, M.D. Krasniewski, and G.N. Kuma, “Design and Optimization of Multi-level TAM Architectures for Hierarchical SOCs,” in Proceedings of IEEE VLSI Test Symposium (VTS), 2003, pp. 299–304.

S.K. Goel and E.J. Marinissen, “Cluster-Based Test Architecture Design for System-On-Chip,” in Proceedings of IEEE VLSI Test Symposium (VTS), Monterey, California, USA, 2002, pp. 259–264.

S.K. Goel and E.J. Marinissen, “Effective and efficient test architecture design for SOCs,” in Proceedings of IEEE International Test Conference (ITC), Baltimore, MD, USA, 2002, pp. 529–538.

S. Koranne, “On Test Scheduling for Core-based. SOCs,” in Proceedings of International Conference on VLSI Design, Bangalore, India, 2002, pp 505–510.

S. Koranne and V. Iyengar, “On the use of k - tuples for SoC test schedule representation,” in Proceedings of International Test Conference (ITC), Baltimore, MD, USA, 2002, pp. 539–548.

E.J. Marinissen, R. Kapur, and Y. Zorian, “On Using IEEE P1500 SECT for Test Plug-n-play,” in Proceedings of IEEE International Test Conference (ITC), Atlantic City, NJ, USA, 2000, pp. 770–777.

J. Pouget, E. Larsson, Z. Peng, M.-L. Flottes, and B. Rouzeyre, “An Efficient Approach to SoC Wrapper Design, TAM configuration, and Test Scheduling,” in Proceedings of IEEE European Test Workshop (ETW), Maastricht, The Nederlands, 2003, pp. 117-122.

J. Pouget, E. Larsson, and Z. Peng, “SOC Test Time Minimization Under Multiple Constraints,” in Proceedings of Asian Test Symposium (ATS), Xian, China, 2003, pp. 312–317.

Author information

Authors and Affiliations

Corresponding author

Additional information

The research is partially supported by the Swedish National Program on Socware. An earlier version of the paper has been presented at the Asian Test Symposium (ATS), 2003 [16].

Julien Pouget received his M.Sc degree and PhD degree from Montpellier University, LIRMM, France, in 1999 and 2002, respectively. He was a guest researcher at Embedded Systems Laboratory, Linköpings Universitet, Sweden, from September 2002 to October 2003, and during 2004 he was an assistant professor at ISIM, The Microelectronic Engineering School, Montpellier, France. Currently, he is a DFT engineer at ST Microelectronics, Grenoble, France. His main research interest is on system-on-chip test scheduling and test architecture co-optimization.

Erik Larsson received his M.Sc., Tech. Lic and Ph.D from Linköping University in 1994, 1998, 2000, respectively. From October 2001 to December 2002 he was at a Japan Society for the Promotion of Science (JSPS) funded Post Doc position at the Computer Design and Test Laboratory at Nara Institute of Science and Technology (NAIST), Nara, Japan. Currently, he is Assistant Professor and Director of Studies of the Division for Software and Systems at the Department of Computer and Information Science, Linköpings Universitet, Sweden.

His current research interests include the development of tools and design for testability methodologies to facilitate the testing of complex digital systems. The main focuses are on system-on-chip test scheduling and test infrastructure design.

He is author of the book “Introduction to Advanced System-on-Chip Test Design and Optimization” (Springer 2005) and is co-guest editor for the IEE Computers & Digital Techniques special issue on “Resource-Constrained Testing of System Chips”. He received the best paper award for the paper “Integrated Test Scheduling, Test Parallelization and TAM Design” at IEEE Asian Test Symposium (ATS), 2002, and he has supervised the thesis, which was selected as the best thesis by Föreningen Svenskt Näringsliv, 2002, and the thesis, which was selected as the best thesis at the Department of Computer Science, 2004.

He is a member of the program committee of Design and Test Automation in Europe (DATE), 2004, 2005, 2006, IEEE Workshop on Design and Diagnostics of Electronic Circuits and Systems (DDECS), 2004, 2005, 2006, and The Workshop on RTL ATPG & DFT (WRTLT), 2005, 2006.

Zebo Peng received the B.Sc. degree in Computer Engineering from the South China Institute of Technology, China, in 1982, and the Licentiate of Engineering and Ph.D. degrees in Computer Science from Linköping University, Sweden, in 1985 and 1987, respectively.

Currently, he is Professor of Computer Systems, Director of the Embedded Systems Laboratory, and Chairman of the Division for Software and Systems in the Department of Computer Science, Linköping University. His research interests include design and test of embedded systems, electronic design automation, SoC testing, design for testability, hardware/software co-design, and real-time systems. He has published over 180 technical papers in these areas and co-authored the books “System Synthesis with VHDL” (Boston: Kluwer, 1997), “Analysis and Synthesis of Distributed Real-Time Embedded Systems” (Boston: Kluwer, 2004), and “System-level Test and Validation of Hardware/Software Systems” (London: Springer, 2005).

Prof. Peng was co-recipient of four best paper awards, two at the European Design Automation Conferences (EURO-DAC'92 and EURO-DAC'94), one at the IEEE Asian Test Symposium (ATS'02), and one at the Design, Automation and Test in Europe Conference (DATE'05), as well as a best presentation award at the IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis (2003). He has served on the program committee of a dozen international conferences and workshops, including ATS, ASP-DAC, DATE, DDECS, DFT, ETS, ITSW, MEMOCDE and VLSI-SOC. He was the General Chair of the 6th IEEE European Test Workshop (ETW'01), the Program Chair of the 7th IEEE Design & Diagnostics of Electronic Circuits & Systems Workshop (DDECS'04), and the Test Track Chair of the 2006 Design Automation and Test in Europe Conference (DATE'06). He is the Vice-Chair of the IEEE European Test Technology Technical Council (ETTTC).

Rights and permissions

About this article

Cite this article

Pouget, J., Larsson, E. & Peng, Z. Multiple-Constraint Driven System-on-Chip Test Time Optimization. J Electron Test 21, 599–611 (2005). https://doi.org/10.1007/s10836-005-2911-4

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/s10836-005-2911-4