Abstract

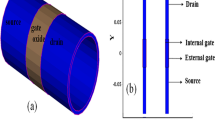

Tunnel field-effect transistors (TFETs) have been explored extensively as a possible substitute for MOSFETs, especially for digital system design applications. Unlike conventional MOSFET devices, TFETs exhibit certain unique characteristics which are suitable for energy-efficient digital system design. In this paper, we report the use of a single device with both terminals biased independently for basic two-input Boolean logic operations AND, OR, NAND, and NOR using technology computer-aided design (TCAD) simulations. It is shown that these basic Boolean operations can be realized by minimally altering the design of a double-gate vertical TFET (DGVTFET) device and by selecting the appropriate device characteristics. The results show that when the Boolean functions are implemented, the ION/IOFF ratio is in the range of 109 to 1013 at a supply voltage VDD = 1 V. Simulation results show that the use of a gate–source overlap technique and the selection of a suitable silicon body thickness are vital to obtaining distinct logic functions using a DGVTFET.

Similar content being viewed by others

Data availability

Enquiries about data availability should be directed to the authors.

References

Hurst, S.L.: VLSI Custom Microelectronics: Digital: Analog, and Mixed-Signal. CRC Press, Cambridge (1998)

SIA et al.: International Technology Roadmap for Semiconductors, (2003)

Mano, M.M., Michael, C.: Digital design: with an introduction to the Verilog HDL. Pearson, London (2013)

Joshi, M., Dutt, A., Tiwari, S., Nigam, P., Beohar, A., Mathew, R.: Impact of channel splitting on gate all around tunnel field effect transistor (GAA-TFET). Devices Integr. Circuit (DevIC) 2021, 1–5 (2021)

Beohar, A., Vishvakarma, S.K.: Performance enhancement of asymmetrical underlap 3D-cylindrical GAA-TFET with low spacer width. IET Micro Nano Lett. 11(8), 443–445 (2016)

Dutt, A., Tiwari, S., Upadhyay, A.K., Mathew, R., Beohar, A.: Impact of drain underlap and high bandgap strip on cylindrical gate all around tunnel FET and its influence on analog/RF performance. Silicon 14(15), 9789–9796 (2022). https://doi.org/10.1007/s12633-022-01692-w

Tiwari, S., Dutt, A., Joshi, M., Nigam, P., Beohar, A., Mathew, R.: In-silico investigation of Cyl. Gate all around (GAA) tunnel field effect transistor (TFET) biosensor. IOP Conf. Ser.: Mater. Sci. Eng. 1166(1), 012045 (2021). https://doi.org/10.1088/1757-899X/1166/1/012045

Sanjana, T., Dutt, A., Joshi, M., Nigam, P., Mathew, R., Beohar, A.: An investigation of a suppressed-drain cylindrical gate-all-around retrograde-doped heterospacer steep-density-film tunneling field-effect transistor. J. Comput. Electron. 20(5), 1702–1710 (2021)

Frank, D.J., Dennard, R.H., Nowak, E., Solomon, P.M., Taur, Y., Wong, H.-S.P.: Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 89(3), 259–288 (2001). https://doi.org/10.1109/5.915374

The International Technology Roadmap for Semiconductors (ITRS), (2006). [Online]. Available: http://public.itrs.net

Horowitz, M., Alon, E., Patil, D., Naffziger, S., Kumar, R., Bernstein, K.: Scaling, power, and the future of CMOS." Technical Digest. IEEE International Electron Devices Meeting, pp. 9–15. (2005)

Cheung, K. P.: On the 60 mV/dec @300 K limit for MOSFET subthreshold swing. In: Proceedings of 2010 International Symposium on VLSI Technology, System and Application, Hsinchu, pp. 72–73. (2010)

Choi, W.Y., Park, B., Lee, J.D., Liu, T.K.: Tunneling field-effect transistors (TFETs) With subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007). https://doi.org/10.1109/LED.2007.901273

Khatami, Y., Banerjee, K.: Steep subthreshold slope n- and p-Type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Trans. Electron Devices 56(11), 2752–2761 (2009). https://doi.org/10.1109/TED.2009.2030831

Mukundrajan, R., Cotter, M., Saripalli, V., Irwin, M. J., Datta, S., and Narayanan, V: Ultra Low Power Circuit Design Using Tunnel FETs. In IEEE Computer Society Annual Symposium on VLSI, Amherst, MA, pp. 153–158. (2012). https://doi.org/10.1109/ISVLSI.2012.70

Datta, S., Bijesh, R., Liu, H., Mohata, D., and Narayanan, V.: Tunnel transistors for low power logic. In: IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Monterey, CA, pp.1–4. (2013)

Saurabh, S., Kumar, M.J.: Fundamentals of Tunnel Field-Effect Transistors. CRC Press, Boca Raton (2016)

Chiang, M.-H., Kim, K., Chuang, C.-T., Tretz, C.: High-density reduced-stack logic circuit techniques using independent-gate controlled double-gate devices. IEEE Trans. Electron Devices 53(9), 2370–2377 (2006). https://doi.org/10.1109/TED.2006.881052

Datta, A., Goel, A., Cakici, R.T., Mahmoodi, H., Lekshmanan, D., Roy, K.: Modeling and circuit synthesis for independently controlled double gate FinFET devices. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 26(11), 1957–1966 (2007). https://doi.org/10.1109/TCAD.2007.896320

Marchi, M.D., et al.: Configurable logic gates using polarity-controlled silicon nanowire gate-all-around FETs. IEEE Electron Device Lett. 35(8), 880–882 (2014). https://doi.org/10.1109/LED.2014.2329919

Simon, M. et al.: A wired-AND transistor: polarity controllable FET with multiple inputs. In 2018 76th Device Research Conference (DRC), Santa Barbara, CA, USA, pp. 1–2. (2018). https://doi.org/10.1109/DRC.2018.8442159

Veloso, A., et al.: Nanowire nanosheet FETs for ultra-scaled, high-density logic and memory applications. Solid State Electron. 168, 107736 (2019). https://doi.org/10.1016/j.sse.2019.107736

Amat, E., del Moral, A., Soler, V., Bausells, J., and Perez-Murano, F.: Exploring the suitability of stacking devices in a vertical nanowire to implement a CMOS inverter. In IEEE NANO’22, (2022)

Banerjee, S., Garg, S., Saurabh, S.: Realizing logic functions using single double-gate tunnel FETs: a simulation study. IEEE Electron Device Lett. 39(5), 773–776 (2018)

Garg, S., Saurabh, S.: Implementing logic functions using independently-controlled gate in double-gate tunnel FETs: investigation and analysis. IEEE Access 7, 117591–117599 (2019)

Garg, S., Saurabh, S.: Implementation of Boolean functions using tunnel field-effect transistors. IEEE J. Explor. Solid-State Comput. Devices Circuits 6(2), 146–154 (2020). https://doi.org/10.1109/JXCDC.2020.3038073

Singh, S., Khosla, M., Wadhwa, G., Raj, B.: Design and analysis of double-gate junctionless vertical TFET for gas sensing applications. Appl. Phys. A 127, 1–7 (2021)

Paras, N., Chauhan, S.S.: A novel vertical tunneling based Ge-source TFET with enhanced DC and RF characteristics for prospect low power applications. Microelectron. Eng. 217, 111103 (2019)

Chappa, V.K., Yadav, A.K., Deka, A., Khosla, R.: Investigating the effects of doping gradient, trap charges, and temperature on Ge vertical TFET for low power switching and analog applications. Mater. Sci. Eng., B 299, 116996 (2024)

Silvaco: Atlas user’s manual. (2015). [Online]. Available: http://www.silvaco.com

Beohar, A., Yadav, N., Vishvakarma, S.K.: Analysis of trap-assisted tunnelling in asymmetrical underlap 3D-cylindrical GAA-TFET based on hetero-spacer engineering for improved device reliability. Micro Nano Lett. 12(12), 982–986 (2017)

Vandooren, A., Leonelli, D., Rooyackers, R., et al.: Analysis of trap-assisted tunneling in vertical Si homo-junction and SiGe hetero-junction Tunnel-FETs. Solid-State Electron. 83, 50–55 (2013)

Acharya, A., Solanki, A.B., Glass, S., Zhao, Q.T., Anand, B.: Impact of gate-source overlap on the device/circuit analog performance of line TFETs. IEEE Trans. Electron Devices 66(9), 4081–4086 (2019). https://doi.org/10.1109/ted.2019.2927001

Liu, K.-M., Cheng, C.-P.: Investigation on the effects of gate-source overlap/underlap and source doping gradient of n-type Si cylindrical gate-all-around tunnel field-effect transistors. IEEE Trans. Nanotechnol. 19, 382–389 (2020). https://doi.org/10.1109/tnano.2020.2991787

Bernasconi, A., Berti, A., Ciriani, V., Del Corso, G.M., Fulginiti, I.: XOR-AND-XOR logic forms for autosymmetric functions and applications to quantum computing. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 42(6), 1861–1872 (2023). https://doi.org/10.1109/TCAD.2022.3213214

Bernasconi, A., et al.: Multiplicative complexity of XOR based regular functions. IEEE Trans. Comput. 71(11), 2927–2939 (2022)

Banerjee, S., Garg, S., Saurabh, S.: Realizing logic functions using single double-gate tunnel FETs: a simulation study. IEEE Electron Device Lett. 39(5), 773–776 (2018)

Funding

The authors would like to acknowledge the SERB TARE GRANT Project no. TAR/2022/000406, Govt. of India, and VIT Bhopal University, Kothrikalan, Sehore-466114, for technical and financial support.

Author information

Authors and Affiliations

Contributions

Ribu, Ankur, and Jyotirmoy conceptualized the idea and implemented the study using simulation. Ribu, Abhishek, and Pallabi wrote the paper.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Mathew, R., Beohar, A., Ghosh, J. et al. Implementation of a Boolean function with a double-gate vertical TFET (DGVTFET) using numerical simulations. J Comput Electron 23, 525–532 (2024). https://doi.org/10.1007/s10825-024-02170-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-024-02170-9