Abstract

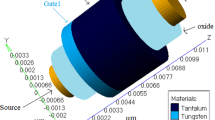

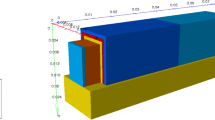

We have developed a simple physics-based two-dimensional analytical off-state breakdown voltage model of a partial buried oxide step structure (PBOSS) silicon-on-insulator laterally diffused metal oxide semiconductor (SOI-LDMOS) transistor. The analytical model includes the expressions of surface potential and electric field distributions in the drift region by solving the 2D Poisson equation. The electric field at the Si–SiO2 surface is modulated by additional electric field peaks developed due to the presence of the PBOSS structure. The uniformly distributed electric field results in improved breakdown voltage. Further, the breakdown voltage is analytically obtained by means of the critical electric field concept, to determine the breakdown characteristics. The model reveals the impact of the critical device design parameters such as thickness and length of the PBOSS structure, doping, and thickness of the drift region on the surface electric field and the breakdown voltage. The proposed model is verified by ATLAS two-dimensional simulations. The analytical model will be useful to design high-voltage SOI-LDMOS transistors for power switching applications.

Similar content being viewed by others

References

NG Wright, K. Vasilevskiy, (2020) Historical Introduction to Silicon Carbide Discovery, Properties and Technology, Advancing Silicon Carbide Electronics Technology II: Core Technologies of Silicon Carbide Device Processing, Materials Research Forum LLC, 69

Mitrovic, I., et al.: Monolithic integration design of GaN-based power chip including gate driver for high-temperature DC-DC converters. Jpn. J. Appl. Phys. 58(5), 056505 (2019)

Chowdhury, S., Swenson, B.L., Wong, M.H., Mishra, U.K.: Current status and scope of gallium nitride-based vertical transistors for high-power electronics application. Semiconductor Sci. Technol. 28(7), 074014 (2013)

Wang, Y., Chen, X., Dong, P.: Improvement of electrostatic discharge current-handling capability for high-voltage multi-finger nLDMOS devices with self-triggered technique. Semiconduct. Sci. Technol. 35, 065010 (2020)

Shu, L., Zhao, Y.F., Galloway, K.F., Wang, L., Wang, X.S., Yuan, Z.Y., Zhou, X., Chen, W.P., Qiao, M., Wang, T.Q.: Effect of drift length on shifts in 400-V SOI LDMOS breakdown voltage due to TID. IEEE Trans. Nucl. Sci. 67(11), 2392–2395 (2020)

Ningaraju, V., Lin, H.C., Chen, P.A., Lin, K.L.: Improving breakdown voltage for 120 V level up shifter by using vertical and lateral assisted depletion layers in 0.35 μm CMOS technology. Jpn. J. Appl. Phys. 59, 15 (2020)

Udrea, F., Garner, D., Sheng, K., Popescu, A., Lim, H., Milne, V.: SOI power devices. Electron. Commun. Eng. J. 12(1), 27–40 (2000)

W. Kloosterman and M. Swanenberg, “Modelling of High-Voltage SOI-LDMOS Transistors including Self-Heating,” In Simulation of Semiconductor Processes and Devices 2001. Springer, 2001, pp. 246–249

Arnold, E.: Silicon-on-insulator devices for high voltage and power IC applications. J. Electrochem. Soc. 141(7), 1983 (1994)

Yao, J., Guo, Y., Yang, K., Du, L., Zhang, J., Xia, T.: Analytical model for the SOI lateral power device with step width technique and high-K dielectric. IEEE Trans. Electron Devices 66(7), 3055–3059 (2019)

Litty, A., Ortolland, S., Golanski, D., Dutto, C., Cristoloveanu, S.: EDMOS in ultrathin FDSOI: impact of the drift region properties. Solid-State Electron. 128, 133–141 (2016)

Nikhil, K.S., DasGupta, N., DasGupta, A., Chakravorty, A.: Analysis and modeling of the snapback voltage for varying buried oxide thickness in SOI-LDMOS transistors. IEEE Trans. Electron Devices 63(10), 4003–4010 (2016)

Hu, Y., Wang, H., Du, C., Ma, M., Chan, M., He, J., Wang, G.: A high-voltage (>600 V) N-Island LDMOS with step-doped drift region in partial SOI technology. IEEE Trans. Electron Devices 63(5), 1969–1976 (2016)

Hu, Y., Xu, Q., Wang, L., Wang, J., Chen, S., Zhao, P., Wang, Y., Wang, G.: Dimension effect on breakdown voltage of partial SOI LDMOS. IEEE J. Electron Devices Soc. 5(3), 157–163 (2017)

Wang, Q., Cheng, X., Wang, Z., Xia, C., Shen, L., Zheng, L., Cao, D., Yu, Y., Shen, D.: A novel partial SOI EDMOS (> 800 V) with a buried N-type layer on the double step buried oxide. Superlattices Microstruct. 79(9), 1–8 (2015)

Orouji, A.A., Sharbati, S., Fathipour, M.: A new partial-SOI LDMOSFET with modified electric field for breakdown voltage improvement. IEEE Trans. Electron. Devices Mat. Reliab. 9(3), 449–453 (2009)

Karmalkar, S.: Introducing the device modeling procedure to electrical engineering students. IEEE Trans. Educ. 50(2), 137–142 (2007)

Ghione, G.: Looking for quality in TCAD-based papers. IEEE Trans. Electron Devices 66(8), 3252–3253 (2019)

Chung, S.-K.: An analytical model for breakdown voltage of surface implanted SOI RESURF LDMOS. IEEE Trans. Electron Devices 47(5), 1006–1009 (2000)

Yuan, S., Duan, B., Cao, Z., Guo, H., Yang, Y.: Analytical model of LDMOS with a single step buried oxide layer. Superlattices Microstruct. 97, 358–370 (2016)

Yuan, S., Duan, B., Cao, Z., Guo, H., Yang, Y.: Analytical model of LDMOS with a double Ste buried oxide layer. Solid-State Electron. 123, 6–14 (2016)

ATLAS Users Manual: Device Simulation Software, SILVACO Int., Santa Clara, CA, USA, Mar. 2015.

Van Overstraeten, R., De Man, H.: Measurement of the ionization rates in diffused silicon pn junctions. Solid-State Electron. 13(5), 583–608 (1970)

Young, K.K.: Short-channel effect in fully depleted SOI MOSFETs. IEEE Trans. Electron Devices 36(2), 399–402 (1989)

Sze, S.M., Ng, K.K.: Physics of semiconductor devices. wiley, New York (2006)

Hu, Y., Gong, Y., Liu, H., Xu, Q., Zhao, W.-S., Wang, J., Wang, Y., Wang, G.: Measurement of the ionization rates in diffused silicon pn junctions. IEEE Trans. Electron Devices 64(9), 3725–3733 (2017)

Sahoo, J., Mahapatra, R., Bhattacharayya, A.B.: An electronically programmable off-state breakdown voltage in SOI-LDMOS transistor with dual-dummy-gate for high voltage ESD protection. Microelectron. J. 108, 104968 (2021). https://doi.org/10.1016/j.mejo.2020.104968

Acknowledgements

The authors would like to acknowledge TEQIP-II and the Department of Electronics and Communication Engineering, NIT Durgapur, for extending financial support for the ATLAS device simulator. Shrabasti Mandal, an undergraduate student of the National Institute of Technology, Durgapur, is also acknowledged for their contribution.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sahoo, J., Mahapatra, R. Analytical breakdown voltage model for a partial SOI-LDMOS transistor with a buried oxide step structure. J Comput Electron 20, 1711–1720 (2021). https://doi.org/10.1007/s10825-021-01756-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-021-01756-x