Abstract

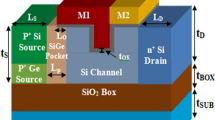

We present a detailed study on the n-channel single-gate junctionless transistor (JLT) at the \({10}-\hbox{nm}\) node. We investigate the influence of its structural parameters on the on-state current and the off-state leakage current. Furthermore, we show that the use of high-k spacers may not be advantageous in future nanoscale junctionless transistors and confirm this argument by simulation. We also present the results of our investigation on process variations, including the sensitivity of the JLT to random dopant fluctuations as well as the gate work function using Monte Carlo simulations. These results are then compared with those of a conventional FinFET. Finally, we provide design guidelines for JLTs at \({10}-\hbox{nm}\) gate length.

Similar content being viewed by others

References

Colinge, J.P., Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., et al.: Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225 (2010)

Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Colinge, J.P.: Junctionless multigate field-effect transistor. Appl. Phys. Lett. 94(5), 053511 (2009)

Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: Theory of the junctionless nanowire FET. IEEE Trans. Electron Dev. 58(9), 2903–2910 (2011)

Lee, C.W., Borne, A., Ferain, I., Afzalian, A., Yan, R., Akhavan, N.D., et al.: High-temperature performance of silicon junctionless MOSFETs. IEEE Trans. Electron Device 57(3), 620–625 (2010)

Ghosh, D., Parihar, M.S., Armstrong, G.A., Kranti, A.: High-performance junctionless MOSFETs for ultralow-power analog/RF applications. IEEE Electron Device Lett. 33(10), 1477–1479 (2012)

Lee, C.W., Nazarov, A.N., Ferain, I., Akhavan, N.D., Yan, R., Razavi, P., et al.: Low subthreshold slope in junctionless multigate transistors. Appl. Phys. Lett. 96(10), 102106 (2010)

Doria, R.T., Pavanello, M.A., Trevisoli, R.D., de Souza, M., Lee, C.W., Ferain, I., et al.: Junctionless multiple-gate transistors for analog applications. IEEE Trans. Electron Devices 58(8), 2511–2519 (2011)

Singh Parihar, M., Ghosh, D., Kranti, A.: Single transistor latch phenomenon in junctionless transistors. J. Appl. Phys. 113(18), 184503 (2013)

Parihar, M.S., Ghosh, D., Kranti, A.: Ultra low power junctionless MOSFETs for subthreshold logic applications. IEEE Trans. Electron Devices 60(5), 1540–1546 (2013)

Lee, C.W., Ferain, I., Afzalian, A., Yan, R., Akhavan, N.D., Razavi, P., et al.: Performance estimation of junctionless multigate transistors. Solid-State Electron. 54(2), 97–103 (2010)

Parihar, M.S., Ghosh, D., Armstrong, G.A., Yu, R., Razavi, P., Kranti, A.: Bipolar effects in unipolar junctionless transistors. Appl. Phys. Lett. 101(9), 093507 (2012)

Colinge, J.P., Kranti, A., Yan, R., Lee, C.W., Ferain, I., Yu, R., et al.: Junctionless nanowire transistor (JNT): properties and design guidelines. Solid-State Electron. 65, 33–37 (2011)

Park, C.H., Ko, M.D., Kim, K.H., Baek, R.H., Sohn, C.W., Baek, C.K., et al.: Electrical characteristics of 20-nm junctionless Si nanowire transistors. Solid-State Electron. 73, 7–10 (2012)

Jhan, Y.R., Thirunavukkarasu, V., Wang, C.P., Wu, Y.C.: Performance evaluation of silicon and germanium ultrathin body (1 nm) junctionless field-effect transistor with ultrashort gate length (1 nm and 3 nm). IEEE Electron Device Lett. 36(7), 654–656 (2015)

Choi, S.J., Moon, D.I., Kim, S., Duarte, J.P., Choi, Y.K.: Sensitivity of threshold voltage to nanowire width variation in junctionless transistors. IEEE Electron Device Lett. 32(2), 125–127 (2010)

Gundapaneni, S., Ganguly, S., Kottantharayil, A.: Enhanced electrostatic integrity of short-channel junctionless transistor with high-k spacers. IEEE Electron Device Lett. 32(10), 1325–1327 (2011)

Gundapaneni, S., Ganguly, S., Kottantharayil, A.: Bulk planar junctionless transistor (BPJLT): an attractive device alternative for scaling. IEEE Electron Device Lett. 32(3), 261–263 (2011)

Soree, B., Magnus, W.: Silicon nanowire pinch-off FET: basic operation and analytical model. In: 2009 10th International Conference on Ultimate Integration of Silicon. IEEE. pp. 245–248 (2009)

Tai, C.H., Lin, J.T., Eng, Y.C., Lin, P.H.: A novel high-performance junctionless vertical MOSFET produced on bulk-Si wafer. In: 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology. IEEE. pp. 108–110 (2010)

Sallese, J.-M., Chevillon, N., Lallement, C., Iniguez, B., Prégaldiny, F.: Charge-based modeling of junctionless double-gate field-effect transistors. IEEE Trans. Electron Devices 58(8), 2628–2637 (2011)

Jazaeri, F., Sallese, J.-M.: Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors. Cambridge University Press, Cambridge (2018)

Rassekh, A., Jazaeri, F., Fathipour, M., Sallese, J.-M.: Modeling interface charge traps in junctionless FETs, including temperature effects. IEEE Trans. Electron Devices 66(11), 4653–4659 (2019)

Wilson, L.: International Technology Roadmap for Semiconductors (ITRS). In: Semiconductor Industry Association; (2013)

ATLAS Device Simulation Software (Silvaco CU Santa Clara. Silvaco;. Available from: https://www.silvaco.com/

Ortiz-Conde, A., Sánchez, F.G., Liou, J.J., Cerdeira, A., Estrada, M., Yue, Y.: A review of recent MOSFET threshold voltage extraction methods. Microelectron. Reliab. 42(4–5), 583–596 (2002)

Predictive technology model [Online];. Available from: http://ptm.asu.edu/

Zhang, X., Connelly, D., Takeuchi, H., Hytha, M., Mears, R.J., Liu, T.J.K.: Comparison of SOI versus bulk FinFET technologies for 6T-SRAM voltage scaling at the 7-/8-nm node. IEEE Trans. Electron Devices 64(1), 329–332 (2016)

Ohtou, T., Sugii, N., Hiramoto, T.: Impact of parameter variations and random dopant fluctuations on short-channel fully depleted SOI MOSFETs with extremely thin BOX. IEEE Electron Device Lett. 28(8), 740–742 (2007)

Nawaz, S.M., Dutta, S., Chattopadhyay, A., Mallik, A.: Comparison of random dopant and gate-metal workfunction variability between junctionless and conventional FinFETs. IEEE Electron Device Lett. 35(6), 663–665 (2014)

Kleeberger, V.B., Graeb, H., Schlichtmann, U.: Predicting future product performance: modeling and evaluation of standard cells in FinFET technologies. In: Proceedings of the 50th Annual Design Automation Conference. ACM. p. 33, (2013)

Dadgour, H., De, V., Banerjee, K.: Statistical modeling of metal-gate work-function variability in emerging device technologies and implications for circuit design. In: 2008 IEEE/ACM International Conference on Computer-Aided Design. IEEE. pp. 270–277, (2008)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Rassekh, A., Fathipour, M. A single-gate SOI nanosheet junctionless transistor at 10-nm gate length: design guidelines and comparison with the conventional SOI FinFET. J Comput Electron 19, 631–639 (2020). https://doi.org/10.1007/s10825-020-01475-9

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01475-9