Abstract

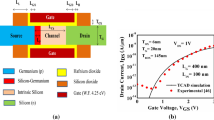

A comparative analysis is performed on a PNPN hetero-dielectric buried oxide (BOX) tunnel field-effect transistor (FET) with the conventional versus various modified structures, including the effects of using a high-k dielectric (HfO2) below the gate electrode and/or a low-bandgap material (InAs) as a source pocket. The use of InAs as a low-bandgap material greatly improves the tunneling of charge carriers from the source to channel region in the tunnel FET. Meanwhile, technology computer-aided design (TCAD) simulations reveal that inclusion of the high-k gate oxide with InAs as the source pocket in the PNPN structure results in a huge improvement in the electrostatic characteristics of the proposed structure in terms of both the ON-state current and subthreshold swing (SS). The proposed structure achieves a SS of 4.64 mV/dec and an ON-state current density of \(1.5\times 10^{-3}\) A/\(\mu \)m.

Similar content being viewed by others

References

Woerlee, P.H., Knitel, M.J., van Langevelde, R., Klaassen, D.B.M., Tiemeijer, L.F., Scholten, A.J., Zegers-van Duijnhoven, A.T.A.: RFCMOS performance trends. IEEE Trans. Electron Devices 48(8), 1776–1782 (2001)

Ghani, T., Mistry, K., Packan, P., Thompson, S., Stettler, M., Tyagi, S., Bohr, M.: Scaling challenges and device design requirements for high performance sub-50 nm gate length planar CMOS transistors. In: Symposium on VLSI Technology, pp. 174–175 (2000)

Sahu, P.K., Mohapatra, S.K., Pradhan, K.P.: Impact of downscaling on analog/RF performance of sub-100nm GS-DG MOSFET. J. Microelectron. Electron. Compon. Mater. 44(2), 119–125 (2014)

Meindl, J.D.: Low power microelectronics: retrospect and prospect. Proc. IEEE 83(4), 619–635 (1995)

Kumar, M., Hussain, M.A., Paul, S.K.: Performance of a two input nand gate using subthreshold leakage control techniques. J. Electron Devices 14, 1161–1169 (2012)

Seabaugh, A.C., Zhang, Q.: Low voltage tunnel transistor beyond CMOS logic. Proc. IEEE 98(12), 2095–2110 (2010)

Kumar, M., Hussain, M.A., Singh, L.K.: Design of a low power high speed ALU in 45 nm using GDI technique and its performance comparison. Commun. Comput. Inf. Sci. 142, 458–463 (2011)

Taghilou, H., Fathi, D.: Spin related transport in two pyrene and triphenylene graphene nanodisks using NEGF method. Phys. E Low Dimens. Syst. Nanostruct. 101, 208–211 (2018)

Rostami, A., Fathi, D.: Real space simulation of graphene nanoribbon field-effect transistor with double-lightly doped source and drain regions. In: Iranian Conference on Electrical Engineering (ICEE), pp. 253–258 (2017)

Aziziyan, M.R., Moghadam, N., Fathi, D., Ahmadi, V.: Analysis of strained double-lightly doped MOSCNT using NEGF. Appl. Phys. A 109(2), 481–488 (2012)

Moghadam, N., Aziziyan, M.R., Fathi, D.: Design and simulation of double-lightly doped MOSCNT using non-equilibrium Green’s function. Appl. Phys. A 108(3), 551–557 (2012)

Abaslou, S., Fathi, D.: A nano-transistor using a mesoscopic ring: the elastic and inelastic interactions analysis. Phys. E Low Dimens. Syst. Nanostruct. 44, 1309–1314 (2012)

Choi, W.Y., Park, B.G., Lee, J.D., Liu, T.J.K.: Tunneling field-effect transistor (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

Avci, U.E., Morris, D.H., Young, I.A.: Tunnel field-effect transistors: prospects and challenges. IEEE J. Electron Devices Soc. 3(3), 88–95 (2015)

Zhang, Q., Zhao, W., Seabaugh, A.: Low-subthreshold-swing tunnel transistors. IEEE Trans. Electron Device Lett. 27(4), 297–300 (2006)

Choi, W.Y., Park, B.G., Lee, J.D., Liu, T.J.K.: Tunnelling field effect transistor with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

Kumar, M.J., Janardhanan, S.: Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 60(10), 3285–3290 (2013)

Ghosh, B., Akram, M.W.: Junctionless tunnel field effect transistor. IEEE Electron Device Lett. 34(5), 584–586 (2013)

Zhu, Y., Hudait, M.K.: Low-power tunnel field effect transistors using mixed As and Sb based heterostructures. Nanotechnol. Rev. 2(6), 637–678 (2013)

Damrongplasit, N., Shin, C., Kim, S.H., Vega, R.A., Liu, T.J.K.: Study of random dopant fluctuation effects in germanium-source tunnel FETs. IEEE Trans. Electron Devices 58(10), 3541–3548 (2011)

Vijayvargiya, V., Vishvakarma, S.K.: Effect of drain doping profile on double-gate tunnel field-effect transistor and its influence on device RF performance. IEEE Trans. Nanotechnol. 13(5), 974–981 (2014)

Jhaveri, R., Nagavarapu, V., Woo, J.C.S.: Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Trans. Electron Devices 58(1), 80–86 (2011)

Ganapathi, K., Yoon, Y., Salahuddin, S.: Analysis of InAs vertical and lateral band-to-band tunneling transistors: leveraging vertical tunneling for improved performance. Appl. Phys. Lett. 97(3), 033504-1–033504-3 (2010)

Shubham, Sahay, Kumar, M.J.: Controlling the drain side tunneling width to reduce ambipolar current in tunnel FETs using heterodielectric BOX. IEEE Trans. Electron Devices 62(11), 3882–3886 (2015)

Anand, Sunny, Sarin, R.K.: Performance investigation of InAs based dual electrode tunnel FET on the analog/RF platform. Superlattices Microstruct. 97, 60–69 (2016)

Ford, A.C., Yeung, C.W., Chuang, Steven, Kim, Ha Sul, Plis, Elena, Krishna, Sanjay, Hu, Chenming, Javey, Ali: Ultrathin body InAs tunneling field-effect transistors on Si substrates. Appl. Phys. Lett. 98(11), 113105-1–113105-3 (2011)

Riel, H., Moselund, K. E., Bessire, C., Bjork, M. T., Schenk, A., Ghoneim, H., Schmid, H.: InAs-Si heterojunction nanowire tunnel diodes and tunnel FETs. In: International Electron Devices Meeting, pp. 16.6.1–16.6.4. San Francisco (2012)

Tomioka, K., Yoshimura, M., Fukui, T.: Steep-slope tunnel field-effect transistors using III–V nanowire/Si heterojunction. In: Proceedings of VLSI Technology (VLSIT) symposium, pp. 47–48. Honolulu (2012)

Ahish, S., Sharma, D., Vasantha, M.H., Kumar, Y.B.N.: Device and circuit level performance analysis of novel InAs/Si heterojunction double gate tunnel field effect transistor. Superlattices Microstruct. 94, 119–130 (2016)

Turkane, S.M., Kharate, G.K., Kureshi, A.K.: Ge/Si hetero-junction hetero-gate PNPN TFET with hetero-dielectric BOX to improve \(I_{\rm ON}\)/\(I_{\rm OFF}\). Indian J. Sci. Technol. 10(14), 1–7 (2017)

Silvaco Int.: ATLAS Device Simulation Software. Santa Clara (2014)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Aslam, M., Korram, G., Sharma, D. et al. Enhancement of the DC performance of a PNPN hetero-dielectric BOX tunnel field-effect transistor for low-power applications. J Comput Electron 19, 271–276 (2020). https://doi.org/10.1007/s10825-019-01427-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-019-01427-y