Abstract

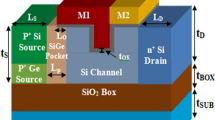

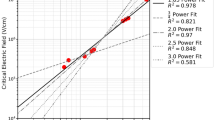

A superjunction (SJ) SiC VDMOS device with a deep trench (DT-SJ SiC) is investigated and compared with conventional SiC VDMOS (C SiC) and SJ SiC VDMOS (C-SJ SiC) devices using numerical simulations. The DT-SJ SiC VDMOS device has an SJ drift region and a deep trench (DT) extending from the gate to the drain. The SJ provides a better trade-off between the breakdown voltage (BV) and specific on-resistance (Ron,sp), resulting in a high figure of merit (FOM = BV2/Ron,sp). The DT leads to a lower maximum gate oxide field (Eox,max) by breaking the restriction of Gauss’s law on the vertical electric field at the gate oxide interface. Moreover, the gate charge (Qg) and the gate–drain charge (Qgd) are dramatically reduced. The electrical characteristics of the DT-SJ SiC are studied and compared with the other two devices with the same dimensions. Compared with the C SiC, the BV and the maximum FOM are increased by 308 V and 3028 MW cm−2, respectively, while Ron,sp, Eox,max, Qg, and Qgd are decreased by 47.97 %, 26.98 %, 35.59 %, and 58.73 %, respectively. Compared with the C-SJ SiC, the BV and the maximum FOM are increased by 18 V and 116 MW cm−2, respectively, while Ron,sp, Eox,max, Qg, and Qgd are decreased by 1.04 %, 21.48 %, 40.63 %, and 61.91 %, respectively.

Similar content being viewed by others

References

Jayant Baliga, B.: SiC power devices: from conception to social impact. In: Solid-State Device Research Conference (ESSDERC), pp. 192–197 (2016)

Niwa, H., Suda, J., Kimoto, T.: Ultrahigh-voltage SiC MPS diodes with hybrid unipolar/bipolar operation. IEEE Trans. Electron Devices 64(3), 874–881 (2017)

An, J., Namai, M., Yano, H., Iwamuro, N.: Investigation of robustness capability of −730 V P-channel vertical SiC power MOSFET for complementary inverter applications. IEEE Trans. Electron Devices 64(10), 4219–4225 (2017)

Benedetto, L.D., Licciardo, G.D., Erlbacher, T., Bauer, A.J., Liguori, R., Rubino, A.: A model of electric field distribution in gate oxide and JFET-region of 4H-SiC DMOSFETs. IEEE Trans. Electron Devices 63(9), 3795–3799 (2016)

Jiang, H., Wei, J., Dai, X., Ke, M., Deviny, I., Mawby, P.: SiC trench MOSFET with shielded fin-shaped gate to reduce oxide field and switching loss. IEEE Electron Device Lett. 37(10), 1324–1327 (2016)

Wei, J., Zhang, M., Jiang, H., Wang, H., Chen, K.J.: Dynamic degradation in SiC trench MOSFET with a floating p-shield revealed with numerical simulations. IEEE Trans. Electron Devices 64(6), 2592–2598 (2017)

Harada, S., Kobayashi, Y., Ariyoshi, K., Kojima, T., Senzaki, J., Tanaka, Y., Okumura, H.: 3.3-kV-Class 4H–SiC MeV-implanted UMOSFET with reduced gate oxide field. IEEE Electron Device Lett. 37(3), 314–316 (2016)

Wang, Y., Tian, K., Hao, Y., Yu, C., Liu, Y.: 4H–SiC step trench gate power metal-oxide-semiconductor field-effect transistor. IEEE Electron Device Lett. 37(5), 633–635 (2016)

Bharti, Deepshikha, Islam, Aminul: Optimization of SiC UMOSFET structure for improvement of breakdown voltage and ON-resistance. IEEE Trans. Electron Devices 65(2), 615–621 (2018)

Williams, R.K., Darwish, M.N., Blanchard, R.A., Siemieniec, R., Rutter, P., Kawaguchi, Y.: The trench power MOSFET: part I—history, technology, and prospects. IEEE Trans. Electron Devices 64(3), 674–691 (2017)

Nakamura, T., Nakano, Y., Aketa, M., Nakamura, R., Mitani, S., Sakairi, H., Yokotsuji, Y.: High performance SiC trench devices with ultra-low ron. In: IEDM, pp. 26.5.1–26.5.3 (2011)

Miura, M., Nakamura, S., Suda, J., Kimoto, T., Matsunami, H.: Fabrication of SiC lateral super junction diodes with multiple stacking p- and n-layers. IEEE Electron Device Lett. 24(5), 321–323 (2003)

Yu, L., Sheng, K.: Modeling and optimal device design for 4H–SiC super-junction devices. IEEE Trans. Electron Devices 55(8), 1961–1969 (2008)

Li, Z., Naik, H., Chow, T.P.: Design of GaN and SiC 5–20 kV vertical superjunction structures. In: Lester Eastman Conference on High Performance Devices (LEC), pp. 1–4 (2012)

Kosugi, R., Sakuma, Y., Kojima, K., Itoh, S., Nagata, A., Yatsuo, T., Tanaka, Y., Okumura, H.: First experimental demonstration of SiC super-junction (SJ) structure by multi-epitaxial growth method. In: ISPSD, pp. 346–349 (2014)

Zhong, X., Wang, B., Sheng, K.: Design and experimental demonstration of 1.35 kV SiC superjunction Schottky diode. In: ISPSD, pp. 231–234 (2016)

Masuda, T., Kosugi, R., Hiyoshi, T.: 0.97 mΩ cm2/820 V 4H–SiC super junction V-groove trench MOSFET. Mater. Sci. Forum 897, 483–488 (2017)

Udrea, F., Deboy, G., Fujihira, T.: Superjunction power devices, history, development, and future prospects. IEEE Trans. Electron Devices 64(3), 720–734 (2017)

Zhang, W., Zhang, B., Li, Z., Qiao, M., Li, Z.H.: Theory of superjunction with NFD and FD modes based on normalized breakdown voltage. IEEE Trans. Electron Devices 62(12), 4114–4120 (2015)

Chen, X.B., Mawby, P.A., Board, K., Salama, C.A.T.: Theory of a novel voltage-sustaining layer for power devices. Microelectron. J. 29(12), 1005–1011 (1998)

TCAD Sentaurus Device Manual Synopsys, Inc., (Version L-2016.03). Mountain View, CA USA

Zhou, X., Yue, R., Zhang, J., Dai, G., Li, J., Wang, Y.: 4H–SiC trench MOSFET with floating/grounded junction barrier-controlled gate structure. IEEE Trans. Electron Devices 64(11), 4568–4574 (2017)

Acknowledgements

This work was supported in part by the National Natural Science Foundation of China under grant 61574023, in part by the Fundamental Research Funds for the Central Universities under grant 2018CDXYTX0008, and in part by the Entrepreneurship and Innovation Program for Chongqing Overseas Returnees under grant cx2017009.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Hu, S., Huang, Y., Liu, T. et al. A comparative study of a deep-trench superjunction SiC VDMOS device. J Comput Electron 18, 553–560 (2019). https://doi.org/10.1007/s10825-019-01318-2

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-019-01318-2