Abstract

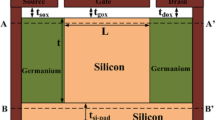

To achieve a steep subthreshold slope (SS) and a better \(I_\mathrm{ON}/I_\mathrm{OFF}\) ratio is a major concern for switching applications in semiconductor devices. To overcome these issues, the tunnel field effect transistor (TFET) is a promising device, as it has low leakage current and a low subthreshold slope at room temperature, making it a highly useful device for ultra-lower circuit applications. However, physical doping leads to random doping fluctuations, which is a serious issue in device technology. For this purpose, we report an electrically doped TFET with a metal strip implanted in the oxide layer between the channel/source junction to improve the performance of the device in terms of steep SS and \(I_\mathrm{ON}/I_\mathrm{OFF}\) at very small gate voltage. Furthermore, we have considered the appropriate length and work function of the metal strip to maintain the improved SS and \(I_\mathrm{ON}/I_\mathrm{OFF}\) ratio. The introduction of a metal strip in the oxide layer on a conventional device offers a higher \(I_\mathrm{ON}/I_\mathrm{OFF}\) ratio on the order of \(10^{8}\), steep subthreshold slope (Point \(\hbox {SS} = 8.07\) mV/decade) and significant change in analog/RF performance. The analog/RF figures of merit are observed in terms of transconductance (\(g_{m}\)), gate-to-drain capacitance (\(C_\mathrm{gd}\)), cutoff frequency (\(f_{T}\)), and gain bandwidth product. The proposed device would be very useful for ultra-low power and high frequency circuit applications at low gate voltages. All simulated results are carried out using 2-D ATLAS software.

Similar content being viewed by others

References

Colinge, J.P.: FinFETs and Other Multi-gate Transistors. Springer, New York (2008)

Kim, S.H., Yokoyama, M., Nakane, R., et al.: High performance tri-gate extremely thin-body InAs-On-insulator MOSFETs with high short channel effect immunity and vth tunability. IEEE Trans. Electron Devices 61, 1354–1360 (2014)

Sharma, D., Vishvakarma, S.K.: Precise analytical model for short channel cylindrical gate (CylG) gate-all-around (GAA) MOSFET. Solid State Electron. 86, 68–74 (2013)

Hur, J., Moon, D.-I., Choi, J.-M., et al.: A core compact model for multiple-gate junctionless FETs. IEEE Trans. Electron Devices 62, 2285–2291 (2015)

William, M.R., Gehan, A.J.: Silicon surface tunnel transistor. Appl. Phys. Lett. 67, 494–496 (1995)

Zhang, Q., Zhao, W., Seabaugh, A.: Low subthreshold swing tunnel transistors. IEEE Trans. Electron Device Lett. 27, 297–300 (2006)

Boucart, K., Ionescu, A.M.: Double gate tunnel FET with high-k gate dielectric. IEEE Trans. Electron Devices 54, 1725–1733 (2007)

Nigam, K., Pandey, S., Kondekar, P.N., et al.: A barrier controlled charge plasma based TFET with gate engineering for ambipolar suppression and RF/linearity performance improvement. IEEE Trans. Electron Devices 64, 2751–2757 (2017)

Guin, S., Chattopadhyay, A., Karmakar, A., et al.: Impact of a pocket doping on the device performance of a Schottky tunneling field-effect transistor. IEEE Trans. Electron Devices 61, 2515–2522 (2014)

Ahish, S., Sharma, D., Kumar, Y.B.N., et al.: Performance enhancement of novel InAs/Si Hetero double-gate tunnel FET using Gaussian doping. IEEE Trans. Electron Devices 63, 288–295 (2016)

Abdi, D.B., Kumar, M.J.: Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. Electron Device Soc. 2, 187–190 (2014)

Hraziia, A., Andrei, C., Vladimirescu, A., et al.: An analysis on the ambipolar current in Si double-gate tunnel FETs. Solid-State Electron. 70, 67–72 (2012)

Choi, W.Y., Lee, W.: Hetero-gate-dielectric tunneling field effect transistors. IEEE Trans. Electron Devices 57, 2317–2319 (2010)

Hraziia, A., Andrei, C., et al.: An analysis on the ambipolar current in Si double-gate tunnel FETs. Solid-State Electron. 70, 67–72 (2012)

Chiang, M.H., Lin, J.-N., Kim, K., et al.: Random dopant fluctuation in limited-width FinFET technologies. IEEE Trans. Electron Devices 54, 2055–2060 (2007)

Damrongplasit, Shin C., Kim, S.H., Vega, R.A., et al.: Study of random dopant fluctuation effects in germanium-source tunnel FETs. IEEE Trans. Electron Devices 58, 3541–3548 (2011)

Colinge, J.-P., Lee, C.-W., Afzalian, A., et al.: Nanowire transistors without junctions. Nat. Nanotechnol. 5, 225–229 (2010)

Ghosh, B., Akram, M.W.: Junctionless tunnel field effect transistor. IEEE Electron Device Lett. 34, 584–586 (2013)

Kumar, M.J., Janardhanan, S.: Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 60, 3285–3290 (2013)

Nigam, K., Kondekar, P.N., Sharma, D., et al.: A new approach for design and investigation of junctionless tunnel FET using electrically doped mechanism. Superlattices Microstruct. 98, 1–7 (2016)

Kondekar, P.N., Nigam, K., Pandey, S., Sharma, D.: Design and analysis of polarity controlled electrically doped tunnel FET with bandgap engineering for analog/RF applications. IEEE Trans. Electron Devices 64, 412–418 (2017)

Nigam, K., Pandey, S., Kondekar, P.N., Sharma, D.: Temperature sensitivity analysis of polarity controlled electrostatically doped tunnel field-effect transistor. Superlattices Microstruct. 97, 598–605 (2016)

Chandan, B.V., Dasari, S., Yadav, S., Sharma, D.: Approach to suppress ambipolarity and improve RF and linearity performances on ED-Tunnel FET. IET Micro Nano Lett. 13(5), 684–689 (2018)

Nigam, K., Pandey, S., Kondekar, P.N., et al.: Performance estimation of polarity controlled electrostatically doped tunnel field effect transistor. IET Micro Nano Lett. 12, 239–244 (2017)

Ranade, P., Takeuchi, H., King, T.J., et al.: Work function engineering of molybdenum gate electrodes by nitrogen implantation. Electrochem. Solid-State Lett. 4, G85–G87 (2001)

Johnson, R.W., Hultqvist, A., Bent, S.F.: A brief review of atomic layer deposition: from fundamentals to applications. Mater. Today 17, 236–246 (2015)

George, S.M.: Atomic layer deposition: an overview. Chem. Rev. 110(1), 111–131 (2009)

Kim, K., Lee, H.B., Johnson, R.W., Tanskanen, J.T., Liu, N., Kim, M.G., Pang, C., Ahn, C., Bent, S.F., Bao, Z.: Selective metal deposition at graphene line defects by atomic layer deposition. Nat. Commun. 5, 4781 (2014)

Griffiths, M.B.E., Pallister, P.J., Mandia, D.J., Barry, S.T.: Atomic layer deposition of gold metal. Chem. Mater. 28(1), 44–46 (2015)

Torndahl, T., Ottosson, M., Carlsson, J.-O.: Growth of copper metal by atomic layer deposition using copper(I) chloride, water and hydrogen as precursors. Thin Solid Films 458, 129–136 (2004)

Guo, L., Leobandung, E., Zhuang, L., Chou, S.Y.: Fabrication and Characterization of Room Temperature Silicon Single Electron Memory. American Vacuum Society, New York (1997)

ATLAS Device Simulation Software, Silvaco Int., Santa Clara, CA, USA (2014)

Tirkey, S., Sharma, D., Yadav, D.S., Yadav, S., et al.: Analysis of a novel metal implant junctionless tunnel FET for better DC and analog/RF electrostatic parameters. IEEE Trans. Electron Devices 64, 3943–3950 (2017)

Tirkey, S., Sharma, D., Raad, B.R., et al.: Introduction of a metal strip in oxide region of junctionless tunnel field effect transistor to improve DC and RF performance. J. Comput. Electron. 16, 714–720 (2017)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chandan, B.V., Gautami, M., Nigam, K. et al. Impact of a metal-strip on a polarity-based electrically doped TFET for improvement of DC and analog/RF performance. J Comput Electron 18, 76–82 (2019). https://doi.org/10.1007/s10825-018-1280-z

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-018-1280-z