Abstract

We study the impact of electron–phonon interaction on the subthreshold operation region of Tunnel-FETs by means of full-quantum simulations. Our approach is based on the nonequilibrium Green’s function method, where acoustic and optical phonon scatterings are taken into account through the self-consistent Born approximation. Two device architectures are analyzed: InAs nanowire longitudinal Tunnel-FETs, and 2D vertical Tunnel-FETs based on either an GaSb/AlSb/InAs heterostructure or a MoS\(_2\)/WTe\(_2\) van der Waals heterojunction. In InAs nanowire Tunnel-FETs with interface traps, electron–phonon interaction deteriorates the subthreshold swing by allowing trap-assisted tunneling at energies higher than the valence-band edge in the source. In vertical heterojunction Tunnel-FETs, optical phonon scattering increases the OFF current by inducing inelastic transition in the overlap region even in the absence of traps.

Similar content being viewed by others

References

Lundstrom, M.S.: Fundamentals of Carrier Transport. Addison Wesley, New York (1990)

Esseni, D., Palestri, P., Selmi, L.: Nanoscale MOS Transistors: Semi-classical Modeling and Applications. Cambridge University Press, Cambridge (2011)

Esseni, D., Pala, M., Rollo, T.: Essential physics of the OFF-state current in nanoscale MOSFETs and tunnel FETs. IEEE Trans. Electron Dev. 62(9), 3084 (2015). doi:10.1109/TED.2015.2458171

Seabaugh, A., Zhang, Q.: Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98(12), 2095 (2010). doi:10.1109/JPROC.2010.2070470

Ionescu, A.M., Riel, H.: Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(9), 329 (2011). doi:10.1038/nature10679

Lu, H., Seabaugh, A.: Tunnel field-effect transistors: state-of-the-art. J. Electron Dev. Soc. 2(4), 44 (2014). doi:10.1109/JEDS.2014.2326622

Dewey,G., Chu-Kung,B., Boardman,J., Fastenau,J.M., Kavalieros,J.,Kotlyar,R., Liu,W.K., Lubyshev, D., Metz, M., Mukherjee, N., Oakey,P., Pillarisetty, R., Radosavljevic, M., Then, H.W., Chau R.: Fabrication, characterization, and physics of III–V heterojunctiontunneling Field Effect Transistors (H-TFET) for steep sub-thresholdswing. In: IEEE IEDM Technical Digest, pp. 33.6.1–33.6.4 (2011). doi:10.1109/IEDM.2011.6131666

Gandhi, R., Chen, Z., Singh, N., Banerjee, K., Lee, S.: CMOS-compatible vertical-silicon-nanowire gate-all-around p-type tunneling FETs With 50 mV/decade subthreshold swing. Electron Dev. Lett. IEEE 32(11), 1504 (2011). doi:10.1109/LED.2011.2165331

Huang, Q, Huang, R., Zhan, Z., Qiu, Y., Jiang, W., Wu, C., Wang, Y.: A novel Si tunnel FET with 36mV/dec subthreshold slope based on junction depleted-modulation through striped gate configuration. In: 2012 IEEE International Electron Devices Meeting (IEDM), pp. 8.5.1–8.5.4 (2012). doi:10.1109/IEDM.2012.6479005

Tomioka, K., Yoshimura, M., Fukui, T.: Steep-slope tunnel field-effect transistors using III–V nanowire/Si heterojunction. In: VLSI Technology (VLSIT), 2012 Symposium on (2012), pp. 47–48. doi:10.1109/VLSIT.2012.6242454

Ganjipour, B., Wallentin, J., Borgstrm, M.T., Samuelson, L., Thelander, C.: Tunnel field-effect transistors based on InP-GaAs heterostructure nanowires. ACS Nano 6(4), 3109 (2012). doi:10.1021/nn204838m

Noguchi, M., Kim, S., Yokoyama, M., Ji, S., Ichikawa, O., Osada, T., Hata, M., Takenaka, M., Takagi, S.: High Ion/Ioff and low subthreshold slope planar-type InGaAs tunnel FETs with Zn-diffused source junctions, In: 2013 IEEE International Electron Devices Meeting (IEDM), pp. 28.1.1–28.1.4 (2013). doi:10.1109/IEDM.2013.6724707

Sarkar, D., Xie, X., Liu, W., Cao, W., Kang, J., Gong, Y., Kraemer, S., Ajayan, P.M., Banerjee, K.: A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526(7571), 91 (2015). doi:10.1038/nature15387

Khayer, M.A., Lake, R.K.: Effects of band-tails on the subthreshold characteristics of nanowire band-to-band tunneling transistors. J. Appl. Phys. 110(7), 074508 (2011). doi:10.1063/1.3642954

Mookerjea, S., Mohata, D., Mayer, T., Narayanan, V., Datta, S.: Temperature-dependent I–V characteristics of a vertical \({\rm In}_{0.53}{\rm Ga}_{0.47}{\rm As}\) tunnel FET. IEEE Electron Dev. Lett. 31(6), 564 (2010). doi:10.1109/LED.2010.2045631

Pala, M., Esseni, D., Conzatti, F.: Impact of interface traps on the IV curves of InAs Tunnel-FETs and MOSFETs: a full quantum study. In: IEEE IEDM Technical Digest, pp. 6.6.1–6.6.4 (2012). doi:10.1109/IEDM.2012.6478992

Koswatta, S., Lundstrom, M., Nikonov, D.: Influence of phonon scattering on the performance of p-i-n band-to-band tunneling transistors. Appl. Phys. Lett. 92(4), 043125 (2008). doi:10.1063/1.2839375

Pala, M., Esseni, D.: Interface traps in InAs nanowire tunnel-FETs and MOSFETs—Part I: model description and single trap analysis in tunnel-FETs. IEEE Trans. Electron Dev. 60(9), 2795 (2013). doi:10.1109/TED.2013.2274196

Esseni, D., Pala, M.: Interface Traps in InAs Nanowire Tunnel FETs and MOSFETs – Part II: Comparative Analysis and Trap-Induced Variability. IEEE Trans. Electron Dev. 60(9), 2802 (2013). doi:10.1109/TED.2013.2274197

Datta, S.: Quantum Transport—Atom to Transistor. Cambridge University Press, Cambridge (2005)

Venugopal, R., Ren, Z., Datta, S., Lundstrom, M.S., Jovanovic, D.: Simulating quantum transport in nanoscale transistors: Real versus mode-space approaches. J. Appl. Phys. 92(7), 3730 (2002). doi:10.1063/1.1503165

Poli, S., Pala, M., Poiroux, T., Deleonibus, S., Baccarani, G., Trans, I.E.E.E.: Size dependence of surface-roughness-limited mobility in Silicon-nanowire FETs. Electron Dev. 55(11), 2968 (2008). doi:10.1109/TED.2008.2005164

Shin, M.: Full-quantum simulation of hole transport and band-to-band tunneling in nanowires using the k\(\cdot {}\)p method. J. Appl. Phys. 106(5), 054505 (2009). doi:10.1063/1.3208067

Mahan, G.: Many-Particle Physics. Plenum Press, New York (1990)

Rogdakis, K., Poli, S., Bano, E., Zekentes, K., Pala, M.: Phonon and surface roughness limited mobility of gate-all-around 3C-SiC and Si nanowire FETs. Nanotechnology 20(29), 295202 (2009). http://stacks.iop.org/0957-4484/20/i=29/a=295202

Ferry, D., Goodnick, S.: Transport in Nanostructures. Cambridge University Press, Cambridge (1997)

Anantram, M.P., Lundstrom, M.S., Nikonov, D.E.: Modeling of Nanoscale Devices. Proc. of IEEE 96, 1511 (2008). doi:10.1109/JPROC.2008.927355

Lopez Sancho, M.P., Lopez Sancho, J.M., Rubio, J.: Quick iterative scheme for the calculation of transfer matrices: application to Mo (100). J. Phys. F 14, 1205 (1984). doi:10.1088/0305-4608/14/5/016

Luisier, M., Klimeck, G.: Atomistic full-band simulations of silicon nanowire transistors: effects of electron-phonon scattering. Phys. Rev. B 80, 155430 (2009). doi:10.1103/PhysRevB.80.155430

Bahder, T.B.: Eight-band k\(\cdot {}\)p model of strained zinc-blende crystals. Phys. Rev. B 41(17), 11992 (1990). doi:10.1103/PhysRevB.41.11992

Luisier, M., Klimeck, G.: Atomistic full-band design study of InAs band-to-band tunneling field-effect transistors. IEEE Electron Dev. Lett. 30(6), 602 (2009). doi:10.1109/LED.2009.2020442

Luisier, M., Klimeck, G.: Simulation of nanowire tunneling transistors: from the Wentzel–Kramers–Brillouin approximation to full-band phonon-assisted tunneling. J. Appl. Phys. 107(8), 084507 (2010). doi:10.1063/1.3386521

Avci, U., Hasan, S., Nikonov, D., Rios, R., Kuhn, K., Young, I.: Understanding the feasibility of scaled III-V TFET for logic by bridging atomistic simulations and experimental results. In: 2012 Symposium on VLSI Technology (VLSIT), pp. 183–184 (2012). doi:10.1109/VLSIT.2012.6242522

Shin, M., Lee, S., Klimeck, G.: Computational study on the performance of Si nanowire pMOSFETs based on the k \(\cdot \) p method. IEEE Trans. Electron Dev. 57(9), 2274 (2010). doi:10.1109/TED.2010.2052400

Conzatti, F., Pala, M., Esseni, D., Bano, E., Selmi, L.: Strain-induced performance improvements in InAs nanowire tunnel FETs. IEEE Trans. Electron Dev. 59(8), 2085 (2012). doi:10.1109/TED.2012.2200253

Fischetti, M.V.: Monte Carlo simulation of transport in technologically significant semiconductors of the Diamond and Zinc-Blende structures - Part I: homogeneous transport. IEEE Trans. Electron Dev. ED–38, 634 (1991). doi:10.1109/16.75176

Vurgaftman, I., Meyer, J.R., Ram-Mohan, L.R.: Band parameters for III–V compound semiconductors and their alloys. J. Appl. Phys. 89(11), 5815 (2001). doi:10.1063/1.1368156

Veprek, R.G., Steiger, S., Witzigmann, B.: Ellipticity and the spurious solution problem of k\(\cdot {}\)p envelope equations. Phys. Rev. B 76, 165320 (2007). doi:10.1103/PhysRevB.76.165320

Mookerjea, S., Mohata, D., Krishnan, R., Singh, J., Vallet, A-, Ali, A., Mayer, T., Narayanan, V., Schlom, D., Liu, A., Datta, S.: Experimental demonstration of 100nm channel length In\(_{0.53}\)Ga\(_{0.47}\)As-based vertical inter-band tunnel Field Effect Transistors (TFETs) for ultra low-power logic and SRAM applications. In: IEEE IEDM Technical Digest, pp. 949–952 (2009). doi:10.1109/IEDM.2009.5424355

Brocard, S., Pala, M., Esseni, D.: Design options for hetero-junction tunnel FETs with high on current and steep sub-threshold voltage slope. In: Electron Devices Meeting (IEDM), 2013 IEEE International, pp. 5.4.1–5.4.4 (2013) doi:10.1109/IEDM.2013.6724567

Mingda, L., Esseni, D., Snider, G., Jena, D., Xing, H.G.: Single particle transport in two-dimensional heterojunction interlayer tunneling field effect transistor. J. Appl. Phys. 115, 074508 (2014). doi:10.1063/1.4866076

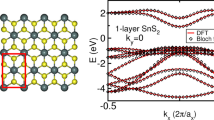

Szabo, A., Koester, S., Luisier, M.: Ab-initio simulation of van der Waals MoTe\(_2\)-SnS\(_2\) heterotunneling FETs for low-power electronics. IEEE Electron Dev. Lett. 36(5), 514 (2015). doi:10.1109/LED.2015.2409212

Cao, J., Logoteta, D., Özkaya, S., Biel, B., Cresti, A., Pala, M., Esseni, D.: A computational study of van der Waals tunnel transistors: Fundamental aspects and design challenges. In: 2015 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2015), pp. 12.5.1–12.5.4. doi:10.1109/IEDM.2015.7409684

Szabo, A., Koester, S. J., Luisier, M.: Metal-dichalcogenide hetero-TFETs: are they a viable option for low power electronics? Device Research Conference (DRC), 19 (2014). doi:10.1109/DRC.2014.6872279

Torun, E., Sahin, H., Cahangirov, S., Rubio, A., Peeters, F.M.: Anisotropic electronic, mechanical, and optical properties of monolayer WTe\(_2\) J. Appl. Phys. 119, 074307 (2016). doi:10.1063/1.4942162

Cao, J., Cresti, A., Esseni, D., Pala, M.: Quantum simulation of a heterojunction vertical tunnel FET based on 2D transition metal dichalcogenides. Solid-State Electron. 116, 1 (2016). doi:10.1016/j.sse.2015.11.003

Kaasbjerg, K., Thygesen, K.S., Jacobsen, K.W.: Phonon-limited mobility in \(n\)-type single-layer MoS\({}_{2}\) from first principles. Phys. Rev. B 85, 115317 (2012). doi:10.1103/PhysRevB.85.115317

Acknowledgments

This work was supported by the French ANR through the project No. ANR-13-NANO-0009-01 (“NOODLES”).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Pala, M.G., Grillet, C., Cao, J. et al. Impact of inelastic phonon scattering in the OFF state of Tunnel-field-effect transistors. J Comput Electron 15, 1240–1247 (2016). https://doi.org/10.1007/s10825-016-0900-8

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-016-0900-8