Abstract

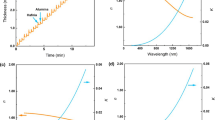

The effect of rapid thermal annealing on the oxide charge distribution of Al/HfO\(_2\)/SiO\(_2\)/Si metal–oxide–semiconductor structures are studied using technology computer-aided design (TCAD) simulations and experiments. The simulated electrical characteristics are compared with experimentally obtained data. The interface traps are found to be nonuniform in nature and laterally distributed following a Gaussian profile. The distribution of interface trap charges arises because of spatial electric field variation in the oxide film upon gate bias application. The interface trap density is found to decrease with increase in annealing temperature. It is further observed that, at higher annealing temperature, the fixed oxide charge density increases due to interfacial Hf silicate formation.

Similar content being viewed by others

References

Fenske, F.: Influence of lateral charge inhomogeneities in MOS structures on the determination of the interface state density distribution from HF CV curves. Phys. Stat. Sol. A 79, 417–421 (1983)

McNutt, M.J., Sah, C.T.: Effects of spatially inhomogeneous oxide charge distribution on the MOS capacitancevoltage characteristics. J. Appl. Phys. 45, 3916–3921 (1974)

Dai, C.-H., Chang, T.-C., Chu, A.-K., Kuo, Y.-J., Ho, S.-H., Hsieh, T.-Y., Lo, W.-H., Chen, C.-E., Shih, J.-M., Chung, W.-L., Dai, B.-S., Chen, H.-M., Xia, G., Cheng, O., Huang, C.T.: Hot carrier effect on gate-induced drain leakage current in n-MOSFETs with HfO\(_2\)/Ti\(_{1-x}\)N\(_x\) gate stacks. Electrochem. Solid-State Lett. 15, H211–H214 (2012)

Khairnar, A.G., Mahajan, A.M.: Effect of post-deposition annealing temperature on RF-Sputtered HfO\(_2\) thin film for advanced CMOS technology. Solid State Sci. 15, 24–28 (2013)

Bo, H., Hua, H.S., Min, W.F.: Modeling of tunneling current in ultrathin MOS structure with interface trap charge and fixed oxide charge. Chin. Phys. B 22, 017301 (2013)

Autran, J.-L., Munteanu, D., Dinescu, R., Houssa, M.: Stretch-out of high-permittivity MOS capacitancevoltage curves resulting from a lateral non-uniform oxide charge distribution. J. Non-Cryst. Solids 322, 219–224 (2003)

Chim, W.K., Lim, P.S.: Latent damage investigation on lateral nonuniform charge generation and stress-induced leakage current in silicon dioxide subjected to high-field current impulse stressing. IEEE Trans. Electron. Devices 47, 473–481 (2000)

Chim, W.K., Lim, P.S.: Hole injection with limited charge relaxation, lateral nonuniform hole trapping, and transient stress-induced leakage current in impulse-stressed thin (\({<}\) 5nm) nitrided oxides. J. Appl. Phys. 91, 1304–1313 (2002)

Chen, C., Ma, T.P.: Direct lateral profiling of hot-carrier-induced oxide charge and interface traps in thin gate MOSFET’s. IEEE Trans. Electron. Devices 45, 512–520 (1998)

Biswas, D., Faruque, S.A.K.M., Sinha, A.K., Upadhyay, A., Chakraborty, S.: Effect of thermal annealing and oxygen partial pressure on the swelling of HfO\(_2\)/SiO\(_2\)/Si metal-oxide-semiconductor structure grown by rf sputtering: a synchrotron x-ray reflectivity study. Appl. Phys. Lett. 105, 113511 (2014)

Howard, J.M., Craciun, V., Essary, C., Singh, R.K.: Interfacial layer formation during high-temperature annealing of ZrO\(_2\) thin films on Si. Appl. Phys. Letts. 81, 3431–3433 (2002)

Quah, H.J., Cheong, K.Y.: Study on gallium nitride-based metal-oxide-semiconductor capacitors with RF magnetron sputtered Y\(_2\)O\(_3\) gate. IEEE Trans. Electron Device 59, 3009–3016 (2012)

Lee, B., Novak, S.R., Lichtenwalner, D.J., Yang, X., Misra, V.: Investigation of the origin of modulation by capping layer approaches for NMOS application: role of La diffusion, effect of host high-layer, and interface properties. IEEE Trans. Electron Devices 58, 3106–3115 (2011)

Hill, W.A., Coleman, C.C.: A single-frequency approximation for interface-state density determination. Solid-State Electron 23, 987–993 (1979)

Oulachgar, E.H., Aktik, C., Scarlete, M., Dostie, S., Sowerby, R., Gujrathi, S.: Electrical and optical characterization of SiONC dielectric thin film deposited by polymer-source chemical vapor deposition. J. Appl. Phys. 101, 084107 (2007)

Nicollian, E.H., Goetzberger, A., Lopez, A.D.: Expedient Method of obtaining interface state properties. Solid-State Electron 12, 937–944 (1968)

Brews, J.R.: Rapid interface parametrization using a single MOS conductance curve. Solid-State Electron 26, 711–716 (1983)

Nicollian, E.H., Goetzberger, A.: The Si-SiO\({}_2\) interface: electrical properties as determined by Metal-Insulator-Silicon conductance technique. Bell Syst. Tech. J. XLVI, 1055–1133 (1967)

Sentaurus Device User Guide: Version G-2012.06. (2012)

Masetti, G., Severi, M., Solmi, S.: Modeling of carrier mobility against carrier concentration in Arsenic-, Phosphorus-, and Boron-doped silicon. IEEE Trans. Electron Devices 30, 764–769 (1983)

Canali, C., Majni, G., Minder, R., Ottaviani, G.: Electron and hole drift velocity measurements in silicon and their empirical relation to electric field and temperature. IEEE Trans. Electron Devices 22, 1045–1047 (1975)

Chakraborty, C.: Role of interfacial layer thickness on high-\(\kappa \) dielectric-based MOS devices. J. Adv. Dielectr. 4, 1450023 (2014)

Lombardi, C., Manzini, S., Saporito, A., Vanzi, M.: A physically based mobility model for numerical simulation of nonplanar devices. IEEE Trans. Comput. Aided Des. 7, 1164–1171 (1988)

Schroder, D.K.: Semiconductor Material and Device Characterization. Wiley, Hoboken (2015)

Biswas, D., Sinha, A.K., Chakraborty, S.: Optimization of annealing temperature for high-based gate oxides using differential scanning calorimetry. J. Vac. Sci. Technol. B 33, 052205 (2015)

Guha, S., Narayanan, V.: Oxygen vacancies in high dielectric constant oxide-semiconductor films. Phys. Rev. Lett. 98, 196101 (2007)

Wong, H., Sen, B., Filip, V., Poon, M.C.: Material properties of interfacial silicate layer and its influence on the electrical characteristics of MOS devices using hafnia as the gate dielectric. Thin Solid Films 504, 192–196 (2006)

Ghetti, A., Sangiorgi, E., Bude, J., Sorsch, T.W., Weber, G.: Tunneling into interface states as reliability monitor for ultrathin oxides. IEEE Tarns. Electron Devices 47, 2358–2365 (2000)

Ghetti, A.: Gate oxide reliability: Physical and computational models. Springer Ser. Mater. Sci. 72, 201–258 (2004)

Lenzlinger, M., Snow, E.H.: Fowler-Nordheim tunneling into thermally grown SiO\(_2\). J. Appl. Phys. 40, 278–283 (1969)

Lee, W.-C., Hu, C.: Modeling CMOS tunneling currents through ultrathin gate oxide due to conduction- and valence-band electron and hole tunneling. IEEE Trans. Electron Devices 48, 1366–1373 (2001)

Maserjian, J.: Tunneling in thin MOS structures. J. Vac. Sci. Technol. 11, 996–1003 (1974)

Gehring, A.: Simulation of tunneling in semiconductor devices: Dissertation, Technische Universit\(\ddot{a}\)t Wien, (2003). http://www.iue.tuwien.ac.at/phd/gehring/

Schenk, A., Heiser, G.: Modeling and simulation of tunneling through ultra-thin gate dielectrics. J. Appl. Phys. 81, 7900–7908 (1997)

Karner, M., et al.: A multi-purpose Schr\(\ddot{o}\)dinger-Poisson solver for TCAD application. J. Comput. Electron 6, 179–182 (2007)

Chim, W.-K., Lim, P.-S.: Latent damage investigation on lateral nonuniform charge generation and stress-induced leakage current in silicon dioxide subjected to high-field current impulse stressing. IEEE Trans. Electron Devices 47, 473–481 (2000)

Satake, H., Toriumi, A.: Dielectric breakdown mechanism of thin-SiO\(_2\) studied by the post-breakdown resistance statistics. IEEE Trans. Electron Devices 47, 741–745 (2000)

Acknowledgments

The authors would like to acknowledge Prof. Tapas Kumar Chini of Saha Institute of Nuclear Physics, Kolkata for providing the SEM facility. The authors would also like to thank the Department of Atomic Energy, Govt. of India for financial assistance.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Biswas, D., Chakraborty, A. & Chakraborty, S. Role of annealing temperature in the oxide charge distribution in high-\(\kappa \)-based MOS devices: simulation and experiment. J Comput Electron 15, 795–800 (2016). https://doi.org/10.1007/s10825-016-0829-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-016-0829-y