Abstract

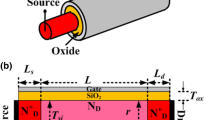

Over the years, the approach of cylindrical gate MOSFETs has attracted several research initiatives due to the very inherent benefit of the cylindrical geometry over other conventional planar structures. Nowadays, the present boon in the research field of nanoscale device physics is attributed to a large extent by the development of junctionless devices. In our current research endeavor, we have for the first time proposed a new idea by incorporating the innovative concept of work function engineering by the continuous horizontal variation of mole fraction in a binary metal alloy gate into a junctionless cylindrical gate MOS structure, thereby presenting a new device structure, a junctionless work function engineered gate cylindrical gate MOSFET (JL WFEG CG MOSFET). We have presented a rigorous analytical modeling of the proposed JL WFEG CG MOS structure by solving the two dimensional Poisson’s equation in cylindrical co-ordinates. Based on this analytical modeling, an overall performance comparison of the proposed JL WFEG CG MOS and normal JL CG MOS structure has been investigated in order to testify the improved performance of the proposed JL WFEG CG structure over its normal JL CG equivalent in terms of reduced short channel effects, threshold voltage roll off, drain induced barrier lowering and superior current driving capability. The results obtained from our analytical analysis are found to be in good agreement with the simulation results, thereby establishing the accuracy of our modeling.

Similar content being viewed by others

References

The International Technology Roadmap for Semiconductor, Emerging Research Devices 2009

Li, C., Zhuang, Y., Di, S., Han, R.: Subthreshold behavior models for nanoscale short-channel junctionless cylindrical surrounding-gate MOSFETs. IEEE Trans. Electron Devices 60(11), 3655–3662 (2013)

Iñiguez, B., Fjeldly, T.A., Lázaro, A., Danneville, F., Deen, M.J.: Compact-modeling solutions for nanoscale double-gate and gate-all-around MOSFETs. IEEE Trans. Electron Devices 53(9), 2128–2141 (2006)

Iñíguez, B., Jiménez, D., Roig, J., Hamid, H.A., Marsal, L.F., Pallarès, Josep: Explicit continuous model for long-channel undoped surrounding gate MOSFETs. IEEE Trans. Electron Devices 52(8), 1868–1873 (2005)

Jiménez, D., Sáenz, J.J., Iñíguez, B., Suñé, J., Marsal, L.F., Pallarès, J.: Modeling of nanoscale gate-all-around MOSFETs. IEEE Electron Device Lett. 25(5), 314–316 (May 2004)

Lee, C.-W., Borne, A., Ferain, I., Afzalian, A., Yan, R., Dehdashti Akha-van, N., Razavi, P., Colinge, J.-P.: High-temperature performance of silicon junctionless MOSFETs. IEEE Trans. Electron Devices 57(3), 620–625 (2010)

Colinge, J.-P., Lee, C.-W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O’Neill, B., Blake, A., White, M., Kelleher, A.-M., McCarthy, B., Murphy, R.: Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

Lee, C.-W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Colinge, J.P.: Junctionless multigate field-effect transistor. Appl. Phys. Lett. 94(5), 053511-1–053511-2 (2009)

Deb, S., Basanta Singh, N., Islam, N., Kumar Sarkar, S.: Work function engineering with linearly graded binary metal alloy gate electrode for short channel SOI MOSFET. IEEE Trans. Nanotechnol. 11(3), 472–478 (2012)

Pan, A., Liu, R., Sun, M., Ning, C.-Z.: Spatial composition grading of quaternary ZnCdSSe alloy nanowires with tunable light emission between 350 and 710 nm on a single substrate. Am. Chem. Soc. ACSNANO 4(2), 671–680 (2010)

Lee, C.K., Kim, J.Y., Hong, S.N., Zhong, H., Chen, B., Mishra, V.: Properties of Ta-Mo alloy gate electrode for n-MOSFET. J. Mater. Sci. 40, 2693–2695 (2005)

Tsui, B.-Y., Huang, C.-F.: Wide range work function modulation of binary alloys for MOSFET application. IEEE Electron Device Lett. 24(3), 153–155 (2003)

Chiang, T.-K.: A quasi-two-dimensional threshold voltage model for short-channel junctionless double-gate MOSFETs. IEEE Trans. Electron Devices 59(9), 2284–2289 (2012)

Chiang, T.-K.: A new quasi-2-D threshold voltage model for short-channel junctionless cylindrical surrounding gate (JLCSG) MOSFETs. IEEE Trans. Electron Devices 59(11), 3127–3129 (2012)

Cong, L., Yiqi, Z., Ru, H.: New analytical threshold voltage model for halo-doped cylindrical surrounding-gate MOSFETs. J. Semicond. 32(7), 074002-1–074002-8 (2011)

Li, C., Zhuang, Y., Di, S., Han, R.: Subthreshold behavior models for nanoscale short-channel junctionless cylindrical surrounding-gate MOSFETs. IEEE Trans. Electron Device 60(11), 3655–3662 (2013)

Kranti, A., Haldar, S., Gupta, R.S.: Analytical model for threshold voltage and I-V characteristics of fully depleted short channel cylindrical / surrounding gate MOSFET. Microelectron. Eng. 56, 241–259 (2001)

Jagadesh Kumar, M., Orouji, A.A., Dhakad, H.: New dual-material SG nanoscale MOSFET: analytical threshold-voltage model. IEEE Trans. Electron Devices 53(4), 920–923 (2006)

Manna, B., Sarkhel, S., Islam, N., Sarkar, S., Kumar Sarkar, S.: Spatial composition grading of binary metal alloy gate electrode for short-channel SOI/SON MOSFET application. IEEE Trans. Electron Devices 59(12), 3280–3287 (2012)

Young, K.K.: Short-channel effects in fully depleted SOI MOSFET’s. IEEE Trans. Electron Devices 36, 399–402 (1989)

Auth, C.P., Plummer, J.D.: Scaling theory for cylindrical, fully-depleted, surrounding-gate MOSFET’s. IEEE Electron Device Lett. 18(2), 74–76 (1997)

Tsormpatzoglou, A., Dimitriadis, C.A., Clerc, R., Pananakakis, G., Ghibaudo, G.: Threshold voltage model for short-channel undoped symmetrical double-gate MOSFETs. IEEE Trans. Electron Devices 55(9), 2512–2516 (2008)

Lázaro, A., Iñiguez, B.: RF and noise performance of double gate and single gate SOI. Solid-State Electron. 50, 826–842 (2006)

Reddy, G.V., Jagadesh Kumar, M.: A new dual material double gate (DMDG) nanoscale SOI MOSFET -two dimensional analytical modeling and simulation. IEEE Trans. Electron Devices 4(2), 260–268 (2005)

Ghosh, P., Haldar, S., Gupta, R.S., Gupta, M.: An analytical drain current model for dual material engineered cylindrical/surrounded gate MOSFET. Microelectron. J. 43, 17–24 (2012)

Acknowledgments

Saheli Sarkhel thankfully acknowledges the financial support obtained in the form of State Research Fellowship from the Department of Electronics and Telecommunication Engineering, Jadavpur University.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sarkhel, S., Sarkar, S.K. A comprehensive two dimensional analytical study of a nanoscale linearly graded binary metal alloy gate cylindrical junctionless MOSFET for improved short channel performance. J Comput Electron 13, 925–932 (2014). https://doi.org/10.1007/s10825-014-0609-5

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-014-0609-5