Abstract

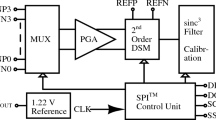

Advent in VLSI technology made digital signal processing to take over analog signal processing. Analog to digital converter plays a vital role in modern digital signal processing applications. Various signal processing applications incorporated sigma delta ADC among different analog to digital converters because of its digital dominant architecture. This paper presents the design of a low pass continuous time sigma delta analog to digital converter on-chip architecture with a very few passive components connected externally to FPGA suitable for signal processing applications, wireless application, sonar and radar beamforming. Schematic level architecture of high speed comparator working at a differential swing which is not allowed by FPGA standard differential pads is designed. By applying various differential swings at the input to LVPECL, the performance and power is analyzed. High performance comparator schematic is designed as on-chip continuous-time sigma-delta analog to digital converter architecture. SPICE simulations are carried out to verify the maximum input frequency for given RC values. Xilinx provided Spartan 6 I/O pad and package SPICE models are used. Power analysis is carried out with LVPECL logic family based differential buffers along with external RC circuit. The analog and digital sections simulations along with mixed signal simulations at different stages are performed. Power and performance analysis are carried out using h-Spice and questasim simulations. schematic level architecture of a high speed comparator at a differential swing of 1.65 ± 1.5 V which is not allowed by standard differential pads is designed. Analysis illustrates that proposed on-chip continuous-time sigma-delta analog to digital converter exhibits a sampling rate of 400 MHz designed with high speed comparator with varied differential swing. Power analysis resulted with 1.86 mW for an input signal of 1 MHz. Optimal filtering is achieved with total decimation of 400, out of which the decimation of 100 is achieved by CIC filter and PFIR filter achieves remaining decimation factor of 4. Output data rate of 1 MHz with a dynamic range of 72 dB is achieved with less bill of material that suites for signal processing applications.

Similar content being viewed by others

References

Artigas, J. I., Urriza, I., Navarro, D., Barragan, L. A., & Acero, J. (2009). Comparator-less digital implementation of AC-coupled ΣΔ A/D converters. Electronics Letters, 45(11), 537–538.

Bindu Tushara, D., & Harsha Vardhini, P. A. (2015). FPGA implementation of image transformation techniques with Zigbee transmission to PC. International Journal of Applied Engineering Research, 10(55), 420–425.

Babu, K. M. C., & Harsha Vardhini, P. A. (2020). Design and development of cost effective arduino based object sorting system. In 2020 International conference on smart electronics and communication (ICOSEC), Trichy, India (pp. 913–918). https://doi.org/10.1109/ICOSEC49089.2020.9215269.

Bindu Tushara, D., & Harsha Vardhini P. A. (2017). Performance of efficient image transmission using Zigbee/I2C/Beagle board through FPGA. In H. Saini, R. Sayal, S. Rawat (Eds.), Innovations in computer science and engineering. Lecture notes in networks and systems (Vol. 8). Singapore: Springer. https://doi.org/10.1007/978-981-10-3818-1_27.

Brandt, B. P. (1991). Oversampled analog-to-digital conversion. Integrated Circuits Labaratory, Technical Report No. ICL91-009, Stanford University.

Harsha Vardhini, P. A., Harsha, M. S., Sai, P. N., & Srikanth, P. (2020). IoT based smart medicine assistive system for memory impairment patient. In 2020 12th international conference on computational intelligence and communication networks (CICN), Bhimtal, India (pp. 182–186). https://doi.org/10.1109/CICN49253.2020.9242562.

Harsha Vardhini, P. A., & Madhavi Latha, M. (2015). Power analysis of high performance FPGA low voltage differential I/Os for SD ADC architecture. International Journal of Applied Engineering Research, 10(55), 3287–3292.

Harsha Vardhini, P. A., Madhavi Latha, M., & Krishna Reddy, C. V. (2012). A 65 dB SF DR, 500 kS/s continuous time all digital sigma delta a DC for SON AR applications. In Pearl Jubilee international conference on “navigation and communication” (NAVCOM-2012).

HarshaVardhini, P. A., Madhavi Latha, M., & Krishna Reddy, C. V. (2013). Analysis on digital implementation of Sigma-Delta ADC with passive analog components. International Journal of Computing and Digital Systems (IJCDS), University of Bahrain, 2(2), 71–77.

Harsha Vardhini, P. A., & Murali Mohan Babu, Y. (2020). FPGA based energy-aware image compression and transmission with single board computers. Journal of Green Engineering, 10(5), 2483–2497.

Hu, J., Li, D., Liu, M., & Zhu, Z. (2019). A 10-Ks/s 625-Hz-bandwidth 65-db SNDR 2nd-order noise-shaping SAR ADC for biomedical sensor applications. IEEE Sensors Journal. https://doi.org/10.1109/jsen.2019.2949641.

Jacomet, M., Goethe, J., Zbinden, V., & Narvez, C. (2004). On the dynamic behavior of a novel digital-only sigma-delta A/D converter. In Proceedings of sympsoium on integrated circuits and system design, Pernambuco, Brazil (pp. 222–227).

Norsworthy, S. R., Schreier, R., & Temes, G. C. (1996). Delta-sigma data converters: Theory, design and simulation. New York: IEEE Press.

Palagiri, A. H. V., Makkena, M. L., & Chantigari, K. R. (2016). An efficient on-chip implementation of reconfigurable continuous time sigma delta ADC for digital beamforming applications. In Advances in Intelligent Systems and Computing (Vol. 381, pp. 291–299). https://doi.org/10.1007/978-81-322-2526-3_31.

Palagiri, H., Makkena, M., & Chantigari, K. R. (2013a). Design development & performance analysis of high speed comparator for reconfigurable ΣΔ ADC with 180 nm TSMC technology. In 15th International conference on advanced computing technologies (ICACT 2013).

Palagiri, H. V., Makkena, M. L., & Chantigari, K. R. (2012). Performance analysis of first order digital sigma delta ADC. In 2012 Fourth international conference on computational intelligence, communication systems and networks, Phuket (pp. 435–440). https://doi.org/10.1109/CICSyN.2012.84.

Palagiri, H. V., Makkena, M. L., & Chantigari, K. R. (2013b). Optimum decimation and filtering for reconfigurable sigma delta adc. Far East Journal of Electronics and Communications, 11(2), 101–111.

Sousa, F., Mauer, V., Duarte, N., Jasinski, R. P., & Pedroni, V. A. (2004). Taking advantage of LVDS input buffers to implement sigma-delta A/D converters in FPGAs. In Proceedings of international symposium on circuits and systems, Vancouver, BC, Canada (Vol. 1, pp. 1088–1091).

Szczesny, S., Kropidłowski, M., & Naumowicz, M. (2020). 0.5-V ultra-low-power modulator for sub-NA signal sensing in amperometry. IEEE Sensors Journal, 20(11), 5733–5740.

Vardhini, P. A. H. (2016). Analysis of integrator for continuous time Digital sigma Delta ADC on Xilinx FPGA. In International conference on electrical, electronics, and optimization techniques, ICEEOT 2016 (pp. 2689–2693).

Vasishta, S., Raghunandan, K. R., Dodabalapur, A., & Viswanathan, T. R. (2020). Level-crossing detection based low-power sigma-delta ADC for sensor applications. In 2020 IEEE 63rd international midwest symposium on circuits and systems (MWSCAS), Springfield, MA, USA (pp. 663–666). https://doi.org/10.1109/MWSCAS48704.2020.9184615.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Vardhini, P.A.H., Makkena, M.L. Design and comparative analysis of on-chip sigma delta ADC for signal processing applications. Int J Speech Technol 24, 401–407 (2021). https://doi.org/10.1007/s10772-021-09800-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10772-021-09800-8