Abstract

Large scale Radio Telescopes for Radio Astronomy highly depend on the availability of large (digital) processing capacities for imaging. Estimates concerning power efficiency for future Radio Telescopes lead to anticipated power consumption numbers beyond feasibility. To reduce the power budget, the use of approximate multipliers within the correlator is explored. A baseband equivalent executable model of a radio synthesis telescope is constructed to assess the effects of approximate multipliers. Besides ideal multipliers with floating point accuracy, the use of accurate 8-bit multipliers and 4 different types of approximate multipliers is explored. For each of these multipliers, the energy efficiency of an individual multiplier is known and used to determine the energy efficiency improvement of a correlator when using approximate multipliers. The effects of approximation are quantified by 3 metrics (Signal-to-Noise-Ratio (SNR), Spurious-Free-Dynamic-Range (SFDR) and Root-Mean-Square (RMS) level) derived from maps constructed by the executable model based on an empty sky with only a single point source. This is considered to be the worst case scenario. For illustration purposes, a more realistic input is processed by the model as well. The metrics have been determined based on different SNR levels at the input of each antenna element. For input SNR levels up to 10 dB, all types of approximate multipliers used in this paper can be exploited to improve energy efficiency of correlators, leading to a maximum energy reduction of 19 %. For input SNR values up to 30 dB an energy improvement up to 12 % can be achieved. These percentages are based on implementations in a 40nm low power IC technology at 1 GHz.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Within Radio Astronomy, there is a trend to build Radio Telescopes with larger apertures and baselines to increase sensitivity and spatial resolution. In many cases this is realized by sparse arrays of stations and in many cases, each station consists of a sparse array of antennas. The signals of the individual stations or antennas are combined electronically. For Radio Astronomy imaging, part of the processing is done decentralized (beamforming and correlation) and part is done centralized. Prominent recent examples of this type of systems are the Low Frequency Array LOFAR, [18] and the Square Kilometer Array SKA, [7].

Some quantitative predictions of expected power consumption in the centralized processor of the SKA are presented in [10] where the power consumption is estimated to be 7.9 MW for the correlator. This estimate is based on extrapolation of the power consumption of the correlator for the ALMA telescope [42]. Another estimate that reveals the high power consumption characteristics of the SKA telescope is based on a straw-man design for a baseline correlator for the SKA [8]. Within this design, the total power consumption of the correlator boards is estimated to be 5.2 MW.

High power consumption levels are expected for the the centralized processor of the SKA which are hampering the feasibility of modern radio telescopes. Especially the correlator part is contributing significantly to these high levels of power consumption. Based on that, our research question is formulated: “How can the power consumption of the correlator architectures for modern telescopes be significantly reduced?” Because multipliers are the most power consuming elements within a correlator architecture [11], so-called ‘approximate multipliers’ are introduced as an effective measure to reduce power consumption and required silicon area. In this research, we focus on XF correlators (correlation before Fourier Transform) since complexity within these correlators is dominated by the number of multiplications. For FX correlators (Fourier Transform before correlation), the relative contribution of the number of multiplications to the overall complexity is lower [32]. We therefore expect the largest reduction of power consumption and required silicon area by introducing approximate multipliers within XF correlators.

A model of a radio telescope is mathematically described and based on this model, a simulator of a processing pipeline has been constructed, including different types of approximate multipliers. The simulations reveal e.g. the final Signal-to-Noise-Ratio (SNR), Spurious-Free-Dynamic-Range (SFDR) and RMS level (R) within a map. These metrics are used to assess the effects of approximate multipliers and results are presented for different types of multipliers. As an illustration, the constructed correlator model is used to generate maps based on a realistic sky image. At the end of this paper, conclusions are drawn concerning the applicability of approximate multipliers within Radio Telescopes.

2 Related work

In this section, the evolution of digital correlators within Radio Astronomy is presented, followed by an overview of techniques used to optimize correlator architectures in Radio Astronomy. In the third part of this section, as a candidate for further optimization of modern correlator architectures, an overview of approximate computing techniques is given. Finally, approximate recursive multipliers are discussed.

2.1 Evolution of digital correlators

At the end of the previous century, Application Specific Integrated Circuits (ASICs) were designed as core elements within digital correlators. An example of such an ASIC is the NFRA Correlator chip [4]. For this chip, the resolution of the input data was bounded to 2 bits in order to reduce chip area and power consumption. Furthermore, the programmability was limited and only a small set of configurations was available for Radio Astronomy observations. Besides this, the development of these integrated circuits was time consuming and costly. At the same time, due to developments within integrated circuit technology pushed by Moore’s law, huge general purpose processing capacities became gradually available in the form of General Purpose Processors (GPP’s) and Graphics Processing Units (GPU’s). These devices combine high resolution (fixed point and floating point) with programmability. Furthermore, because the Instruction Set Architectures (ISA’s) of these devices last for multiple hardware generations, hardware- and software development are decoupled, enabling re-use of legacy code (in the ideal case). Using these devices, high performance correlator systems have been constructed based on Commercial-of-the-shelf (COTS) components [6, 29]. However, as already predicted in [3], developments in digital circuit technology indicate that power-efficiency gain due to Moore’s law is diminishing rapidly, in spite of reduced transistor sizes. Consequently, when using GPP’s and GPU’s, power consumption will eventually increase proportionally to processing requirements. So, technology progress is not scaling with the size of the Radio Astronomy facilities anymore and power consumption is becoming a bottleneck in realization of these systems in general and correlators more specifically. For that reason, designing dedicated correlator hardware is still a feasible approach. There are basically two approaches for dedicated correlator hardware: using reconfigurable devices like Field Programmable Gate Arrays (FPGA’s) or dedicated correlator ASIC’s. FPGA’s are positioned between programmable processors and ASIC’s. FPGA’s are general purpose devices but, because of the absence of an ISA, programming an FPGA is more involved than programming e.g. a GPP. Furthermore, the range of applications that is covered by a single FPGA configuration is limited because of the small configuration memories and relatively long (re-)configuration times whereas the range of applications between which a GPP or GPU can switch instantaneously is almost infinite due to extremely large program and cache memories. The advantages of FPGA’s are that they can provide large processing capacities due to spatial distribution of tasks and they offer high I/O bandwidths. Furthermore, tailor-made implementations of these tasks make FPGA’s more energy-efficient than GPP’s and GPU’s. Also within Radio Astronomy, FPGA’s are used to build energy-efficient correlator and beamforming systems [16, 22, 23]. Solutions are also sought in combining different technologies. For the realization of a correlator for SKA low, FPGA technology is combined with network switches where the first is being used for signal processing and the latter for data routing [19]. Furthermore, combinations with GPU’s are also made. Yu et al. [44] list several correlators that have been designed in this way among which correlators for the Long Wavelength Array (LWA) and the Murchison Widefield Array (MWA). However, GPU’s and FPGA’s cannot reach energy-efficiency levels that can be achieved by ASIC implementations. Anghel et al. [2] indicated that ASIC solutions can be 1.6 to 4 times more energy-efficient than FPGA solutions. For that reason ASIC implementations of especially the correlator have again been investigated [11, 35, 40]. To further optimize the energy efficiency of correlators, carefully reconsidering the multipliers within the correlator chips is key.

2.2 Optimization of correlator architectures in radio astronomy

In the past, to optimize correlator architectures, knowledge concerning characteristics of the input signal was exploited. Realistic assumptions at that time were that correlator inputs consist of noise signals with a known (Gaussian) amplitude distribution and that the correlation between inputs from different telescopes is low, or formulated differently, the SNR at the input of the correlator is low. Besides that, no interference was assumed. As a consequence, even in cases of coarse quantization, the quantization noise introduced by two- or even single-bit quantizers is uncorrelated between signals from different telescopes. For that reason, one- and two-bit mutlipliers lead to only a small loss in sensitivity. Energy efficiency can even be further increased by using incomplete multipliers where, for specific combinations of input values, not the exact result of a multiplication is produced but an approximation with the aim of reducing hardware complexity. This leads to an additional small loss in sensitivity. The effects of incomplete multipliers on sensitivity has been studied in [9] and [5]. Incomplete multipliers were used within e.g. the NFRA correlator chip [4]. This way it was possible to integrate 1024 correlator lags within a single chip. Because of the trend of constructing correlators based on COTS components, coarse quantization and the use of incomplete multipliers has fallen out of favor in contemporary processing pipelines. However, since Moore’s law is no longer guaranteeing increasing processing capacities per Watt, research on incomplete multipliers has been revived in the area of ‘approximate computing’ [36]. In most cases, the resolution of these ‘new’ incomplete multipliers is larger than 2 bits (and in most cases multiples of 8 bits). Since modern Radio Telescopes like LOFAR and SKA use beamforming to increase the SNR at the inputs of the correlator it is interesting to investigate the use of multibit approximate multipliers in modern processing pipelines for Radio Astronomy imaging.

An 8-bit recursive multiplier requires four 4-bit multipliers (left), each 4-bit multiplier requires four 2-bit multipliers (right). Therefore, sixteen 2-bit multipliers are required to construct an 8-bit multiplier. Adapted from [15]

2.3 Approximate computing – the state-of-the-art

Approximate computing is an emerging paradigm that introduces approximations at software-, architecture-, and hardware-level to achieve efficiency benefits [37]. Power-efficiency gains have been demonstrated for error-resilient applications such as radio communication, multimedia digital signal processing, machine learning, and scientific computing [1, 20, 43]. In literature, approximate computing is also coined as best-effort computing, as it executes an algorithm on best-effort bases [26]. It trades the accuracy of algorithms as much as bearable to enhance the computing efficiency as much as possible. Another related term is error-efficient computing, originating from the notion that it prevents as many errors as necessary to execute an algorithm in a resource-efficient manner [38] and [37].

A technique often used in approximate computing is circuit pruning. Wherein, logic gates and/or transistors are reduced in number or complexity to achieve efficiency benefits like chip-area and energy-/power-consumption [33]. It is to be noted that only those parts of a circuit are pruned that have a low probability of usage, and therefore, the approximations do not have a high consequence on the overall quality of output.

Adders and multipliers are the important building blocks of digital signal processing architectures. Unsurprisingly, these building blocks have been widely researched in the approximate computing domain. Gupta et al. [17] presented transistor-level pruning for an approximate full adder circuit, which can be utilized to design multi-bit adders. Another technique for approximate adder circuits is the carry propagation chain simplification or reduction of the critical path to reach the overall sum of two inputs [12, 27, 39]. Additionally, reducing the number of carry-propagation bits reduces power consumption related to the glitches produced during the carry propagation [45].

A multiplication operation includes generating partial products and adding them in a specific shift order to achieve the overall product of two input numbers (operands). The approximation techniques for a multiplier include input truncation, partial product truncation, and pruned addition of partial products [14, 21, 31, 34]. Targeting power-efficiency, gate-level pruning is applied to design a 2-bit multiplier [24]. Such multipliers can be used recursively together with adder trees to form a higher-order (n-bit) multiplier.

2.4 Approximate recursive multipliers

Approximate recursive multipliers prune the recursive multiplication structure to reduce the number of gates and the critical path of the circuit. Such multipliers are (especially) known for their power efficiency benefits [24]. Moreover, such multiplier structures are scalable and provide a huge number of possible approximation choices that help in their optimization process based on the input distribution [25] and [34]. In the context of providing guarantees for approximate multiplication, the worst-case error of approximate recursive multipliers has been demonstrated to be smaller than the worst-case error of some of the other approximate approaches like truncation [28]. Keeping in view the benefits of the approximate recursive multipliers, we have utilized them to study the effect of approximate computation in correlator processing. Here we provide the basic knowledge of approximate recursive multipliers.

Truth tables of 2-bit multipliers. A and C are 2-bit inputs having a range of 0 to 3, shown in decimal numbers. Accurate (M) has all the products correct. M1 has only one output approximated (\(3 \times 3 \mapsto 7\) instead of 9) that produces an error of -2 [24]. M2 has three approximated outputs [34], wherein each approximation produces an error of -1 (e.g., \(1 \times 1 \mapsto 0\) instead of 1). M3 is similar to M1, however, it produces an error of +2 to complement M1 [15]. M4 produces an error of -4 while approximating the product (output) for the same combination of inputs, i.e., A=3 and C=3 [13]

To build an n-bit recursive multiplier, four (n/2)-bit sub-multipliers are utilized. Here n is the bit-width of input operands, \(n \in \{4, 8, 16, 32,...\}\). As an example, Fig. 1 illustrates an 8-bit multiplier composed of basic 2-bit multipliers. These 2-bit multipliers generate partial products. The summation of the bit-shifted partial products produces the overall output of an 8-bit recursive multiplier.

Several 2-bit approximate designs have been presented in the literature. The input to output relations (truth tables) of designs used in this paper are shown in Fig. 2. Kulkarni et al. [24] proposed M1 that underestimates one out of the sixteen outputs to improve power-efficiency. It produces an approximate output (7 instead of 9) when both inputs have a value of 3. [34] proposed M2, which reduced the maximum error magnitude to 1 (as compared to 2 in M1). However, M2 increased the error probability to 3/16 (as compared to 1/16 in M1) in case of uniformly distributed inputs. Gillani et al. [15] proposed M3 to introduce a complementary error behavior of M1, i.e., the error produced by M3 is an additive inverse of the error produced by M1. A combination of M1 and M3 within an n-bit multiplier introduces error-cancellation, which improves the quality of the output within accumulation-based algorithms.

Nevertheless, the overestimation in M3 poses a possibility of overflow in n-bit multipliers because it may provide an output higher than that of the exact value. To alleviate the overflow problem while keeping the error cancellation attribute, [13] proposed M4 that underestimates one of the sixteen outputs with a relatively higher error magnitude. Noteworthy, all the approximate 2-bit multipliers (M1, M2, M3, and M4) provide a higher computing efficiency as compared to an accurate 2-bit multiplier.

As shown in Fig. 1, an 8-bit multiplier is composed of sixteen 2-bit multipliers. Any combination of M, M1, M2, M3, and M4 can be utilized to form an 8-bit multiplier. However, the best combinations are chosen based on input distribution and output quality constraints. The following 8-bit designs have been presented in [13]: Acc, Conv2, Conv1, ISH2, and ISH1. The 8-bit Acc multiplier is constructed out of 16 2-bit M multipliers. the Conv designs are based on a combination of M and M1 multipliers whereas the ISH multipliers combine M, M1, M3 and M4 multipliers. The ISH designs are based on the internal-self-healing methodology, which allows higher approximation levels as compared to the conventional methodology (Conv designs) to achieve a higher computing efficiency. For more information, we refer to ([13]). The chip-area and power consumption of the said designs are shown in Table 1. It can be seen that ISH designs provide higher efficiency (lower computing cost) in terms of chip-area and power consumption. The power savings are shown with respect to an accurate 8-bit multiplier (Acc). In Section 4, we will utilize these designs to investigate the feasibility of approximate computing in correlator processing.

3 Model

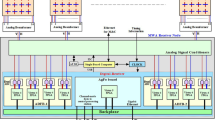

To assess the effects of approximate multipliers in the correlator of a processing pipeline for Radio Astronomy imaging, a simplified baseband-equivalent mathematical description of an interferometer is constructed. This mathematical description serves as a basis for an executable model in Matlab in which a model of the sky serves as an input and a map is generated as output. Different types of approximate multipliers can be used within the correlator model. Based on the output map, quality metrics are defined that are used to assess the effect of different types of multipliers.

As an example, in Fig. 3, a global overview of the model of a 4x4 interferometer is presented. Antennas are located on a regular square grid. Furthermore, a Reference Antenna is positioned in the middle of the array. A single point source, modeled with a white Gaussian distribution is assumed. Receiver noise is modelled as additive white Gaussian noise at each antenna. The output of the model is a map which is used to determine three evaluation criteria: Signal-to-Noise-Ratio (SNR), Spurious-Free-Dynamic-Range (SFDR) and Root-Mean-Square (RMS) noise level in the map. Below, a formal description of the model and the evaluation criteria are given.

The antennas are placed on a grid with \(\frac{1}{2} \lambda \) spacing. The signals from each antenna are correlated with the signal originating from the Reference Antenna that is placed in the middle of the grid. A complex signal representation is used and each complex correlator is calculating the zero-lag of the crosscorrelation function. The outputs of the complex correlators are fed into a two-dimensional Fast Fourier Transform (2D-FFT) to produce a map. The structure of a complex correlator is presented in Fig. 4.

For both inputs of the correlator, a complex signal representation is used (Re() and Im()). Both the real and imaginary part are represented as floating point numbers and are considered as analog signals that need to be converted into the digital domain before digital multiplication. To optimally exploit the dynamic range of the Analog-to-Digital Converters (ADCs), Automatic-Gain-Control (AGC) is adapting the input signal such that the RMS level is a constant fraction of the maximum input amplitude of the ADC. To avoid clipping to a large extent, within this paper the RMS level is positioned at \(\frac{1}{5}\) th of the maximum amplitude. The RMS levels are used for de-normalization purposes in a later stage. The signal is converted from the analog (read: floating point) domain into the digital domain (read: represented by a limited number of equidistant values). In this paper the output of an ADC consists of 9 bits in a sign-magnitude representation. After analog to digital conversion the complex multiplication is realized by means of 4 approximate real multipliers. Each multiplier calculates the sign of the product based on the sign bits of the inputs and the magnitudes are multiplied by an 8 bit approximate multiplier. The outputs of a multipliers are integrated for a specific number of products and after the summing stage, the resulting values are denormalized with the standard deviations of the two correlated signals, measured by the AGC.

For a general, formal description of the model we define a two dimensional square aperture plane with \(A^2\) antennas where A is assumed to be even. An antenna element is defined by the tuple (p, q) where

The set of tuples \((u_p,v_q)\) defines a two-dimensional grid in the uv-plane where each value gives the coordinate of antenna element (p, q) relative to the reference antenna at (0, 0), measured in wavelength \(\lambda \).

The set of tuples (l, m) defines a two-dimensional grid in the source plane where

\((l_s,m_s)\) is the position of a single point source in the source plane. A source is assumed to be positioned exactly on the grid within the source plane. The phase difference between the signal received at the reference antenna and the signal received at antenna (p, q) equals \(\theta _{p,q}=2 \pi (u_p l_s + v_q m_s)\). Note that we use the narrowband assumption which implies that a time-delay can be modelled as a phase shift.

The signal at the output of each antenna consist of a noise- and a source component. The noise component is independent for each antenna having a complex Gaussian distribution. The noise components at time t are defined as \(n_{p,q,t} \sim \mathcal {C}\mathcal {N}(0,1)\). The source component, also with a complex Gaussian distribution, is defined as \(s_t \sim \mathcal {C}\mathcal {N}(0,1)\). Finite series of T samples are defined as \(n_{p,q} = [n_{p,q,0}, n_{p,q,1}..., n_{p,q,T-1}]\) and \(s = [s_0, s_1,..., s_{T-1}]\).

Each individual antenna receives a phase shifted version of the source component: \(x_{p,q} = \textrm{e}^{j \theta _{p,q}} \cdot s\). After addition of the noise, the input of the complex correlator can be written as

where \(\mathrm {SNR_{in}}\) defines the ratio of the standard deviations of the source- and noise components. \(\mathrm {SNR_{in}}\) is equal for all antennas. After normalization by the AGC and quantization by a mid-treat ADC, the complex valued digital signals are described as

The correlator output or Visibility Function is then described as

where \(\otimes \) indicates the complex innerproduct using approximate multipliers, \('\) the complex conjugate transpose operation, and \(\sigma _{y_{p,q}}\) and \(\sigma _{s}\) are the complex standard deviations of \(y_{p,q}\) and s respectively. Consequently, the number of values integrated within the correlator equals T. The Brightness Distribution (M) is calculated by means of a 2-dimensional Fast Fourier Transform (2DFFT) on the Visiblity Function:

In Fig. 5a, an example of a map based on a simulation with 16 x 16 antennas is presented. In this case, an input SNR of \(\mathrm {SNR_{in}}\) = 10 dB and ideal multipliers are used. A single source is located at \((l_s,m_s) = (\frac{1}{8}, \frac{5}{8})\). The map is generated by a Matlab implementation of the model defined by expressions (1) to (11). Because the source is positioned exactly on the grid within the source plane, all energy is confined into a single point in the final Brightness Distribition M. In case of a non-ideal (non-linear) correlator, source energy will be spread over other points within the Brightness Distribution as well. To assess the quality of the map produced by the model described above, three metrics are defined: \(\mathrm {SNR_{dB}}\), \(\mathrm {SFDR_{dB}}\) and \(\mathrm {R_{dB}}\). Their definition is explained below. To determine the metrics, four different values that are distilled from M are defined: the power at the calculated position of the point source \(S_M\), the sum of the power values of all the other points \(N_M\) which ideally consists of only noise contributions but might also contain spurious components due to instrumental effects, the largest component in the map besides the source signal \(P_M\) and the RMS level over all other points in the map (\(R_M\)).

To calculate the RMS level of the noise contributions in the map, the following is defined

The final Signal-to-Noise-Ratio \(\mathrm {SNR_{dB}}\), Spurious Free Dynamic Range \(\mathrm {SFDR_{dB}}\) and RMS level \(\mathrm {R_{dB}}\) on dB scale are then defined as

4 Results

In Fig. 5b the same system setup as for Fig. 5a is used where the ideal multipliers are replaced by ISH1 multipliers. Within these maps, the point source is clearly visible. For all other points in the map, power levels are much lower (more than 35 dB).

To assess the quality of the maps for different approximate multipliers, Monte Carlo simulations have been done using the same setup as for Fig. 5 and the performance metrics, defined in the previous section have been determined. To explore the dependency of the performance metrics \(\mathrm {SNR_{dB}}\), \(\mathrm {SFDR_{dB}}\) and \(\mathrm {R_{dB}}\) on the SNR at the input of each antenna, simulations for a large SNR input range (from -20 to +40 dB) are conducted. All simulation results are averaged over 25 simulation runs. To have manageable simulation times, the number of samples to be integrated within a single run T is relatively small. Simulation results are based on \(T = 64\) for the following multiplier architectures: ideal, accurate (Acc), Conventional 1 (Conv1), Conventional 2 (Conv2), Internal Self Healing 1 (ISH1) and Internal Self Healing 2 (ISH2) multipliers. For the ideal and ISH1 multiplier architectures, simulations are done for \(T = 256\) and \(T=1024\) as well. The results for \(\mathrm {SNR_{dB}}\) are presented in Fig. 6.

Figure 6 shows that up to an input SNR of approximately 10 dB, all architectures give similar performance where an increased \(\mathrm {SNR_{in}}\) leads to an increased \(\mathrm {SNR_{dB}}\). Beyond 10 dB the curves for the non-ideal multiplier architectures deviate from the ideal curve. The largest deviation is seen for the ISH1 curve. This deviation is caused by quantization and clipping by the ADC, and approximation within the multiplier.

In Fig. 7, the distribution of the 25 simulations is presented for the ideal- and ISH1 cases, a limited \(\mathrm {SNR_{in}}\) range (5-25 dB) and \(T=1024\). For an \(\mathrm {SNR_{in}}<\) 10 dB, the two distributions are overlapping. For \(\mathrm {SNR_{in}} \ge \) 10 dB the SNR values for ISH1 case spread over a larger \(\mathrm {SNR_{dB}}\) range, due to the approximation within the ISH1 multipliers.

To analyse the effects that can be observed in Figs. 6 and 7, first the effects introduced by the ADC are analysed. According to [41] the quantization noise is uncorrelated with the input signal if the RMS level of the noise added to the input signal is larger than the quantization step size. In case the RMS level of the noise is smaller than the quantization step size, the quantization noise between the different antennas becomes correlated and higher \(\mathrm {SNR_{in}}\) does not lead to higher \(\mathrm {SNR_{dB}}\). In case of the accurate multiplier and \(5 \sigma \)-clipping, the quantization noise is uncorrelated up to approximately 30 dB. In Fig. 6, the curve for the accurate multiplier indeed starts to deviate from the ideal curve in case \(\mathrm {SNR_{in}}>\) 30 dB. All other multiplier schemes show similar behavior except for ISH1 where the curve starts to deviate beyond 10 dB which is due to the coarser approximation within this multiplier. Because of this, using the ISH1 scheme is considered to be the worst case scenario and is therefore used to further investigate the effect of longer integration lengths, using 256 and 1024 samples. Quadrupling the integration length should lead to an improvement of \(\mathrm {SNR_{dB}}\) by 6 dB which can indeed be seen from Fig. 6 for \(\mathrm {SNR_{in}}<\) 10 dB. Beyond this limit, increasing the integration length does not increase \(\mathrm {SNR_{dB}}\) because of the correlation of noise introduced by quantization and the approximation. Another important observation is that, for \(\mathrm {SNR_{in}}<\) 10 dB, \(\mathrm {SNR_{dB}}\) is not significantly affected by the approximation in ISH1.

Simulation results for the Spurious Free Dynamic Range (\(\mathrm {SFDR_{dB}}\)) and the RMS noise level (\(\mathrm {R_{dB}}\)) are presented in Figs. 8 and 9 respectively.

For the Spurious Free Dynamic Range (\(\mathrm {SFDR_{dB}}\)), similar effects as for \(\mathrm {SNR_{dB}}\) can be observed. However, the effects of approximation are more emphatically present. For the accurate, Conv1 and Conv2 multipliers the \(\mathrm {SFDR_{dB}}\) starts to deviate from ideal values beyond 30 dB. The coarser approximation by the ISH2 multiplier leads to deviations beyond 20 dB and ISH1 leads to deviations beyond 10 dB. But, also for \(\mathrm {SFDR_{dB}}\), the performance is not significantly affected for \(\mathrm {SNR_{in}}<\) 10 dB when increasing integration lengths.

Figure 9 presents the RMS level of the noise within the map as a function of \(\mathrm {SNR_{in}}\) for the same cases as described above. For the ideal multiplier, the \(\mathrm {SNR_{in}}\) domain can be roughly divided into two parts. Up to -10 dB, increasing \(\mathrm {SNR_{in}}\) hardly improves \(\mathrm {R_{dB}}\) because noise is dominating the input signals at the antennas. Beyond -10 dB, increasing \(\mathrm {SNR_{in}}\) leads to reduced RMS levels in the map. In case of using the accurate or one of the approximate multipliers, increasing \(\mathrm {SNR_{in}}\) eventually leads to correlated quantization noise which results in diminishing returns with respect to \(\mathrm {R_{dB}}\). This effect is strongest in case of the ISH1 approximate multiplier. Beyond 10 dB, increasing \(\mathrm {SNR_{in}}\) does not lead to lower \(\mathrm {R_{dB}}\). Furthermore, up to \(\mathrm {SNR_{in}}\) = 10 dB, the RMS level in the map is reduced with 3 dB when quadrupling the integration length for all multiplier architectures.

Based on Figs. 6, 8 and 9, we conclude that, for \(\mathrm {SNR_{in}}<\) 10 dB, the performance of all approximate multipliers is similar to the performance of the accurate multiplier for relatively small integration lengths. To explore the effects of approximate multipliers in case of longer integration lengths, simulations are done for the ISH1 multiplier and \(\mathrm {SNR_{in}} =\) 0 dB. ISH1 was chosen because in this design, the effects of approximation are most prominent.

The results of these simulations are displayed in Table 2.

From Table 2 it is seen that also for longer integration lengths, \(\mathrm {SNR_{dB}}\) and \(\mathrm {SFDR_{dB}}\) increase with approximately 3 dB when quadrupling the integration length and \(\mathrm {R_{dB}}\) reduces with approximately 3 dB when quadrupling the integration length.

Part of the map “the dancing ghosts” from [30] that is used to generate the received antenna signals

Map that is created using a correlator with ISH1 multipliers. SNR = 0 dB, T = 256 samples. The scale is normalized based on the maximum value within the map of Fig. 11

To evaluate the effects of approximate multipliers using more realistic data, the model described above has been extended to a square array of 128 by 128 antennas (A = 128). Consequently, the source plane consists of a 128 x 128 grid as well. As a model, a 128 x 128 pixel part of the sky from “the dancing ghosts” image from [30] has been used where a pixel of the sky map is used as a single point source where the power of a point source is determined by the intensity in the map (linear scale). Based on the 128 x 128 point sources, the resulting signal at each individual antenna element has been determined. The SNR at each antenna element was set at 10 dB and maps have been generated in case of a correlator based on ideal 8-bit multipliers and in case of a correlator based on ISH1 multipliers. Results have been obtained by integration over 16K samples. In Fig. 10 the original noise-free part of the sky is presented. The map has been normalized with the maximum value in the map and noise has been added (10 dB SNR). Figure 11 gives the resulting map in case of a correlator with ideal 8-bit multipliers, and Fig. 12 gives the resulting map in case of a correlator with ISH1 multipliers. Both maps are normalized with the maximum value in the map based on ideal multipliers (Fig. 11). Figure 13 presents the difference between the maps in Figs. 11 and 12.

Visual inspection of Figs. 11 and 12 shows that artefacts introduced by quantization (Fig. 11) and approximate multiplication (Fig. 12) are below the sky noise. Furthermore, the difference between the two maps is smaller than \(1.5 10^{-2}\) and as expected, the variance in areas with higher intensity is larger.Also, no artefacts are observed.

5 Conclusion

In order to find the answer to the research question “How can the power consumption of the correlator architectures for modern telescopes be significantly reduced?”, the use of approximate multipliers within the correlator of signal processing pipelines for modern Radio Telescopes has been investigated. Approximate multipliers produce results with reduced precision compared to accurate multipliers. The benefit is that these multipliers are smaller (occupy less area on an integrated circuit) and consume less energy per multiplication. The next question that is addressed in this paper is then “How does the reduced precision affect the quality of the maps that are produced using a correlator with approximate multipliers?”. To quantify the effects on the quality of the map, 3 performance metrics have been defined: Signal-to-Noise-Ratio (\(\mathrm {SNR_{dB}}\)), Spurious-Free-Dynamic-Range (\(\mathrm {SFDR_{dB}}\)) and Root-Mean-Square noise level (\(\mathrm {R_{dB}}\)) in the map. A simulation model has been constructed based on an array of 16 by 16 antennas and a single point source. Besides the reference case (no quantization, ideal multipliers), the use of 5 different types of multipliers has been simulated. Besides an accurate 8-bit multiplier, 4 approximate multipliers are analysed. Based on the simulations, the following conclusions can be drawn:

-

Up to 10 dB \(\textrm{SNR}\) at the input of the individual antennas, there is no (noticeable) effect introduced by the approximate multipliers that have been used in this paper. This is illustrated for the ISH1 approximate multiplier which was identified as the worst case.

-

Approximation leads to noise correlation. Different approximate multipliers exhibit different levels of noise correlation. The maximum \(\mathrm {SNR_{in}}\) at which approximation does not lead to noise correlation differs for different approximate multipliers. Out of the set of approximate multipliers that have been investigated the best performing ones (Conv1 and Conv2) introduce no (noticable) effects up to \(\mathrm {SNR_{in}}\) = 30 dB.

-

Significant power reduction can be achieved by exploiting approximate multipliers. When using the approximate multiplier ISH1 which can be used up to 10 dB input SNR, 19% energy can be saved compared to using accurate multipliers. When using Conv1 which can be used up to 30 dB input SNR, 12% energy can be saved.

The analysis in this paper uses 8-bit multipliers as a starting point. The results indicate that, as long as the SNR at the input of the correlator is low, more aggressive approximation could be applied, leading to even higher energy savings. To further improve energy efficiency of correlators, it is interesting to investigate flexible multiplier architectures where the type of multiplier can be matched with the SNR at the input. In case of low SNR, a multiplier exploiting aggressive approximation can significantly reduce power consumption. In high SNR scenarios, more accurate multipliers are required leading to relatively high levels of power consumption. Being able to chose the optimal multiplier when configuring the correlator will lead to significant lower energy consumption when considering multiple, different observations. Related to this, it is interesting to investigate how to exploit the concepts of approximate computing when using Field Programmable Gate Array (FPGA) boards to realize correlators. In this paper, ASIC implementations of multipliers are used. However, these implementations do not map optimally onto the basic blocks of FPGA’s. For that reason a bottom-up approach should be used where FPGA basic blocks are used to construct approximate multipliers which can lead to significant energy savings when using FPGA’s. Furthermore, the aim is to further exploit the approximate computing paradigm within other parts of the signal processing chain besides the correlator, to increase energy efficiency.

Availability of data and materials

Code and data are available from the corresponding author on reasonable request

References

Airoldi, R., Campi, F., Nurmi, J.: Approximate computing for complexity reduction in timing synchronization. EURASIP J. Adv. Signal Process. 2014(1), 1–7 (2014)

Anghel, A., Jongerius, R., Dittmann, G., Weiss, J., Luijten, R.P.: Holistic power analysis of implementation alternatives for a very large scale synthesis array with phased array stations. In: 2014 IEEE International conference on acoustics, speech and signal processing (ICASSP), pp. 5397–5401. (2014)

Borkar, S., Chien, A.A.: The future of microprocessors. Commun. ACM 54(5), 67–77 (2011)

Bos, A.: A high speed 2-bit correlator chip for radio astronomy. IEEE Trans. Instrum. Meas. 40(3), 591–595 (1991)

Bowers, FK., Klingler, R.: Quantization noise of correlation spectrometers. In: Astronomy and astrophysics supplement series vol. 15, p. 373 (1974)

Broekema, P.C., Mol, J.J.D., Nijboer, R., van Amesfoort, A.S., Brentjens, M.A., Loose, G.M., Klijn, W.F.A., Romein, J.W.: Cobalt: A GPU-based correlator and beamformer for LOFAR. In: Astronomy and Computing vol. 23, pp. 180–192 (2018). https://www.sciencedirect.com/science/article/pii/S2213133717301439. ISSN 2213-1337

Carilli, C., Rawlings, S.: Science with the Square Kilometer Array: Motivation, key science projects, standards and assumptions. (2004). arXiv preprint astro-ph/0409274

Carlson, B.: The Giant Systolic Array (GSA): Straw-man Proposal for a Multi-Mega Baseline Correlator for the SKA. (2010). https://www.skatelescope.org/uploaded/14974_127_Memo_Carlson.pdf. Square Kilometre Array Memo 127

Cooper, B.F.C.: Correlators with two-bit quantization. Aust J Phys 23, 521–527 (1970)

D’Addario, L.: Low-Power Correlator Architecture for the MidFrequency SKA (2011). http://www.skatelescope.org/pages/page_memos.htm. Square Kilometre Array Memo 133

D’Addario, L.R., Wang, D.: An integrated circuit for radio astronomy correlators supporting large arrays of antennas. J. Astron. Instrum. 5(02), 1650002 (2016)

Echavarria, J., Wildermann, S., Becher, A., Teich, J., Ziener, D.: Fau: Fast and error-optimized approximate adder units on lut-based fpgas. In: 2016 International conference on field-programmable technology (FPT) IEEE (Veranst.), pp. 213–216 (2016)

Gillani, G.A., Hanif, M.A., Verstoep, B., Gerez, S.H., Shafique, M., Kokkeler, A.B.: MACISH: Designing approximate MAC accelerators with internal-self-healing. IEEE Access 7, 77142–77160 (2019)

Gillani, G.A., Krapukhin, A., Kokkeler, A.B.: Energy-efficient approximate least squares accelerator: a case study of radio astronomy calibration processing. In: Proceedings of the 16th ACM international conference on computing frontiers, pp. 358–365 (2019)

Gillani, G.A., Hanif, M.A., Krone, M., Gerez, S.H., Shafique, M., Kokkeler, A.B.J.: SquASH: Approximate square-accumulate with self-healing. IEEE Access 6, 49112–49128 (2018)

Guo, S., Zheng, L., Jin, X.: Accelerating a radio astronomy correlator on FPGA. In: 2018 20th International conference on advanced communication technology (ICACT), pp. 85–89 (2018)

Gupta, V., Mohapatra, D., Raghunathan, A., Roy, K.: Low-power digital signal processing using approximate adders. IEEE Trans. Comput. Aided Des. Integr. Circ. Syst. 32(1), 124–137 (2012)

van Haarlem, M.P., Wise, M.W., Gunst, A.W., Heald, G., McKean, J.P., Hessels, J.W., de Bruyn, A.G., Nijboer, R., Swinbank, J., Fallows, R.u. a.: LOFAR: The low-frequency array. Astron Astrophys 556, A2

Hampson, G.A., Bunton, J.D., Humphrey, D., Bengston, K.J., Jourjon, G., Bolin, A.B., Chen, Y., Troup, E.R., Babich, G.C., Aardt, J.C.V.: Square Kilometre Array Low Atomic commercial off-the-shelf correlator and beamformer. J. Astron. Telescopes Instrum. Syst. 8(1), 011018 (2022). https://doi.org/10.1117/1.JATIS.8.1.011018

Hanif, M.A., Shafique, M.: A cross-layer approach towards developing efficient embedded deep learning systems. Microprocess. Microsyst. 103609 (2021)

Hashemi, S., Bahar, R.I., Reda, S.: DRUM: A dynamic range unbiased multiplier for approximate applications. In: 2015 IEEE/ACM International conference on computer-aided design (ICCAD) IEEE (Veranst.), pp. 418–425 (2015)

Kamp, W., Abel, N., Comoretto, G.: Complex Multiply Accumulate Cells for the Square Kilometre Array Correlators. In: 2018 International conference on ReConFigurable computing and FPGAs (ReConFig), pp. 1–6 (2018)

Kooistra, E., Hampson, G.A., Gunst, A.W., Bunton, J.D., Schoonderbeek, G.W., Brown, A.: Gemini FPGA hardware platform for the SKA low correlator and beamformer. In: 2017 XXXIInd General assembly and scientific symposium of the international union of radio science (URSI GASS) IEEE (Veranst.), pp. 1–4 (2017)

Kulkarni, P., Gupta, P., Ercegovac, M.: Trading accuracy for power with an underdesigned multiplier architecture. In: 2011 24th Internatioal conference on VLSI design IEEE (Veranst.), pp. 346–351 (2011)

Mazahir, S., Hasan, O., Hafiz, R., Shafique, M.: Probabilistic error analysis of approximate recursive multipliers. IEEE Trans. Comput. 66(11), 1982–1990 (2017)

Meng, J., Chakradhar, S., Raghunathan, A.: Best-effort parallel execution framework for recognition and mining applications. In: 2009 IEEE International symposium on parallel & distributed processing IEEE (Veranst.), pp. 1–12 (2009)

Miao, J., He, K., Gerstlauer, A., Orshansky, M.: Modeling and synthesis of quality-energy optimal approximate adders. In: Proceedings of the international conference on computer-aided design, pp. 728–735 (2012)

Mrazek, V., Vasicek, Z., Sekanina, L., Jiang, H., Han, J.: Scalable construction of approximate multipliers with formally guaranteed worst case error. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 26(11), 2572–2576 (2018)

van Nieuwpoort, R.V., Romein, J.W.: Correlating radio astronomy signals with many-core hardware. Int. J. Parallel Prog. 39(1), 88–114 (2011)

Norris, R.P., Marvil, J., Collier, J.D., Kapińska, A.D., O’Brien, A.N., Rudnick, L., Andernach, H., Asorey, J., Brown, M.J., Brüggen, M.u.a.: The Evolutionary Map of the Universe pilot survey. In: Publications of the astronomical society of Australia 38 (2021)

Prabakaran, B.S., Rehman, S., Hanif, M.A., Ullah, S., Mazaheri, G., Kumar, A., Shafique, M.: DeMAS: An efficient design methodology for building approximate adders for FPGA-based systems. In: 2018 Design, automation & test in Europe conference & exhibition (DATE) IEEE (Veranst.), pp. 917–920 (2018)

Rajan, R.T., Bentum, M., Gunst, A., Boonstra, A.-J.: Distributed correlators for interferometry in space. In: 2013 IEEE Aerospace conference, pp. 1–9 (2013)

Reda, S., Shafique, M.: Approximate Circuits. Springer, Cham (2019)

Rehman, S., El-Harouni, W., Shafique, M., Kumar, A., Henkel, J., Henkel, J.: Architectural-space exploration of approximate multipliers. In: 2016 IEEE/ACM International conference on computer-aided design (ICCAD) IEEE (Veranst.), pp. 1–8 (2016)

Schmatz, M.L., Jongerius, R., Dittmann, G., Anghel, A., Engbersen, T., van Lunteren, J., Buchmann, P.: Scalable, efficient ASICS for the square kilometre array: From A/D conversion to central correlation. In: 2014 IEEE International conference on acoustics, speech and signal processing (ICASSP), pp. 7505–7509 (2014)

Shalf, J.M., Leland, R.: Computing beyond Moore’s Law. Computer 48(12), 14–23 (2015)

Stanley-Marbell, P., Alaghi, A., Carbin, M., Darulova, E., Dolecek, L., Gerstlauer, A., Gillani, G., Jevdjic, D., Moreau, T., Cacciotti, M.u.a.: Exploiting Errors for Efficiency: A Survey from Circuits to Applications. ACM Comput. Surv. (CSUR) 53(3), 1–39 (2020)

Stanley-Marbell, P., Rinard, M.: Error-efficient computing systems. (2017)

Verma, A.K., Brisk, P., Ienne, P.: Variable latency speculative addition: A new paradigm for arithmetic circuit design. In: Proceedings of the conference on design, automation and test in Europe, pp. 1250–1255 (2008)

Vermij, E., Fiorin, L., Hagleitner, C., Bertels, K.: Exascale Radio Astronomy: Can We Ride the Technology Wave? In: Kunkel, J.M., Ludwig, T., Meuer, H.W. (eds.) Supercomputing. Cham, Springer International Publishing, pp. 35–52 (2014). ISBN 978-3-319-07518-1

Widrow, B., Kollar, I., Liu, M.-C.: Statistical theory of quantization. IEEE Trans. Instrum. Meas. 45(2), 353–361 (1996)

Wootten, A., Thompson, A.R.: The Atacama Large Millimeter/Submillimeter Array. Proc. IEEE 97(8), 1463–1471 (2009)

Xu, Q., Mytkowicz, T., Kim, N.S.: Approximate computing: A survey. IEEE Des. Test 33(1), 8–22 (2015)

Yu, W., Romein, J.W., Dursi, L.J., Lu, R-S., Pope, A., Callanan, G., Pesce, D.W., Blackburn, L., Merry, B., Srinivasan, R., Kim, J., Weintroub, J.: Prospects of GPU Tensor Core Correlation for the SMA and the ngEHT. Galaxies 11(1), (2023). https://www.mdpi.com/2075-4434/11/1/13. ISSN 2075-4434

Zhu, N., Goh, W.L., Zhang, W., Yeo, K.S., Kong, Z.H.: Design of low-power high-speed truncation-error-tolerant adder and its application in digital signal processing. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 18(8), 1225–1229 (2009)

Acknowledgements

This work is a follow-up on the work done within the IMPEDRA project which was supported in part by the ASTRON and IBM Joint Project, DOME, through the Netherlands Organization for Scientific Research.

Author information

Authors and Affiliations

Contributions

The research and paper writing was a joint effort by A.B.J. Kokkeler and G.A. Gillani in consultation with A.J. Boonstra. The contributions by A.B.J. Kokkeler were mainly w.r.t. to the modeling of the interferometer and simulation of the effects whereas the approximate multipliers and their power consumption have been researched by G.A. Gillani. Figures 1 and 2 were made by G.A. Gillani, Figures 3-13 were made by A.B.J. Kokkeler. A.J. Boonstra provided the Radio Astronomy context and input concerning the performance metrics. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing interest

The authors have no competing interests as defined by Springer, or other interests that might be perceived to influence the results and/or discussion reported in this paper

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Kokkeler, A.B.J., Gillani, G.A. & Boonstra, A.J. Modeling the effects of power efficient approximate multipliers in radio astronomy correlators. Exp Astron 57, 11 (2024). https://doi.org/10.1007/s10686-024-09921-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10686-024-09921-3