Abstract

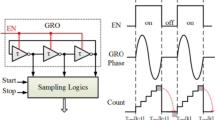

This paper comprehensively reviews the evolution and latest advancement of ultra-low All-Digital Phase Locked Loop (ADPLL) RF transceivers designed specifically for biomedical monitoring devices. With CMOS technology, these transceivers provide efficiency and simplicity, which are essential in the medical industry. As the size and power needs of these devices decrease due to CMOS scaling, they become more suitable for small and low-energy applications. In addition, this review also provides an insight into the ADPLL applications, Digital Controlled Oscillator (DCO), and Phase Frequency Detectors. The review highlights notable differences in performance between time-to-digital converters (TDC) and TDC-less designs. TDC-less design, like Digital Phase Frequency Detectors (DPFD), offers improvements in phase noise, small size, fast phase and frequency acquisition, and power efficiency at the expense of resolution. Comparing LC-DCO and ring-DCO revealed that at high operating frequencies, the ring-DCO consumes more power but has a simpler design and a smaller circuit area than LC-DCO. Future research should focus on enhancing the performance of the ADPLL RF transceiver for biomedical devices, specifically by using a low-voltage supply and implementing DPFD to achieve low power consumption, compact design and fast locking. The significant challenges remain in maintaining low power consumption at higher frequencies with Ring-DCO design. Using the Verilog HDL for ADPLL design and implementation provides modularity, simulation, synthesis, and flexibility, which makes it an excellent alternative to designing RF transceivers in biomedical applications which are efficient and reliable.

Similar content being viewed by others

References

Hu, P. (2020). IoT-based contact tracing systems for infectious diseases: Architecture and analysis. In: Globecom 2020–2020 Ieee Global Communications Conference, (pp. 1–7). IEEE. https://doi.org/10.1109/GLOBECOM42002.2020.9347957

Bradley, P. D. (2006 ).An ultra low power, high performance Medical Implant Communication System (MICS) transceiver for implantable devices. In: 2006 IEEE Biomedical Circuits and Systems Conference, (pp. 158–161). IEEE. https://doi.org/10.1109/BIOCAS.2006.4600332

Li, W., Duan, Y., & Rabaey, J. (2019). A 200-Mb/s energy efficient transcranial transmitter using inductive coupling. IEEE Transactions on Biomedical Circuits and Systems, 13(2), 435–443. https://doi.org/10.1109/TBCAS.2018.2889802

Rahaman, D. M. M., Shabiul Is, Md., Sampe, J., & Md Ali, S. H. (2014). An architecture of ULP energy harvesting power conditioning circuit using piezoelectric transducer for wireless sensor network: A review. Asian Journal of Scientific Research, 8(1), 1–13. https://doi.org/10.3923/ajsr.2015.1.13

Yunus, N.H.M, Sampe, J. Yunas, J., & Pawi, A. (2017). Parameter design of microstrip patch antenna operating at dual microwave-band for RF energy harvester application. In: 2017 IEEE regional symposium on micro and nanoelectronics (RSM), (pp. 92–95). IEEE. https://doi.org/10.1109/RSM.2017.8069128

Copani, T., et al. (2011). A CMOS low-power transceiver with reconfigurable antenna interface for medical implant applications. IEEE Transactions on Microwave Theory and Techniques, 59(5), 1369–1378. https://doi.org/10.1109/TMTT.2011.2116036

Balikai, V., & Kittur, H. (2021). A CMOS implementation of controller based all digital phase locked loop (ADPLL). Circuit World, 47(1), 71–85. https://doi.org/10.1108/CW-11-2019-0184

Gunda, S., ER, R. S., Hemalatha, B., & Divya, C. (2019). DESIGN and simulation of digitally controlled oscillator of ADPLL. International Journal of Advanced Scientific Technologies in Engineering and Management Sciences, 5(3), 1.

Bae, J., Radhapuram, S., Jo, I., Kihara, T., & Matsuoka, T. (2015). A low-voltage design of controller-based ADPLL for implantable biomedical devices. In: 2015 IEEE biomedical circuits and systems conference (BioCAS), (pp. 1–4). IEEE. https://doi.org/10.1109/BioCAS.2015.7348405

Maniam, G., Sampe, J., Jaafar, R., & Ibrahim, M. F. (2022). Smart monitoring system for chronic kidney disease patients based on fuzzy logic and IoT. International Journal of Advanced Computer Science and Applications. https://doi.org/10.14569/IJACSA.2022.0130238

Hemel, M.S.K, Hossain, Md. R., Amin, S., Reaz, M. B. I., Bhuiyan, M. A. S., & Miraz, M. H. (2022) Ring oscillator design in 50 nm CMOS technology for iot based remote infectious disease monitoring system. In: 2022 International conference on computing, electronics & communications engineering (iCCECE), (pp. 17–20). IEEE. https://doi.org/10.1109/iCCECE55162.2022.9875091.

Botsis, T., Bellika, J. G., & Hartvigsen, G. (2009). New directions in electronic disease surveillance: detection of infectious diseases during the incubation period. In: 2009 International conference on eHealth, telemedicine, and social medicine, (pp. 176–183). IEEE. https://doi.org/10.1109/eTELEMED.2009.9.

Badal, T. I., Alam, J. Reaz, M. B. I., Bhuiyan, M. A. S., & Jahan, N. A. (2019). High-resolution time to digital converter in 0.13 µM CMOS process for RFID phase locked loop.

Wang, Y. L., Wang, G. T., & Liu, W. J. (2011). Design and implementation of the RF front-end all-digital phase-locked loop in the UHF RFID reader. Key Engineering Materials, 474–476, 63–68. https://doi.org/10.4028/www.scientific.net/KEM.474-476.63

Ishak, S. N., Sampe, J., Yusoff, Z., & Faseehuddin, M. (2022). All-digital phase locked loop (ADPLL) topologies for RFID system application: A review. Jurnal Teknologi, 84(1), 219–230. https://doi.org/10.11113/jurnalteknologi.v84.17123

Cheng, K.-H., Liu, J.-C., & Huang, H.-Y. (2012). A 0.6-V 800-MHz all-digital phase-locked loop with a digital supply regulator. IEEE Transactions on Circuits and Systems II: Express Briefs, 59(12), 888–892. https://doi.org/10.1109/TCSII.2012.2231021

Ramaswami Palaniappan, A., & Siek, L. (2019). A TDC-less all-digital phase locked loop for medical implant applications. Microprocessors and Microsystems. https://doi.org/10.1016/j.micpro.2019.06.008

Chung, C.-C., & Lee, C.-Y. (2003). An all-digital phase-locked loop for high-speed clock generation. IEEE Journal of Solid-State Circuits, 38(2), 347–351. https://doi.org/10.1109/JSSC.2002.807398

Chung, C.-C., & Ko, C.-Y. (2011). A fast phase tracking ADPLL for video pixel clock generation in 65 nm CMOS technology. IEEE Journal of Solid-State Circuits, 46(10), 2300–2311. https://doi.org/10.1109/JSSC.2011.2160789

Kratyuk, V., Hanumolu, P. K., Moon, U. K., & Mayaram, K. (2007). A design procedure for all-digital phase-locked loops based on a charge-pump phase-locked-loop analogy. IEEE Transactions on Circuits and Systems II: Express Briefs, 54(3), 247–251. https://doi.org/10.1109/TCSII.2006.889443

Wei, C.-L., & Liu, S.-I. (2016). A digital PLL using oversampling delta-sigma TDC. IEEE Transactions on Circuits and Systems II: Express Briefs, 63(7), 633–637. https://doi.org/10.1109/TCSII.2016.2530904

Chen, M.S.-W., Su, D., & Mehta, S. (2010). A calibration-free 800 MHz fractional-N digital PLL with embedded TDC. IEEE Journal of Solid-State Circuits, 45(12), 2819–2827. https://doi.org/10.1109/JSSC.2010.2074950

Lee, I.-T., Zeng, K.-H., & Liu, S.-I. (2013). A 4.8-GHz dividerless subharmonically injection-locked all-digital PLL with a FOM of –252.5 dB. IEEE Transactions on Circuits and Systems II: Express Briefs, 60(9), 547–551. https://doi.org/10.1109/TCSII.2013.2268640

Ho, Y.-H., & Yao, C.-Y. (2016). A low-jitter fast-locked all-digital phase-locked loop with phase–frequency-error compensation. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 24(5), 1984–1992. https://doi.org/10.1109/TVLSI.2015.2470545

Su, C.-C., Lin, C.-C., & Hung, C.-C. (2017). An all-digital phase-locked loop with a multi-delay-switching TDC. In: 2017 International Symposium on VLSI Design, Automation and Test (VLSI-DAT), (pp. 1–4). IEEE. https://doi.org/10.1109/VLSI-DAT.2017.7939662

Jang, S., Kim, S., Chu, S.-H., Jeong, G.-S., Kim, Y., & Jeong, D.-K. (2015). An optimum loop gain tracking all-digital PLL using autocorrelation of bang-bang phase-frequency detection. IEEE Transactions on Circuits and Systems II: Express Briefs, 62(9), 836–840. https://doi.org/10.1109/TCSII.2015.2435691

Seo, Y.-H., Lee, S.-K., & Sim, J.-Y. (2011). A 1-GHz digital PLL with a 3-ps resolution floating-point-number TDC in a 0.18-μm CMOS. IEEE Transactions on Circuits and Systems II: Express Briefs, 58(2), 70–74. https://doi.org/10.1109/TCSII.2011.2106315

Shabaany, M. H., & Saneei, M. (2012) A 0.7-to-1.1-GHz all-digital phase-locked loop with a new phase frequency detector and controlled oscillator with body-biasing. In: The 16th CSI International Symposium on Computer Architecture and Digital Systems (CADS 2012), (pp. 54–59). IEEE. https://doi.org/10.1109/CADS.2012.6316419

Tasca, D., Zanuso, M., Marzin, G., Levantino, S., Samori, C., & Lacaita, A. L. (2011). A 2.9–4.0-GHz fractional-N digital PLL with bang-bang phase detector and 560-fs rms integrated jitter at 4.5-mW Power. IEEE Journal of Solid-State Circuits, 46(12), 2745–2758. https://doi.org/10.1109/JSSC.2011.2162917

Kumar, M. (2012). FPGA implementation of ADPLL with ripple reduction techniques. International Journal of VLSI Design & Communication Systems, 3(2), 99–106. https://doi.org/10.5121/vlsic.2012.3209

Zeng, K.-H., Kuan, T.-K., & Liu, S.-I. (2015). A subharmonically injection-locked all-digital PLL without main divider. IEEE Transactions on Circuits and Systems II: Express Briefs, 62(11), 1033–1037. https://doi.org/10.1109/TCSII.2015.2455292

Fergusson, WW., Patel, RH., Bereza, W. (2007) Modeling and simulation of noise in closed-loop all-digital PLLs using Verilog-A. In: 2007 IEEE custom integrated circuits conference, (pp. 857–860). IEEE. https://doi.org/10.1109/CICC.2007.4405863

Tarar, M. A., Sun, J., Sampson A., Wilcox, R., & Zhizhang Chen. (2009) The implementation of a new all-digital phase-locked loop on an FPGA and its testing in a complete wireless transceiver architecture. In: 2009 Seventh annual communication networks and services research conference, pp. 238–244. IEEE. https://doi.org/10.1109/CNSR.2009.44

Wu, J., Wang, Z., Chen, C., Huang, C., & Zhang, M. (2015). A 2.4-GHz all-digital PLL with a 1-ps resolution 0.9-mW edge-interchanging-based stochastic TDC. IEEE Transactions on Circuits and Systems II: Express Briefs, 62(10), 917–921. https://doi.org/10.1109/TCSII.2015.2457792

Ferreira, L., Moreira, M., Souza, B., Ferreira, S., Baumgratz, F., & Bampi, S. (2020) Review on the evolution of low-power and highly-linear time-to-digital converters–TDC. In: 2020 IEEE 11th Latin American symposium on circuits & systems (LASCAS), (pp. 1–4). IEEE. https://doi.org/10.1109/LASCAS45839.2020.9068950

Staszewski, R. B., & Balsara, P. T. (2006). All-digital frequency synthesizer in deep-submicron CMOS. Wiley. https://doi.org/10.1002/0470041951

Liu, M., Liu, H., Li, X., & Zhu, Z. (2020). A 60-m range 6.16-mW laser-power linear-mode LiDAR system with multiplex ADC/TDC in 65-nm CMOS. IEEE Transactions on Circuits and Systems I: Regular Papers, 67(3), 753–764. https://doi.org/10.1109/TCSI.2019.2955671

Arvani, F., & Carusone, A. C. (2021). Peak-SNR analysis of CMOS TDCs for SPAD-based TCSPC 3D imaging applications. IEEE Transactions on Circuits and Systems II: Express Briefs, 68(3), 893–897. https://doi.org/10.1109/TCSII.2020.3023631

Cheng, Z., Deen, M. J., & Peng, H. (2016). A low-power gateable vernier ring oscillator time-to-digital converter for biomedical imaging applications. IEEE Transactions on Biomedical Circuits and Systems, 10(2), 445–454. https://doi.org/10.1109/TBCAS.2015.2434957

Hussein, A. I., Vasadi, S., & Paramesh, J. (2018). A 450 fs 65-nm CMOS millimeter-wave time-to-digital converter using statistical element selection for all-digital PLLs. IEEE Journal of Solid-State Circuits, 53(2), 357–374. https://doi.org/10.1109/JSSC.2017.2762698

Sahani, J. K., Singh, A., & Agarwal, A. (2020). A fast locking and low jitter hybrid ADPLL architecture with bang bang PFD and PVT calibrated flash TDC. AEU–International Journal of Electronics and Communications. https://doi.org/10.1016/j.aeue.2020.153344

Bhati, D., & Singh, B. (2017). Design and analysis of a low power digital phase locked loop. In: Proceedings–2016 8th international conference on computational intelligence and communication networks, CICN 2016. Institute of Electrical and Electronics Engineers Inc, (pp. 275–279). https://doi.org/10.1109/CICN.2016.60

Zhao, B.,& Yan, D.L. (2016). A low-power digital design of all digital PLL for 2.4G wireless communication applications. In: 2016 international symposium on integrated circuits (ISIC). IEEE. https://doi.org/10.1109/ISICIR.2016.7829674

Balcioǧlu, Y., & Dündar, G. (2017). A 0.65-1.35 GHz synthesizable all-digital phase locked loop with quantization noise suppressing time-to-digital converter. Turkish Journal of Electrical Engineering and Computer Sciences, 25(3), 2410–2423. https://doi.org/10.3906/elk-1601-185

Habib, A., Dessouky, M., & Naguib, A. (2022). A Pulse-Train Time Amplifier used for Time-based Phase detectors in ADPLLs. In: Proceedings of the 10th international Japan-Africa conference on electronics, communications, and computations, JAC-ECC 2022, institute of electrical and electronics engineers Inc., (pp. 64–67). https://doi.org/10.1109/JAC-ECC56395.2022.10043869.

Dudek, P., Szczepanski, S., & Hatfield, J. V. (2000). A high-resolution CMOS time-to-digital converter utilizing a vernier delay line. IEEE Journal of Solid-State Circuits, 35(2), 240–247. https://doi.org/10.1109/4.823449

Vercesi, L., Liscidini, A., & Castello, R. (2010). Two-dimensions vernier time-to-digital converter. IEEE Journal of Solid-State Circuits, 45(8), 1504–1512. https://doi.org/10.1109/JSSC.2010.2047435

Vercesi, L., Fanori, L., De Bernardinis, F., Liscidini, A., & Castello, R. (2012). A dither-less all digital PLL for cellular transmitters. IEEE Journal of Solid-State Circuits, 47(8), 1908–1920. https://doi.org/10.1109/JSSC.2012.2197130

Lee, S.-K., Seo, Y.-H., Park, H.-J., & Sim, J.-Y. (2010). A 1 GHz ADPLL With a 1.25 ps Minimum-Resolution Sub-Exponent TDC in 0.18-μm CMOS. IEEE Journal of Solid-State Circuits, 45(12), 2874–2881. https://doi.org/10.1109/JSSC.2010.2077110

IEEE Solid-State Circuits Society, & Ōyō Butsuri Gakkai. (2009). In: VLSI circuits symposium. IEEE.

Zhang, W., Ma, R., Wang, X., Zheng, H., & Zhu, Z. (2022). A high linearity TDC with a united-reference fractional counter for LiDAR. IEEE Transactions on Circuits and Systems I: Regular Papers, 69(2), 564–572. https://doi.org/10.1109/TCSI.2020.3045731

Levinger, R. (2019). A Compact 3.9-4.7 GHz, 0.82 mW all-digital PLL with 543 fs RMS jitter in 28 nm CMOS. In: IEEE 19th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF). IEEE. https://doi.org/10.1109/SIRF.2019.8709087

Chen, P., Meng, X., Yin, J., Mak, P.-I., Martins, R. P., & Staszewski, R. B. (2022). A 529-μW fractional-N all-digital PLL using TDC gain auto-calibration and an inverse-class-F DCO in 65-nm CMOS. IEEE Transactions on Circuits and Systems I: Regular Papers, 69(1), 51–63. https://doi.org/10.1109/TCSI.2021.3094094

Wu, Y., Shahmohammadi, M., Chen, Y., Lu, P., & Staszewski, R. B. (2017). A 3.5–6.8-GHz wide-bandwidth DTC-assisted fractional-N all-digital PLL with a MASH ΔΣ-TDC for Low In-Band Phase Noise. IEEE Journal of Solid-State Circuits, 52(7), 1885–1903. https://doi.org/10.1109/JSSC.2017.2682841

Liu, H. et al. (2018). A 0.98mW fractional-N ADPLL using 10b isolated constant-slope DTC with FOM of −246dB for IoT applications in 65nm CMOS. In: 2018 IEEE international Solid - State circuits conference - (ISSCC), 246 248. IEEE. https://doi.org/10.1109/ISSCC.2018.8310276

Siriburanon, T., et al. (2016). A 2.2 GHz -242 dB-FOM 4.2 mW ADC-PLL using digital sub-sampling architecture. IEEE Journal of Solid-State Circuits, 51(6), 1385–1397. https://doi.org/10.1109/JSSC.2016.2546304

Elshazly, A., Rao, S., Young, B., & Hanumolu, P. K. (2014). A noise-shaping time-to-digital converter using switched-ring oscillators—analysis, design, and measurement techniques. IEEE Journal of Solid-State Circuits, 49(5), 1184–1197. https://doi.org/10.1109/JSSC.2014.2305651

Hung, C. C., & Liu, S. I. (2011). A 40-GHz fast-locked all-digital phase-locked loop using a modified bang-bang algorithm. IEEE Transactions on Circuits and Systems II: Express Briefs, 58(6), 321–325. https://doi.org/10.1109/TCSII.2011.2149610

Hwang, I.-C., Song, S.-H., & Kim, S.-W. (2001). Brief papers a digitally controlled phase-locked loop with a digital phase-frequency detector for fast acquisition.

Zhang, L., Wang, Z., Zhang, T., & Peng, X. (2018). An improved fast acquisition phase frequency detector for high speed phase-locked loops. In: AIP conference proceedings, American Institute of Physics Inc. https://doi.org/10.1063/1.5033694

Ali, I., et al. (2017). An ultra low power fully synthesizable digital phase and frequency detector for adpll applications in 55 nm CMOS Technology.

Abdul Majeed, K. K., & Kailath, B. J. (2017). Low power PLL with reduced reference spur realized with glitch-free linear PFD and current splitting CP. Analog Integrated Circuits Signal Process, 93(1), 29–39. https://doi.org/10.1007/s10470-017-1013-4

Ishak, S. N., Sampe, J., Hashim, F. H., & Faseehuddin, M. (2022). Digital phase-frequency detector in all-digital pll-based local oscillator for radio frequency identification system transceiver. In: 2022 IEEE 18th International colloquium on signal processing & applications (CSPA), (pp. 231–236). IEEE. https://doi.org/10.1109/CSPA55076.2022.9781829

Ishak, S. N., Sampe, J., Nayan, N. A., & Yusoff, Z. (2022). A fast digital phase frequency detector with preset word frequency searching in ADPLL for a UHF RFID reader. Engineering, Technology & Applied Science Research, 12(5), 9379–9387. https://doi.org/10.48084/etasr.5202

Zhuang, J., Du, Q., & Kwasniewski, T. (2007). A 4GHz low complexity ADPLL-based frequency synthesizer in 90nm CMOS. In: 2007 IEEE custom integrated circuits conference, (pp. 543–546). IEEE. https://doi.org/10.1109/CICC.2007.4405790

Ahmad, N., & Lee, K. Y. (2023). Design and implementation of a low-area reconfigurable and synthesizable digital loop filter for ADPLL. In: 2023 fourteenth international conference on ubiquitous and future networks (ICUFN), (pp. 580–582). IEEE. https://doi.org/10.1109/ICUFN57995.2023.10199652

Sayadi, M., & Farshidi, E. (2016). A fast locked and low phase noise all-digital phase locked loop based on model predictive control. Analog Integr Circuits Signal Process, 88(3), 401–414. https://doi.org/10.1007/s10470-016-0794-1

Shi, L., Gai, W., Tang, L., & Xiang, X. (2017). A novel digital loop filter with frequency error prediction for fast-locking bang-bang ADPLL. In: 2017 international conference on electron devices and solid-state circuits (EDSSC), (pp. 1–2). IEEE. https://doi.org/10.1109/EDSSC.2017.8333239

Lotfy, A., Ghoneima, M., & Abdel-Moneum, M. (2016). A fast locking hybrid TDC-BB ADPLL utilizing proportional derivative digital loop filter and power gated DCO. In: 2016 IEEE international symposium on circuits and systems (ISCAS), (pp. 1646–1649). IEEE. https://doi.org/10.1109/ISCAS.2016.7538882.

Yang, S.-Y., Chen, W.-Z., & Lu, T.-Y. (2010). A 7.1 mW, 10 GHz all digital frequency synthesizer with dynamically reconfigured digital loop filter in 90 nm CMOS technology. IEEE Journal of Solid-State Circuits, 45(3), 578–586. https://doi.org/10.1109/JSSC.2009.2039530

Staszewski, R. B., et al. (2004). All-digital TX frequency synthesizer and discrete-time receiver for bluetooth radio in 130-nm CMOS. IEEE Journal of Solid-State Circuits, 39(12), 2278–2291. https://doi.org/10.1109/JSSC.2004.836345

Muhammad, K., et al. (2006). The first fully integrated quad-band GSM/GPRS Receiver in a 90-nm digital CMOS process. IEEE Journal of Solid-State Circuits, 41(8), 1772–1783. https://doi.org/10.1109/JSSC.2006.877271

Titus, W. S., & Kenney, J. G. (2012). A 5.6 GHz to 11.5 GHz DCO for Digital Dual Loop CDRs. IEEE Journal of Solid-State Circuits, 47(5), 1123–1130. https://doi.org/10.1109/JSSC.2012.2185572

Yu, C.-Y., Chung, C.-C., Yu, C.-J., & Lee, C.-Y. (2012). A low-power DCO using interlaced hysteresis delay cells. IEEE Transactions on Circuits and Systems II: Express Briefs, 59(10), 673–677. https://doi.org/10.1109/TCSII.2012.2213357

Bae, J., Yan, L., & Yoo, H. J. (2011). A low energy injection-locked FSK transceiver with frequency-to-amplitude conversion for body sensor applications. IEEE Journal of Solid-State Circuits, 46(4), 928–937. https://doi.org/10.1109/JSSC.2011.2109450

Xu, N., Rhee, W., & Wang, Z. (2014). A hybrid loop two-point modulator without DCO nonlinearity calibration by utilizing 1 bit high-pass modulation. IEEE Journal of Solid-State Circuits, 49(10), 2172–2186. https://doi.org/10.1109/JSSC.2014.2345021

Song, H., Kim, D. S., Oh, D. H., Kim, S., & Jeong, D. K. (2011). A 1.04.0-Gb/s all-digital CDR with 1.0-ps period resolution DCO and adaptive proportional gain control. IEEE Journal of Solid-State Circuits, 46(2), 424–434. https://doi.org/10.1109/JSSC.2010.2082272

Chung, C. C., Ko, C. Y., & Shen, S. E. (2011). Built-in self-calibration circuit for monotonic digitally controlled oscillator design in 65-nm CMOS technology. IEEE Transactions on Circuits and Systems II: Express Briefs, 58(3), 149–153. https://doi.org/10.1109/TCSII.2011.2110370

De Caro, D. (2013). Glitch-free NAND-based digitally controlled delay-lines. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 21(1), 55–66. https://doi.org/10.1109/TVLSI.2011.2181547

Staszewski, R. B., Leipold, D., Chih-Ming Hung, & Balsara, P. T. (2003). A first digitally-controlled oscillator in a deep-submicron CMOS process for multi-GHz wireless applications. In: IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, (pp. 81–84). IEEE. https://doi.org/10.1109/RFIC.2003.1213898

Razavi, B. (1996). A study of phase noise in CMOS oscillators. IEEE Journal of Solid-State Circuits, 31(3), 331–343. https://doi.org/10.1109/4.494195

Xu, L., Lindfors, S., Stadius, K., & Ryynanen, J. (2010). A 2.4-GHz low-power all-digital phase-locked loop. IEEE Journal of Solid-State Circuits, 45(8), 1513–1521. https://doi.org/10.1109/JSSC.2010.2047453

Heydarzadeh, S., Torkzadeh, P., & Sadughi, S. (2019). A fully linear 5.2 GHz - 5.8 GHz digitally controlled oscillator in 65-nm CMOS technology. Microelectronics Journal, 90, 48–57. https://doi.org/10.1016/j.mejo.2019.04.018

Sadr, M. S., Ghafoorifard, H., Yavari, M., & Sheikhaei, S. (2016).A novel low phase noise and low power DCO in 90 nm CMOS technology for ADPLL application. In: 2016 24th Iranian conference on electrical engineering (ICEE), (pp. 810–815). IEEE. https://doi.org/10.1109/IranianCEE.2016.7585631

Haddad, F., Rahajandraibe, W., & Ghorbel, I. (2019). Compact RF CMOS 4-bit Digitally Controlled Oscillator. In: 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), (pp. 378–381). IEEE. https://doi.org/10.1109/ICECS46596.2019.8964931

Wang, Y., Wei, M-D.,& Negra, R. (2019). Ultralow Power, 3.15 mW, 76.7 GHz digitally controlled oscillator in 65 nm CMOS for high data-rate application. In: 2019 14th European microwave integrated circuits conference (EuMIC), (pp. 5–8). IEEE. https://doi.org/10.23919/EuMIC.2019.8909398

Moreira, M., Ferreira, L., Souza, B., Ferreira, S. B., Baumgratz, F. D., & Bampi, S. (2019). Low power 380 μW Energy Efficient 1.8 GHz Digitally Controlled Oscillator for IoT Applications. In: 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), (pp. 763–766). IEEE. https://doi.org/10.1109/ICECS46596.2019.8964984

Ali, I., et al. (2020). An ultra-low power, adaptive all-digital frequency-locked loop with gain estimation and constant current DCO. IEEE Access, 8, 97215–97230. https://doi.org/10.1109/ACCESS.2020.2995853

Rehman, M. R. U., et al. (2021). An ultra-low-power 2.4 GHz all-digital phase-locked loop with injection-locked frequency multiplier and continuous frequency tracking. IEEE Access, 9, 152984–152992. https://doi.org/10.1109/ACCESS.2021.3123167

Abdullah, S., Rogers, J. W. M., & Amaya, R. E. (2022). A 6 GHz Digitally-Controlled Oscillator Achieving Minimum Fine Tuning Step Size of Up to 160 Hz Using Capacitive Degeneration Technique in 40 nm CMOS Process. In: 2022 international conference on microelectronics (ICM), pp. 144–147. IEEE. https://doi.org/10.1109/ICM56065.2022.10005329

Duan, S., Li, Z., Wu, Y., Li, Z., He, X., & Leng, J. (2024). Design and analysis of high-resolution CMOS digitally controlled oscillator with tunable transformer. Microelectronics Journal, 143, 106060. https://doi.org/10.1016/j.mejo.2023.106060

Suraparaju, E. R., Arja, P. V. R., & Ren, S. (2015). A 1.1–8.2 GHz tuning range In-phase and quadrature output DCO design in 90 nm CMOS technology. In: 2015 IEEE 58th international midwest symposium on circuits and systems (MWSCAS), (pp. 1–4). IEEE. https://doi.org/10.1109/MWSCAS.2015.7282171

Dabas, S., & Kumar, M. (2016). A new design of digitally controlled oscillator for low power applications. In: 2016 2nd International Conference on Contemporary Computing and Informatics (IC3I), (pp. 671–675). IEEE. https://doi.org/10.1109/IC3I.2016.7918047

Pahlavan, S., & Ghaznavi-Ghoushchi, M. B. (2016). 1.45 GHz differential dual band ring based digitally-controlled oscillator with a reconfigurable delay element in 0.18 μm CMOS process. Analog Integr Circuits Signal Process, 89(2), 461–467. https://doi.org/10.1007/s10470-016-0814-1

Yuan, C., & Shekhar, S. (2019). A supply-noise-insensitive digitally-controlled oscillator. IEEE Transactions on Circuits and Systems I: Regular Papers, 66(9), 3414–3422. https://doi.org/10.1109/TCSI.2019.2924399

Bisiaux, P., Blokhina, E., Koskin, E., Siriburanon, T., & Galayko, D. (2020). Design of a 1.5 GHz low jitter DCO ring in 28 nm CMOS process. In: 2020 European conference on circuit theory and design (ECCTD), (pp. 1–5). IEEE. https://doi.org/10.1109/ECCTD49232.2020.9218352

Liu, J.-C., & Li, Y.-P. (2021). A low supply voltage all-digital phase-locked loop with a bootstrapped and forward interpolation digitally controlled oscillator. IEEE Access, 9, 39717–39726. https://doi.org/10.1109/ACCESS.2021.3064378

Baek, K., Kim, K. & Jeong, D-K. (2022). A 5GHz All-digital PLL with shunt regulating ring DCO in BOST for DDR5 ATE. In: 2022 19th international SoC design conference (ISOCC), (pp.139–140). IEEE. https://doi.org/10.1109/ISOCC56007.2022.10031547

Selvaraj, S., Bayram, E., & Negra, R. (2020). Low phase noise, high resolution digitally-controlled ring oscillator operating at 2.2GHz. In: 2020 9th International Conference on Modern Circuits and Systems Technologies (MOCAST), (pp. 1–4). IEEE. https://doi.org/10.1109/MOCAST49295.2020.9200272

Yan, N., et al. (2019). A low power all-digital PLL with -40dBc In-band fractional spur suppression for NB-IoT applications. IEEE Access, 7, 7897–7904. https://doi.org/10.1109/ACCESS.2018.2890073

Hoppner, S., Partzsch, J., Neumann, J., Schuffny, R., & Mayr, C. (2016). A calibration technique for bang-bang ADPLLs using jitter distribution monitoring. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 24(12), 3548–3552. https://doi.org/10.1109/TVLSI.2016.2558664

Pourmousavian, N., Kuo, F. W., Siriburanon, T., Babaie, M., & Staszewski, R. B. (2018). A 0.5-V 1.6-mW 2.4-GHz fractional-N All-digital PLL for bluetooth le with PVT-insensitive tdc using switched-capacitor doubler in 28-nm CMOS. IEEE Journal of Solid-State Circuits, 53(9), 2572–2583. https://doi.org/10.1109/JSSC.2018.2843337

Kim, H., Jung, W., Kim, K., Kim, S., Choi, W. S., & Jeong, D. K. (2022). A low-jitter 8-GHz RO-based ADPLL with PVT-robust replica-based analog closed loop for supply noise compensation. IEEE Journal of Solid-State Circuits, 57(6), 1712–1722. https://doi.org/10.1109/JSSC.2022.3148174

Shen, Z., et al. (2020). A 12-GHz calibration-free all-digital PLL for FMCW signal generation with 78 MHz/μs chirp slope and high chirp linearity. IEEE Transactions on Circuits and Systems I: Regular Papers, 67(12), 4445–4456. https://doi.org/10.1109/TCSI.2020.3004363

Li, C. C., et al. (2021). A compact transformer-based fractional-N ADPLL in 10-nm FinFET CMOS. IEEE Transactions on Circuits and Systems I: Regular Papers, 68(5), 1881–1891. https://doi.org/10.1109/TCSI.2021.3059484

Tang, H., Liu, X., Yang, C., & Jin, J. (2023) An ADPLL with two-point modulation gain calibration for 2.4GHz ISM-band in 40nm CMOS. In: 2023 IEEE international symposium on circuits and systems (ISCAS), (pp. 1–4). IEEE. https://doi.org/10.1109/ISCAS46773.2023.10181799

Jin, Z., et al. (2024). A Fractional-N DTC-based ADPLL using path-select multi-delay line TDC and true fractional division technique. Microelectronics Journal, 145, 106102. https://doi.org/10.1016/j.mejo.2024.106102

Sheng, D., Chen, W. Y., Chang, Y. H., & Huang, H. T. (2020). High-timing-resolution and low-complexity cell-based digitally controlled oscillator. In: 2020 IEEE International Conference on Consumer Electronics – Taiwan. ICCE-Taiwan. https://doi.org/10.1109/ICCE-TAIWAN49838.2020.9258210

Szopos, E., Saracut, I., Kirei, B. S., & Dana Topa, M. (2017). Discrete domain modeling of an all-digital frequency locked loop. In 2017 international semiconductor conference (CAS), (pp. 247–250). IEEE. https://doi.org/10.1109/SMICND.2017.8101214

Solanki, P., Gurjar, R. C., & Mishra, D. K. (2018). Design of LC-tank digitally controlled oscillator with variable capacitor. In: 2018 4th international conference for convergence in technology. I2CT. https://doi.org/10.1109/I2CT42659.2018.9058250

Acknowledgements

This work is funded by a UKM internal grant and a PAME SDN BHD industry grant under the grants GUP-2022-069 and RR-2022-001, respectively.

Funding

UKM Internal Grant, GUP-2022-069, PAME SDN BHD,RR-2022-001

Author information

Authors and Affiliations

Contributions

Abdul Khaliq: Conceptualization, Methodology, Formal analysis, Investigation, Visualization, Writing an original draft. Jahariah Sampe: Conceptualization, Project administration, Formal analysis, Validation, Supervision, Writing -review & editing. Fazida Hanim Hashim: Validation, Writing -review& editing, Huda Abdullah: Writing -review& editing, Noor Hidayah Mohd Yunus: Writing -review& editing, Muhammad Asim Noon: Writing -review& editing.

Corresponding author

Ethics declarations

Competing interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Data availability

No data was used for the research described in the article.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Khaliq, A., Sampe, J., Hashim, F.H. et al. A comprehensive review: ultra-low power all-digital phase-locked loop RF transceivers for biomedical monitoring applications. Analog Integr Circ Sig Process (2024). https://doi.org/10.1007/s10470-024-02272-1

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10470-024-02272-1