Abstract

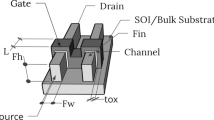

The principal design concern in today’s very large-scale integration (VLSI) industry is power dissipation. Power dissipation in a chip rises reliability issues. Static power dissipation places a bottleneck in scaling down the dimensions and supply voltage of metal oxide semiconductor field effect transistor (MOSFET). Short channel effects (SCEs) put a limit on MOSFET scaling. At the lower technology nodes, the control of the gate over the channel is lost in MOSFET. Fin-shaped field effect transistor (FinFETs) uses multiple gates to gain much electrostatic control over the channel. FinFET not only improves the drive current but also reduces the subthreshold leakage. This paper proposes a novel power-efficient technique for the nanoscale regime. The simulation results are derived using Mentor Graphics at a 16 nm node. The power is reduced by 91.45% and 89.01% in the proposed MOSFET and FinFET-based inverter, respectively. A chain of 5-inverters is designed as a benchmark circuit to check the performance comparisons. In the proposed MOSFET and FinFET-based benchmark circuit, there is a power delay product (PDP) reduction of 80.28%, and 99.87%, respectively. The effect of process voltage and temperature (PVT) variations for the robustness of the technique is also discussed. The proposed technique provides the power-efficient and robustness operation against the variations as compared to the other methods.

Similar content being viewed by others

Data availability

Not applicable.

References

Sharma, V. K., & Pattanaik, M. (2015). A reliable ground bounce noise reduction technique for nanoscale CMOS circuits. International Journal of Electronics, 102(11), 1852–1866.

Sharma, V. K. (2021). A survey of leakage reduction techniques in CMOS digital circuits for nanoscale regime. Australian Journal of Electrical and Electronics Engineering, 18(4), 217–236.

Haensch, W., et al. (2006). Silicon CMOS devices beyond scaling. IBM Journal of Research and Development, 50(4–5), 339–361.

Sharma, V. K., & Pattanaik, M. (2016). Design of low leakage variability aware ONOFIC CMOS standard cell library. Journal of Circuits, Systems and Computers, 25(11), 1650134.

Bhattacharya, D., & Jha, N. K. (2014). FinFETs: From devices to architectures. Advances in Electronics, 2014, 1–21.

J. Gu, J. Keane, S. Sapatnekar, and C. Kim, (2006) Width quantization aware FinFET circuit design. In: Proceedings of the Custom Integrated Circuits Conference, 337–340

Boukortt, N. E. I., Lenka, T. R., Patanè, S., & Crupi, G. (2021). Effects of varying the fin width, fin height, gate dielectric material, and gate length on the DC and RF performance of a 14 nm SOI FinFET structure. Electronics, 11(1), 91.

Riaz, A., & Sharma, V. K. (2022). A novel low power 4: 2 compressor using FinFET devices. Analog Integrated Circuits and Signal Processing, 112, 127–139.

Boukortt, N., Hadri, B., Patanè, S., Caddemi, A., & Crupi, G. (2016). Electrical characteristics of 8-nm SOI n-FinFETs. SILICON, 8(4), 497–503.

Subramanian, V., et al. (2007). Impact of fin width on digital and analog performances of n-FinFETs. Solid-State Electronics, 51(4), 551–559.

Mushtaq, U., & Sharma, V. K. (2020). Design and analysis of INDEP FinFET SRAM cell at 7-nm technology. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, 33(5), e2730.

T. Kitahara et al., (1998) Clock-gating method for low-power LSI design. In: Proceedings of the Asia and South Pacific Design Automation Conference, ASP-DAC, 307–312, 1998.

Srikanth, G., Bhaskara, B. M., & Rani, M. A. (2016). A survey on power gating techniques in low power VLSI design. Advances in Intelligent Systems and Computing, 435, 297–307.

Ogras, U. Y., Marculescu, R., Marculescu, D., & Jung, E. G. (2009). Design and management of voltage-frequency island partitioned networks-on-chip. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 17(3), 330–341.

Greenberg, S., Rabinowicz, J., & Manor, E. (2015). Selective state retention power gating based on formal verification. IEEE Transactions on Circuits and Systems I: Regular Papers, 62(3), 807–815.

Sharma, V. K., Patel, S., & Pattanaik, M. (2014). High performance process variations aware technique for sub-threshold 8T-SRAM cell. Wireless Personal Communications, 78(1), 57–68.

Sharma, V. K. (2022). A novel approach for designing of variability aware low-power logic gates. ETRI Journal, 44(3), 491–503.

Sharma, V. K., Pattanaik, M., & Raj, B. (2014). PVT variations aware low leakage INDEP approach for nanoscale CMOS circuits. Microelectronics Reliability, 54(1), 90–99.

Anis, M., Areibi, S., & Elmasry, M. (2003). Design and optimization of multithreshold CMOS (MTCMOS) circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 22(10), 1324–1342.

Hanchate, N., & Ranganathan, N. (2004). LECTOR: A technique for leakage reduction in CMOS circuits. IEEE Transactions on Very Large Scale Integration VLSI Systems, 12(2), 196–205.

Lorenzo, R., & Chaudhury, S. (2017). LCNT-an approach to minimize leakage power in CMOS integrated circuits. Microsystem Technologies, 23(9), 4245–4253.

Corsonello, P., Lanuzza, M., & Perri, S. (2014). Gate-level body biasing technique for high-speed sub-threshold CMOS logic gates. International Journal of Circuit Theory and Applications, 42(1), 65–70.

Accessed link for model files: https://ptm.asu.edu/.

Z. A. Tarawneh, (2011)The effects of process variations on performance and robustness of bulk CMOS and SOI implementations of C-elements, Newcastle University eTheses, https://theses.ncl.ac.uk/jspui/handle/10443/1289.

Toriyama, S., & Sano, N. (2003). Probability distribution functions of threshold voltage fluctuations due to random impurities in deca–nano MOSFETs. Physica E: Low-dimensional Systems and Nanostructures, 19(1–2), 44–47.

Sharma, V. K., Pattanaik, M., & Raj, B. (2015). INDEP approach for leakage reduction in nanoscale CMOS circuits. International Journal of Electronics, 102(2), 200–215.

W. Sootkaneung, S. Howimanporn, and S. Chookaew, (2017) Thermal effect on performance, power, and BTI aging in FinFET-based designs. In: Proceedings - 20th Euromicro Conference on Digital System Design, DSD, 2011: 345–351

W. Lee, Y. Wang, T. Cui, S. Nazarian, and M. Pedram, (2015) Dynamic thermal management for FinFET-based circuits exploiting the temperature effect inversion phenomenon. In: Proceedings of the International Symposium on Low Power Electronics and Design, 2015: 105–110

Rai, S., Sahu, J., Dattatray, W., Mishra, R. A., & Sudarshan, T. (2012). Modelling, design, and performance comparison of triple gate cylindrical and partially cylindrical FinFETs for low-power applications. International Scholarly Research Notices, 2012, 827452.

Sharma, V. K. (2022). CNTFET circuit-based wide fan-in domino logic for low power applications. Journal of Circuits, Systems and Computers, 31(2), 2250036.

Acknowledgements

The author thanks the editor and reviewers for their helpful comments and suggestions.

Funding

None.

Author information

Authors and Affiliations

Contributions

Shams Ul Haq has contributed for the concept generation, methodology formation, formal analysis and investigation, and writing original draft of the manuscript. Vijay Kumar Sharma has contributed writing, reviewing and editing the final manuscript, and supervising the work.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Consent for publication

Not applicable.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Haq, S.U., Sharma, V.K. Reliable and ultra-low power approach for designing of logic circuits. Analog Integr Circ Sig Process 119, 85–95 (2024). https://doi.org/10.1007/s10470-023-02207-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-023-02207-2