Abstract

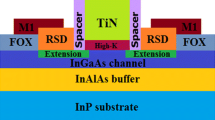

This work proposes an optimized Nanosheet Transistor (NSHT) with an inner high-k spacer and an underlap region. A symmetric dual-k spacer structure and an undoped underlap region are incorporated into the baseline device to optimize it for better performance. The optimized NSHT exhibits an improvement of 54% in the on-to-off current ratio (ION/IOFF) and 36% in the off current (IOFF) over the baseline NSHT of 5 nm node. The analog performance of the optimized NSHT is compared with the performance of the baseline NSHT device across the design space. The optimized NSHT, with Lg/Wg = 12 nm/120 nm, shows the largest transconductance (gm) value with a 6.7% increment compared to the baseline device. An increase of 4.9% in the maximum value of Av is obtained in optimized NSHT with Lg/Wg = 12 nm/15 nm, as compared to its baseline counterpart NSHT. Also, the intrinsic gain (Av) of optimized NSHT, with Lg/Wg = 12 nm/120 nm, shows a most significant improvement of 8.6% over its baseline counterpart NSHT. NSHT with Lg/Wg = 12 nm /120 nm has the highest value of unit-gain frequency (fT) for both optimized and baseline structures. Baseline NSHT shows higher fT values. NSHT with Lg/Wg = 12 nm/15 nm shows the highest gain frequency product (GFP). The optimized NSHT device gives a better analog performance in terms of gain (Av). However, the baseline NSHT device will serve the purpose better for analog applications requiring large fT and GFP values.

Similar content being viewed by others

Data/materials availability

Not applicable.

References

Schaller, R. R. (1997). Moore’s law: past, present and future. IEEE Spectrum, 34(6), 52–59. https://doi.org/10.1109/6.591665

Gargini, P. (2017). “Roadmap evolution: From NTRS to ITRS, from ITRS 2.0 to IRDS. In 2017 Fifth berkeley symposium on energy efficient electronic systems & steep transistors workshop (E3S) (pp. 1-62). IEEEhttps://doi.org/10.1109/E3S.2017.8246153.

Bardon, M. G., Schuddinck, P., Raghavan, P., Jang, D., Yakimets, D., Mercha, A., ... & Thean, A. (2015, June). Dimensioning for power and performance under 10nm: The limits of FinFETs scaling. In 2015 international conference on IC design & technology (ICICDT) (pp. 1-4). IEEE. https://doi.org/10.1109/ICICDT.2015.7165883.

Seon, Y., Chang, J., Yoo, C., & Jeon, J. (2021). Device and circuit exploration of multi-nanosheet transistor for sub-3 nm technology node. Electronics, 10(2), 1–14. https://doi.org/10.3390/electronics10020180

Loubet, N., Hook, T., Montanini, P., Yeung, C., Kanakasabapathy, S., Guillorn, M., & Miao, X. (2017). T17–5 (late news ) stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET T230 T231. VLSI Technology, 5(1), 14–15.

Yeung, C. W., Zhang, J., Chao, R., Kwon, O., Vega, R., Tsutsui, G., & Guo, D. (2018, December). Channel geometry impact and narrow sheet effect of stacked nanosheet. In 2018 IEEE international electron devices meeting (IEDM) (pp. 28-6). IEEE https://doi.org/10.1109/IEDM.2018.8614608.

Yang, J. W., Zeitzoff, P. M., & Tseng, H. H. (2007). Highly manufacturable double-gate finFET with gate-source/drain underlap. IEEE Transactions on Electron Devices, 54(6), 1464–1470. https://doi.org/10.1109/TED.2007.896387

Sachid, A. B., Manoj, C. R., Sharma, D. K., & Rao, V. R. (2008). Gate fringe-induced barrier lowering in underlap FinFET structures and its optimization. IEEE Electron Device Letters, 29(1), 128–130. https://doi.org/10.1109/LED.2007.911974

Pal, P. K., Kaushik, B. K., & Dasgupta, S. (2013). High-performance and robust SRAM cell based on asymmetric dual-k spacer Finfets. IEEE Transactions on Electron Devices, 60(10), 3371–3377. https://doi.org/10.1109/TED.2013.2278201

Pal, P. K., Kaushik, B. K., & Dasgupta, S. (2014). Investigation of symmetric dual-k spacer trigate FinFETs from delay perspective. IEEE Transactions on Electron Devices, 61(11), 3579–3585. https://doi.org/10.1109/TED.2014.2351616

Ko, H., Kim, J., Kang, M., & Shin, H. (2017). Investigation and analysis of dual-k spacer with different materials and spacer lengths for nanowire-FET performance. Solid-State Electronics, 136, 68–74. https://doi.org/10.1016/j.sse.2017.06.026

Pal, P. K., Kaushik, B. K., & Dasgupta, S. (2015). Asymmetric dual-spacer trigate FinFET device-circuit codesign and its variability analysis. IEEE Transactions on Electron Devices, 62(4), 1105–1112. https://doi.org/10.1109/TED.2015.2400053

Ryu, D., Kim, M., Kim, S., Choi, Y., Yu, J., Lee, J. H., & Park, B. G. (2020). Design and Optimization of Triple-k Spacer Structure in Two-Stack Nanosheet FET from OFF-State Leakage Perspective. IEEE Transactions on Electron Devices, 67(3), 1317–1322. https://doi.org/10.1109/TED.2020.2969445

Pundir, Y. P., Saha, R., & Pal, P. K. (2020). Effect of gate length on performance of 5nm node N-channel nano-sheet transistors for analog circuits. Semiconductor Science and Technology. https://doi.org/10.1088/1361-6641/abc51e

Pundir, Y. P., Bisht, A., Saha, R., & Pal, P. K. (2021). Air-spacers as analog-performance booster for 5 nm-node N-channel nanosheet transistor. Semiconductor Science and Technology. https://doi.org/10.1088/1361-6641/ac16e6

Bisht, A., Pundir, Y. P., & Pal, P. K. (2022). Electro-Thermal analysis of vertically stacked gate all around nano-sheet transistor. In international symposium on VLSI design and test (pp. 126-136). Cham: Springer Nature Switzerland https://doi.org/10.1007/978-3-031-21514-8_12.

Sentaurus device user guide (2019) Version-Q 2019.12. Synopsys Inc., Mountain View.

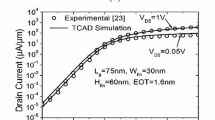

Yoon, J. S., Jeong, J., Lee, S., & Baek, R. H. (2018). Systematic DC/AC Performance Benchmarking of Sub-7-nm Node FinFETs and nanosheet FETs. IEEE Journal of the Electron Devices Society, 6(June), 942–947. https://doi.org/10.1109/JEDS.2018.2866026

Pundir, Y. P., Bisht, A., Saha, R., & Pal, P. K. (2022). Effect of temperature on performance of 5-nm node silicon nanosheet transistors for analog applications. SILICON. https://doi.org/10.1007/s12633-022-01800-w

Pal, P. K., Kaushik, B. K., & Dasgupta, S. (2014). Design metrics improvement for SRAMs using symmetric dual-k spacer (SymD-k) FinFETs. IEEE Transactions on Electron Devices, 61(4), 1123–1130. https://doi.org/10.1109/TED.2014.2304711

Cheng, K., Park, C., Wu, H., Li, J., Nguyen, S., Zhang, J., & Divakaruni, R. (2020). Improved air spacer for highly scaled CMOS technology. IEEE Transactions on Electron Devices, 67(12), 5355–5361. https://doi.org/10.1109/TED.2020.3031878

Razavi, B. (2001). Design of analog CMOS integrated circuits (2nd ed.). McGraw Hill Education.

Daoud Dammak, H., Bensalem, S., Zouari, S., & Loulou, M. (2008). Design of Folded cascode OTA in different regions of operation by the gm/Id methodology. International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering, 2(9), 89–94.

Murmann, B., Nikaeen, P., Connelly, D. J., & Dutton, R. W. (2006). Impact of scaling on analog performance and associated modeling needs. IEEE Transactions on Electron Devices, 53(9), 2160–2167. https://doi.org/10.1109/TED.2006.880372

Saha, R., Goswami, R., Bhowmick, B., & Baishya, S. (2020). Dependence of RF/analog and linearity figure of merits on temperature in ferroelectric FinFET: A simulation study. IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control, 67(11), 2433–2439. https://doi.org/10.1109/TUFFC.2020.2999518

Acknowledgements

Not applicable.

Funding

Not applicable.

Author information

Authors and Affiliations

Contributions

Arvind Bisht has contributed in the Conceptualization, Methodology, Writing Original Draft, Software, Data Curation, Investigation, Formal Analysis, and Editing. Yogendra Pratap Pundir has contributed to the Writing Original Draft and Formal Analysis. Pankaj Kumar Pal has contributed to Formal Analysis and Editing of this paper. All authors have contributed to the revision of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare that there is no conflict of interest reported in this paper.

Consent to participate

Not applicable.

Consent for publication

Not applicable as the manuscript does not contain any data from individual.

Ethics approval

Not applicable.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Bisht, A., Pundir, Y.P. & Pal, P.K. Performance analysis of nanosheet transistor with drain/source extension and high-k spacer optimizations for analog applications. Analog Integr Circ Sig Process 116, 35–47 (2023). https://doi.org/10.1007/s10470-023-02171-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-023-02171-x