Abstract

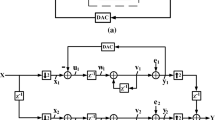

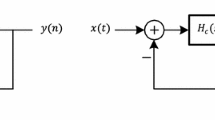

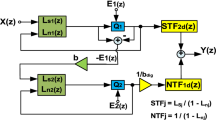

Among analog to digital converters, high speed ADCs are accomplished by the time interleaved delta-sigma modulators. The block digital filtering (BDF) method is a proper method to implement the Time-interleaved Delta-sigma modulators (TIDSM). In this method, M delta-sigma modulators are placed in parallel and the sampling rate in each of the parallel channel will be \({\mathrm{f}}_{\mathrm{s}}\),whereby the effective sampling rate become\(\mathrm{M}*{\mathrm{f}}_{\mathrm{s}}\). The serious disadvantage of the TIDSM based on BDF is that its NTF is equal to the standard structure. The time interleaved structure described in this paper is based on Noise Coupled time interleaved delta-sigma modulator (NC-TIDSM) that uses a noise-coupled between the channels. In this modulator not only the effective sampling is increased but also the overall noise transfer function order is increased by two or more without any additional active element. For implementation of the NC-TIDSM structure, the theoretical relations are proved and then these results have been verified by implementation of the second-order two-channel NC-TIDSM in circuit level and in an 180 nm CMOS technology. Using a 1.8 V supply, the SNDR of 62 dB in a 10 MHz signal band is achieved for the second-order two-channel NC-TIDSM.

Similar content being viewed by others

Data availability

The authors declare that the data supporting the findings and obtained during this research work are available within the paper.

References

Khoury, J., & Tao, H. (1998). Data converters for communication systems. IEEE Communications Magazine, 36, 113–117.

Maloberti, F. (2007) Data converters. Springer Science & Business Media.

Ren, F. J., Sarwana, S., Sahu, A., Talalaevskii, A., & Inamdar, A. (2015). Low-pass delta-delta-sigma ADC. IEEE Transactions on Applied Superconductivity, 25, 1–6.

Tao, S., & Rusu, A. (2015). A power-efficient CT incremental Σ∆ ADC for multi-channel neural recording systems. Review of IEEE Transactions on Circuits Systems: I Regular Papers, 62, 1–10.

Shanthi, P., Schreier, R., & Temes, G. C. (2017). Understanding delta-sigma data converters. New York: Wiley.

Moradi, R., Farshidi, E., & Soroosh, M. (2018). Digital calibration of memory errors in passive sigma-delta modulator. IETE Journal of Research, 2063, 1–8.

Balmelli, P., & Huang, Q. (2004) 4.2 A 25MS/s 14b 200mW Σ∆ Modulator in 0.18 µm CMOS, in Solid-State Circuits Conference, 2004. Digest of Technical Papers. ISSCC. 2004 IEEE International pp. 74–514.

Lee, H., Aurangozeb, Park, S., Kim, J., & Kim, C. (2014). A 6-bit 2.5-GS/s time-interleaved analog-to-digital converter using resistor-array sharing digital-to-analog converter. IEEE Transactions on Very Large Scale Integration Systems, 23, 1–13.

Bolatkale, M., Breems, L. J., Rutten, R., & Makinwa, K. A. A. (2011). A 4 GHz continuous-time ΔΣ ADC with 70 dB DR and -74 dBFS THD in 125 MHz BW. IEEE Journal of Solid-State Circuits, 46, 2857–2868.

Maghari, N., & Moon, U., (2014). Emerging analog-to-digital converters, in European Solid State Circuits Conference (ESSCIRC), ESSCIRC 2014–40th. IEEE, pp. 43–50.

Beydoun, A., Nguyen, V. T., & Loumeau, P. (2010). A novel digital calibration technique for gain and offset mismatch in parallel TIΣΔ ADCs, in ICASSP, IEEE International Conference on Acoustics, Speech and Signal Processing–Proceedings pp. 4158–4161.

Han, C., & Maghari, N. (2015). Time-interleaved noise-coupling delta-sigma modulator using modified noise-shaped integrating quantizer. IEEE Journal on Emerging and Selected Topics in Circuits, 5, 548–560.

Beydoun, A., Nguyen, V. T., Naviner, L., & Loumeau, P. (2013). Optimal digital reconstruction and calibration for multichannel time interleaved ΣΔ ADC based on comb-filters. AEU-International Journal of Electronics and Communications, 67, 329–339.

Lee, S., Chandrakasan, A. P., & Lee, H. (2014). A 1 GS/s 10b 18.9 mW time-interleaved SAR ADC with background timing skew calibration. IEEE Journal of Solid-State Circuits, 49, 2846–2856.

Abbaszadeh, A., Aghdam, E. N., & Rosado-Muñoz, A. (2019). Digital background calibration algorithm and its FPGA implementation for timing mismatch correction of time-interleaved ADC. Analog Integrated Circuits and Signal Processing, 9, 299–310.

Monsurrò, P., Rosato, F., & Trifiletti, A. (2018). New models for the calibration of four-channel time-interleaved ADCs using filter banks. IEEE Transactions on Circuits and Systems II: Express Briefs, 65, 141–145.

Eshraghi, A., & Fiez, T. S. (2004). A comparative analysis of parallel delta-sigma ADC architectures. IEEE Transactions on Circuits and Systems I: Regular Papers, 51, 450–458.

Kurosawa, N., Kobayashi, H., Maruyama, K., Sugawara, H., & Kobayashi, K. (2001). Explicit Analysis of channel mismatch effects in time-interleaved adc systems. IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, 48, 749–756.

Riewruja, V., & Chaikla, A. (2004). A high-speed algorithmic ADC. International Journal of Electronics, 91, 719–733.

Talebzadeh, J., & Kale, I. (2018). A novel two-channel continuous-time time-interleaved 3rd-order sigma-delta modulator with integrator-sharing topology. Analog Integrated Circuits and Signal Processing, 95, 375–385.

Aziz, P. M., Sorensen, H. V., & Van der Spiegel J. (1994). Multi band sigma delta analog to digital conversion, in Acoustics, Speech, and Signal Processing, 1994. ICASSP-94., 1994 IEEE International Conference, Vol. 3, pp. III/249-III/252.

Cormier, R. F., Sculley, T. L., & Bamberger R. H. (1994). Combining subband decomposition and sigma delta modulation for wideband A/D conversion, in Proceedings of IEEE International Symposium on Circuits and Systems-ISCAS ’94, pp. 357–360.

Galton, I., Jensen, H. T., & Member, S. (1995). Delta-sigma modulator based A/D conversion without oversampling. IEEE Transactions on Circuits and Systems, 42, 773–784.

Galton, I., & Jensen, H. (1996). Oversampling parallel delta-sigma modulator A/D conversion. IEEE Transactions on Circuits and Systems, 43, 801–810.

Khoini-poorfard, R., Lim, L. B., & Johns, D. A. (1997). Time-interleaved oversampling A/D converters: Theory and practice. IEEE Transactions on Circuits and Systems, 44, 634–645.

Prakash, J. A. V., Jose, B. R., Mathew, J., & Jose, B. A. (2017). A triple-mode hexa-standard reconfigurable TI cross-coupled ΣΔ modulator. International Journal of Electronics, 104, 1142–1160.

Lee, K. S., Choi, Y., & Maloberti, F. (2005). Domino free 4-path time-interleaved second order sigma-delta modulator. Analog Integrated Circuits and Signal Processing, 43, 225–235.

Razavi, B. (2013). Design considerations for interleaved ADCs. IEEE Journal of Solid-State Circuits, 48, 1806–1817.

Kozak, M., & Kale, I. (1999). A novel topology for time-interleaving in oversampling delta- sigma modulators, in 1999 Third International Conference on Advanced A/D and D/A Conversion Techniques and their Applications, pp. 27–28.

John, D., & Martin K. (2008) Analog Integrated Circuit Design. John Wiley & Sons

Yao Lu, C., Yu Hsieh, C., Liang Chen, H., & Shiun Chiang, J. in Proceedings A High-Resolution Time-Interleaved Delta-Sigma Modulator with Low Oversampling.

Abdoli, M., Najafi Aghdam, E., & Hemmati, F. (2020). A novel noise-coupled time-interleaved delta-sigma modulator with analysis of practical limitations. Analog Integrated Circuits and Signal Processing, 102, 389–401.

Abdoli, M., & Najafi Aghdam, E. (2020). Noise-coupled time-interleaved delta-sigma modulator with reduced hardware complexity. Journal of Circuits Systems and Computers, 30, 2150071.

Huang, Y. C., Wang, Z. G., Liu, W. F., & Zheng, X. (2011). Design of a delta-sigma modulator structured in MASH 2-1-2 with dither of error feedback. 2011 International Conference on Applied Superconductivity and Electromagnetic Devices, ASEMD 2011, (d), pp. 33–36. https://doi.org/10.1109/ASEMD.2011.6145061

Fitzgibbon, B., Member, S., & Kennedy, M. P. (2011). Calculation of cycle lengths in higher order error feedback modulators with constant inputs. IEEE Transactions On Circuits And Systems, 58(January), 6–10.

Teymouri, B., & Najafi Aghdam, E. (2015). Stability and sensitivity and optimization of delta sigma modulators, in 2015 23rd Iranian Conference on Electrical Engineering. pp. 1245–1248.

Funding

This research did not receive any specific grant from funding agencies in the public, commercial, or not-for-profit sectors.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Abdoli, M., Najafiaghdam, E. A second-order two-channel time-interleaved delta-sigma modulator circuit design. Analog Integr Circ Sig Process 112, 457–466 (2022). https://doi.org/10.1007/s10470-022-02066-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-022-02066-3