Abstract

This paper presents a single-stage bulk-driven double recycling low-voltage low-power operational transconductance amplifier (OTA) operating in subthreshold region. The proposed OTA utilizes double recycling topology and provides enough open loop voltage gain, slew rate, and unity gain frequency (UGF). The flipped voltage follower-based adaptively biased input differential pair working in class AB mode has ensured dynamic current boosting and increased slew rate. Further, the proposed OTA has utilized partial positive feedback to mitigate some of the performance reduction caused by the bulk-driven topology. The simulation results of the proposed OTA have ensured open loop gain of 79.5 dB, UGF of 37.1 kHz, and phase margin of 64°. It operates with dual power supply of ± 0.25 V and consumes low power of 60 nW. These performance parameters validate its usefulness for LV, LP and low-frequency applications. The process, voltage, and temperature variation effects on low-frequency voltage gain, UGF, and phase margin of the proposed OTA has also been investigated with process corner simulations. The proposed OTA is designed and simulated in UMC 180 nm standard n-tub bulk CMOS process technology utilizing Tanner EDA tools.

Similar content being viewed by others

References

Cabrera-Bernal, E., Pennisi, S., Grasso, A. D., Torralba, A., & Carvajal, R. G. (2016). 0.7-V three-stage class-AB CMOS operational transconductance amplifier. IEEE Transactions on Circuits and Systems I: Regular Papers, 63(11), 1807–1815.

Chatterjee, S., Tsividis, Y., & Kinget, P. (2005). 0.5-V analog circuit techniques and their application in OTA and filter design. IEEE Journal of Solid-State Circuits, 40(12), 2373–2387.

Blalock, B. J., Allen, P. E., & Rincon-Mora, G. A. (1998). Designing 1-V op amps using standard digital CMOS technology. IEEE Transactions Circuits Systems II: Analog and Digital Signal Processing, 45(7), 769–780.

Ferreira, L. H. C., & Sonkusale, S. R. (2014). A 60-dB gain OTA operating at 0.25-V power supply in 130-nm digital CMOS process. IEEE Transactions on Circuits and Systems I: Regular Papers, 61(6), 1609–1617.

Yao, L., Steyaert, M., & Sansen, W. (2004). A 1-V 140-µW 88 dB audio sigma-delta modulator in 90-nm CMOS. IEEE Journal of Solid-State Circuits, 39(11), 1809–1818.

Harrison, R. R., & Charles, C. (2003). A low-power low-noise CMOS amplifier for neural recording applications. IEEE Journal of Solid-State Circuits, 38(6), 958–965.

Sharan, T., Chetri, P., & Bhadauria, V. (2018). Ultra-low-power bulk-driven fully differential subthreshold OTAs with partial positive feedback for Gm-C filters. Analog Integrated Circuits and Signal Processing, 94(3), 427–447.

Ferreira, L. H. C., Pimenta, T. C., & Moreno, R. L. (2007). An ultra-low-voltage ultra-low-power CMOS Miller OTA with rail-to-rail input/output swing. IEEE Transactions on Circuits and Systems II: Express Briefs, 54(10), 843–847.

Assaad, R. S., & Silva-Martinez, J. (2009). The recycling folded cascode: A general enhancement of the folded cascode amplifier. IEEE Journal of Solid-State Circuits, 44(9), 2535–2542.

Yao, L., Steyaert, M., & Sansen, W. (2004). A 0.8-V, 8-µW, CMOS OTA with 50-dB gain and 1.2-MHz GBW in 18-pF load. In Proceedings of 29th European solid-state circuits conference, Estoril, Portugal (pp. 297–300). https://doi.org/10.1109/esscirc.2003.1257131.

Roh, J. (2006). High-gain class-AB OTA with low quiescent current. Analog Integrated Circuits and Signal Processing, 47(2), 225–228.

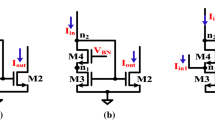

Yan, Z., Mak, P. I., & Martins, R. P. (2012). Double recycling technique for folded-cascode OTA. Analog Integrated Circuits and Signal Processing, 71(1), 137–141.

Yan, Z., Mak, P. I., Law, M.-K., Martins, R. P., & Maloberti, F. (2015). Nested-current-mirror rail-to-rail-output single-stage amplifier with enhancements of DC gain, GBW and slew rate. IEEE Journal of Solid-State Circuits, 50(10), 2353–2366.

Baswa, S., Lopez-Marin, A. J., Angulo, J. R., & Carvajal, R. G. (2004). Low-voltage micropower super class AB CMOS OTA. Electronics Letters, 40(4), 216–217.

Baswa, S., Lopez-Martin, A., Ramirez-Angulo, J., & Carvajal, R. G. (2006). Winner-take-all class AB input stage. Analog Integrated Circuits and Signal Processing, 46(2), 149–152.

Lopez-Marin, A. J., Baswa, S., Angulo, J. R., & Carvajal, R. G. (2005). Low-voltage super class AB CMOS OTA cells with very high slew rate and power efficiency. IEEE Journal of Solid-State Circuits, 40(5), 1068–1078.

Ramirez-Angulo, J., Carvajal, R. G., Torralba, A., & Nieva, C. (2001). A new class AB differential input stage for implementation of low-voltage high slew-rate op-amps and linear transconductors. In Proceedings of international symposium on circuits and systems (ISCAS), Sydney, Australia (Vol. 1, pp. 671–674).

Raikos, G., & Vlassis, S. (2010). 0.8 V bulk-driven operational amplifier. Analog Integrated Circuits and Signal Processing, 63(3), 425–432.

Sharan, T., & Bhadauria, V. (2016). Sub-threshold, cascode compensated, bulk-driven OTAs with enhanced gain and phase-margin. Microelectronics Journal, 54, 150–165.

Carrillo, J. M., Torelli, G., Pérez-Aloe, R., & Carrillo, J. F. D. (2007). 1-V rail-to-rail CMOS OpAmp with improved bulk-driven input stage. IEEE Journal of Solid-State Circuits, 42, 508–517.

Wang, R., & Harjani, R. (1995). Partial positive feedback for gain enhancement of low-power CMOS OTAs. Analog Integrated Circuits and Signal Processing, 8(1), 21–35.

Wen, B., Zhang, Q., & Zhao, X. (2019). A two-stage CMOS OTA with enhanced transconductance and DC-gain. Analog Integrated Circuits and Signal Processing, 98(2), 257–264.

Carvajal, R. G., Angulo, J. R., Martin, A. J. L., Torralba, A., Galan, J. A. G., Carlosena, A., et al. (2005). The flipped voltage follower: A useful cell for low-voltage, low-power circuit design. IEEE Transaction on Circuits and Systems-I-Regular Papers, 52(7), 1276–1291.

Yodtean, A., & Thanchayanont, A. (2013). Sub 1–V highly linear low power class AB bulk driven tunable CMOS transconductor. Analog Integrated Circuits and Signal Processing, 75(3), 383–397.

Lv, X., Zhao, X., Wang, Y., & Jia, D. (2018). Super class AB-AB bulk-driven folded cascode OTA. Integration, the VLSI Journal, 63, 196–203.

Veldandi, H., & Shaik, R. A. (2017). An Ultra-low-voltage bulk-driven analog voltage buffer with rail-to-rail input/output range. Circuits, Systems, and Signal Processing, 36(12), 4886–4907.

Yavari, M. (2005). Hybrid cascode compensation for two-stage CMOS op-amps. IEICE Transactions Electronics, 88(6), 1161–1165.

Anisheh, S. M., Shamsi, H., & Mitra, M. (2017). Positive feedback technique and split-length transistors for DC-gain enhancement of two-stage op-amps. IET Circuits, Devices and Systems, 11(6), 605–612.

Kulej, T. (2015). 0.5-V bulk-driven OTA and its applications. International Journal of Circuit Theory and Applications, 43(2), 187–204.

Binkley, D. M. (2008). Tradeoffs and optimization in analog CMOS design (pp. 47, 197, 207–209, 497, 501). New York: Wiley.

Carrillo, J. M., Torelli, G., Pérez-Aloe, R., & Carrillo, J. F. D. (2011). Transconductance enhancement in bulk-driven input stages and its applications. Analog Integrated Circuits and Signal Processing, 68(2), 207–217.

Akbari, M., Hashemipour, O., Moaiyeri, M. H., & Aghajani, A. (2017). An efficient approach to enhance bulk-driven amplifiers. Analog Integrated Circuits and Signal Processing, 92(3), 489–499.

Ghaemnia, A., & Hashemipour, O. (2019). An ultra-low power high gain CMOS OTA for biomedical applications. Analog Integrated Circuits and Signal Processing, 99(3), 529–537.

Sharan, T., & Bhadauria, V. (2017). Fully differential, bulk-driven, class AB, sub-threshold OTA with enhanced slew rates and gain. Journal of Circuits, Systems and Computers, 26(01), 1750001.

Kulej, T., & Khateb, F. (2018). Design and implementation of sub 0.5 V OTAs in 0.18 μm CMOS. International Journal of Circuit Theory and Applications, 46(6), 1129–1143.

Kulej, T., & Khateb, F. (2020). A compact 0.3-V Class AB bulk-driven OTA. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 28(1), 224–232.

Kulej, T., & Khateb, F. (2020). A 0.3-V 98-dB rail-to-rail OTA in 0.18 µm CMOS. IEEE Access, 8, 27459–27467.

Acknowledgements

This work has been performed using the resources of PG Lab2 of ECE Department of NERIST, Nirjuli. The simulations has been performed using Tanner EDA tools provided under TEQIP-II project funded by Department of Information Technology, Ministry of Communication and Information Technology Government of India at NERIST, Nirjuli, Arunachal Pradesh, 791109, India.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that there is no conflict of interest regarding the publication of this work.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendix

Appendix

1.1 The inoise contribution of proposed OTA

The input referred thermal noise and flicker noise should be low for a low-voltage OTA cell. The first one has a flat power spectral density (PSD) whereas latter one is frequency dependent and is predominant in low frequency regions [30]. The noise may either be referred to input terminal (gate or bulk) of a MOS device called inoise or may be referred at output node of an amplifier called onoise. The bulk-driven input stage results in more input referred noise as compared to gate-driven circuit since gmb < gm. So, noise PSD at gate terminal is η2 times of the noise PSD at bulk terminal of PMOS input pair where η = (np− 1) is its gmb/gm ratio. The onoise PSD at drain terminal in squared mean current form (A2/Hz) is given by (21) [7, 30]:

where (npГ) is product of substrate and thermal noise factors, K’FP is flicker noise factor in fluctuation noise model (see on pp. 197, 207–209 of [30]) having unit of (nA . µm)2 for \(\overline{{i_{snD}^{2} }}\) and (nV . µm)2 for \(\overline{{V_{snG}^{2} }}\) and is related to KFP of other noise model as K’FP= KFP/C 2ox , the f is frequency, (WL)i is the area of a concerned MOS transistor and other notations have their usual meanings as described in [30].

The value of Г is 1/2 [30] and gmi is \(\left( {{{i_{Di} } \mathord{\left/ {\vphantom {{i_{Di} } {n_{p} U_{T} }}} \right. \kern-0pt} {n_{p} U_{T} }}} \right)\), in weak inversion region of operation, so (21) could be expressed as (22),

where q is the unit charge of an electron and gmi is the gate transconductance of ith MOSFET. The total noise voltage PSD [7, 30] at bulk-terminal \(\overline{{V_{snB}^{2} }}\) could be expressed as (23)

where gmbi is bulk-transconductance of input pair. However, if the effective transconductance gain of the input pair MOSFETs at bulk-input terminal be Gmeff, then its drain current PSD when referred to input terminal can be expressed as (24):

The value of \(g_{mi}^{2} = {{i_{Di}^{2} } \mathord{\left/ {\vphantom {{i_{Di}^{2} } {n_{p}^{2} }}} \right. \kern-0pt} {n_{p}^{2} }}\,U_{T}^{2}\) so, the (24) can be written as (25).

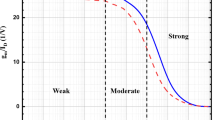

The overall thermal noise PSD (in unit of V2/Hz) in weak inversion region operated double recycling core (within blue box of Fig. 2) including PA4, PB4 as well and assuming that there is a constant current source in place of FVF (red box Fig. 2), is approximated to (26):

where A = 2, B = 3, C = 1, D = 3, E = 1 and F = 6 and PPF factor K = 0.7 [20]. Applying these values in (26) thermal noise is given by (27)

Thus, its thermal noise contribution can be reduced by increasing the Gmeff of OTA, i.e. by biasing the CMOS devices at high bias current.

Similarly, presenting the flicker noise and subthreshold slope factors of the NMOS transistors as \(K_{FN}^{'}\) and nn the flicker noise PSD of double recycling core in unit of V2/Hz could be approximated to (28):

Thus, its Flicker noise PSD can be reduced by increasing the Gmeff and size of each MOS transistors.

In DRCM-ST the constant current source in Fig. 1 has been replaced by FVF cell which additionally contributes [7, 30] its own noise. The thermal noise contribution of this FVF is shown in (29). In (29) the degeneration effect (see Fig. 12) of RS is considered for noise contribution of PA5 and equivalent resistor RS itself (see pages 497–502 of [30]).

where RS = 1/Gme, in (29) and Fig. 12. In (29) first and second terms present the thermal noise of PA6 and NA7. The third term presents the thermal noise contribution of PA5 and fourth term presents the noise of equivalent resistor RS [7, 30].

Similarly, the flicker noise contributed by FVF cell can be presented as (30):

In (30) the first and second terms present the flicker noise of PA6 and NA7, respectively. The third term presents the flicker noise contribution of PA5 [7, 30].

Rights and permissions

About this article

Cite this article

Deo, N., Sharan, T. & Dubey, T. Subthreshold biased enhanced bulk-driven double recycling current mirror OTA. Analog Integr Circ Sig Process 105, 229–242 (2020). https://doi.org/10.1007/s10470-020-01689-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01689-8