Abstract

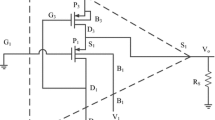

Biopotential amplifier (BPA) remains one of the most crucial blocks for the successful implementation of any of the biomedical systems. However, design of a BPA remains challenging owing to most of the topologies reported in literature displaying high values of noise, consuming high value of power and working in limited range of bandwidth. Thus, circuit topologies capable of providing an optimum and an acceptable combination of these parameters remains a topic of immense interest among researchers. We in this paper, report the results of a BPA designed using Bulk-Driven Quasi-Floating Gate (BDQFG) technique with a special focus on the effect of variation in the values of biasing resistor (Rlarge). Results obtained through mathematical modelling and analysis of the circuit have been verified by conducting simulations in Cadence Analog Design Environment using standard 0.18 µm technology. Circuit design has been optimized for least values of power consumption of the order of 1.1 µW, noise (≈ 3.15 µVRMS), mid-band gain of 39.9 dB (from 0.266 Hz to f-3dB of 2.8 kHz), offset voltage of 455 μV and phase margin of 65.83°.

Similar content being viewed by others

References

Chen, W. M., Yang, W. C., Tsai, T. Y., Chiueh, H., & Wu, C. Y. (2011, August). The design of CMOS general-purpose analog front-end circuit with tunable gain and bandwidth for biopotential signal recording systems. In 2011 Annual International Conference of the IEEE Engineering in Medicine and Biology Society (pp. 4784–4787). https://doi.org/10.1109/iembs.2011.6091185.

Holleman, J. (2016, August). Design considerations for neural amplifiers. In 2016 38th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC) (pp. 6331–6334). https://doi.org/10.1109/embc.2016.7592176.

Mollazadeh, M., Murari, K., Cauwenberghs, G., & Thakor, N. (2008, August). From spikes to EEG: Integrated multichannel and selective acquisition of neuropotentials. In 2008 30th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (pp. 2741–2744). https://doi.org/10.1109/iembs.2008.4649769.

Sharma, K., & Sharma, R. (2019). Design considerations for effective neural signal sensing and amplification: a review. Biomedical Physics & Engineering Express,5(4), 1–28. https://doi.org/10.1088/2057-1976/ab1674.

Chandrakumar, H., & Marković, D. (2017). A high dynamic-range neural recording chopper amplifier for simultaneous neural recording and stimulation. IEEE Journal of Solid-State Circuits,52(3), 645–656. https://doi.org/10.1109/JSSC.2016.2645611.

Wu, C. Y., Cheng, C. H., & Chen, Z. X. (2018). A 16-channel CMOS chopper-stabilized analog front-end ECoG acquisition circuit for a closed-loop epileptic seizure control system. IEEE Transactions on Biomedical Circuits and Systems,12(3), 543–553. https://doi.org/10.1109/TBCAS.2018.2808415.

Xu, J., Konijnenburg, M., Ha, H., VanWegberg, R., Song, S., Blanco-Almazan, D., et al. (2018). A 36 μW 11 mm 2 reconfigurable analog front-end for cardiovascular and respiratory signals recording. IEEE Transactions on Biomedical Circuits and Systems,12(4), 774–783. https://doi.org/10.1109/tbcas.2018.2814699.

Gosselin, B. (2011). Recent advances in neural recording microsystems. Sensors,11(5), 4572–4597. https://doi.org/10.3390/s110504572.

Harrison, R. R., & Charles, C. (2003). A low-power low-noise CMOS amplifier for neural recording applications. IEEE Journal of Solid-State Circuits,38(6), 958–965. https://doi.org/10.1109/JSSC.2003.811979.

Mohseni, P., & Najafi, K. (2004). A fully integrated neural recording amplifier with DC input stabilization. IEEE Transactions on Biomedical Engineering,51(5), 832–837. https://doi.org/10.1109/TBME.2004.824126.

Wattanapanitch, W., Fee, M., & Sarpeshkar, R. (2007). An energy-efficient micropower neural recording amplifier. IEEE Transactions on Biomedical Circuits and Systems,1(2), 136–147. https://doi.org/10.1109/TBCAS.2007.907868.

Gosselin, B., Ayoub, A. E., Roy, J. F., Sawan, M., Lepore, F., Chaudhuri, A., et al. (2009). A mixed-signal multichip neural recording interface with bandwidth reduction. IEEE Transactions on Biomedical Circuits and Systems,3(3), 129–141. https://doi.org/10.1109/TBCAS.2009.2013718.

Ng, K. A., & Xu, Y. P. (2013). A compact, low input capacitance neural recording amplifier. IEEE Transactions on Biomedical Circuits and Systems,7(5), 610–620. https://doi.org/10.1109/TBCAS.2013.2280066.

Denison, T., Consoer, K., Santa, W., Avestruz, A. T., Cooley, J., & Kelly, A. (2007). A 2 μw, 100 nV/rtHz chopper-stabilized instrumentation amplifier for chronic measurement of neural field potentials. IEEE Journal of Solid-State Circuits,42(12), 2934–2945. https://doi.org/10.1109/JSSC.2007.908664.

Ng, K. A., & Chan, P. K. (2005). A CMOS analog front-end IC for portable EEG/ECG monitoring applications. IEEE Transactions on Circuits and Systems I: Regular Papers,52(11), 2335–2347. https://doi.org/10.1109/TCSI.2005.854141.

Farshchi, S., Pesterev, A., Nuyujukian, P., Guenterberg, E., Mody, I., & Judy, J. W. (2010). Embedded neural recording with TinyOS-based wireless-enabled processor modules. IEEE Transactions on Neural Systems and Rehabilitation Engineering,18(2), 134–141. https://doi.org/10.1109/TNSRE.2009.2039606.

Ferreira, L. H., Pimenta, T. C., & Moreno, R. L. (2007). An ultra-low-voltage ultra-low-power CMOS miller OTA with rail-to-rail input/output swing. IEEE Transactions on Circuits and Systems II: Express Briefs,54(10), 843–847. https://doi.org/10.1109/TCSII.2007.902216.

Lee, J. Y., & Hwang, S. N. (2008). A high-gain boost converter using voltage-stacking cell. The Transactions of the Korean Institute of Electrical Engineers,57(6), 982–984. https://doi.org/10.1049/el:20080371.

Mollazadeh, M., Murari, K., Cauwenberghs, G., & Thakor, N. (2009). Micropower CMOS integrated low-noise amplification, filtering, and digitization of multimodal neuropotentials. IEEE Transactions on Biomedical Circuits and Systems,3(1), 1–10. https://doi.org/10.1109/TBCAS.2008.2005297.

Shahrokhi, F., Abdelhalim, K., Serletis, D., Carlen, P. L., & Genov, R. (2010). The 128-channel fully differential digital integrated neural recording and stimulation interface. IEEE Transactions on Biomedical Circuits and Systems,4(3), 149–161. https://doi.org/10.1109/TBCAS.2010.2041350.

Wang, T. Y., Liu, L. H., & Peng, S. Y. (2015). A power-efficient highly linear reconfigurable biopotential sensing amplifier using gate-balanced pseudoresistors. IEEE Transactions on Circuits and Systems II: Express Briefs,62(2), 199–203. https://doi.org/10.1109/TCSII.2014.2387685.

Ng, K. A., & Xu, Y. P. (2016). A low-power, high CMRR neural amplifier system employing CMOS inverter-based OTAs with CMFB through supply rails. IEEE Journal of Solid-State Circuits,51(3), 724–737. https://doi.org/10.1109/JSSC.2015.2512935.

Khateb, F., Dabbous, S. B. A., & Vlassis, S. (2013). A survey of non-conventional techniques for low-voltage low-power analog circuit design. Radioengineering,22(2), 415–427.

Khateb, F., Vlassis, S., Kumngern, M., Psychalinos, C., Kulej, T., Vrba, R., et al. (2015). 1 V rectifier based on bulk-driven quasi-floating-gate differential difference amplifiers. Circuits, Systems, and Signal Processing,34(7), 2077–2089. https://doi.org/10.1007/s00034-014-9958-3.

Kumngern, M., & Khateb, F. (2016). 0.5 V fully differential current conveyor using bulk-driven quasi-floating-gate technique. IET Circuits, Devices and Systems,10(1), 78–86. https://doi.org/10.1049/iet-cds.2014.0260.

Harrison, R. R. (2008). The design of integrated circuits to observe brain activity. Proceedings of the IEEE,96(7), 1203–1216. https://doi.org/10.1109/JPROC.2008.922581.

Khateb, F. (2014). Bulk-driven floating-gate and bulk-driven quasi-floating-gate techniques for low-voltage low-power analog circuits design. AEU-International Journal of Electronics and Communications,68(1), 64–72. https://doi.org/10.1016/j.aeue.2013.08.019.

Rezaee-Dehsorkh, H., Ravanshad, N., Lotfi, R., Mafinezhad, K., & Sodagar, A. M. (2011). Analysis and design of tunable amplifiers for implantable neural recording applications. IEEE Journal on Emerging and Selected Topics in Circuits and Systems,1(4), 546–556. https://doi.org/10.1109/JETCAS.2011.2174492.

Cortes, F. P., Fabris, E., & Bampi, S. (2004). Analysis and design of amplifiers and comparators in CMOS 0.35 μm technology. Microelectronics Reliability,44(4), 657–664. https://doi.org/10.1016/j.microrel.2003.10.014.

Sharma, K., & Sharma, R. (2017). Highly consistent bulk driven quasi floating gate (BDQFG) PMOS pseudo-resistor design and implementation in 0.18 micron meter technology. In TENCON 2017- IEEE Region 10 Conference (pp. 488–493). https://doi.org/10.1109/tencon.2017.8227913.

Ozalevli, E., & Hasler, P. E. (2008). Tunable highly linear floating-gate CMOS resistor using common-mode linearization technique. IEEE Transactions on Circuits and Systems I: Regular Papers,55(4), 999–1010. https://doi.org/10.1109/TCSI.2008.916459.

Kassiri, H., Abdelhalim, K., & Genov, R. (2013, October). Low-distortion super-GOhm subthreshold-MOS resistors for CMOS neural amplifiers. In 2013 IEEE Biomedical Circuits and Systems Conference (BioCAS) (pp. 270–273). https://doi.org/10.1109/biocas.2013.6679691.

Dwivedi, S., & Gogoi, A. K. (2015, February). Local field potential measurement with low-power area-efficient neural recording amplifier. In 2015 IEEE International Conference on Signal Processing, Informatics, Communication and Energy Systems (SPICES) (pp. 1–5). https://doi.org/10.1109/spices.2015.7091507.

Laskar, N. M., Guha, K., Nath, S., Chanda, S., Baishnab, K. L., Paul, P. K., et al. (2018). Design of high gain, high bandwidth neural amplifier IC considering noise-power trade-off. Microsystem Technologies. https://doi.org/10.1007/s00542-018-4142-5.

Acknowledgement

Authors would like to thank Vice Chancellor, Chitkara University for all the support to carry out this work and also provide financial support to student authors - Preeti and Kulbhushan. Sharing of Technical knowhow by SCL team members is also deeply acknowledged.

Author information

Authors and Affiliations

Corresponding authors

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sharma, P., Sharma, K., Jatana, H.S. et al. A 1.1 μW biopotential amplifier based on bulk-driven quasi-floating gate technique with extremely low-value of offset voltage. Analog Integr Circ Sig Process 103, 303–313 (2020). https://doi.org/10.1007/s10470-020-01623-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01623-y