Abstract

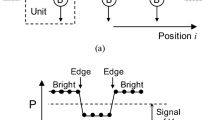

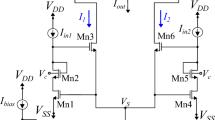

In this paper, a unique biologically inspired retina circuit architecture providing Laplacian filter based analog image processing has been suggested. A digital image filtering method is utilized for this aim. Convolution theory and masking technique have an important place among digital image processing methods. These two mathematical operations can be easily done with basic electronic circuit structures. We use current mirrors and current subtractor circuit for the purpose of performing convolution by the use of masking technique on any image. The concept of human retina is able to be mimicked by the help of using silicon circuits. A retina construction can be thought as a group of pixel structures. Because of this reason, we first design a novel pixel circuit as a subcircuit for the retina structure. Our new retina-inspired neuromorphic pixel consists of only 8 MOS transistors. Then, 10 k identical pixel circuits are united together with the help of proper subcircuit connections to achieve a retina structure of size 100 × 100 pixels which enables edge detection feature on images thanks to Laplacian filtering. We compare the analysis results of our grid retina circuit with the theoretical Laplacian filter method used in digital image processing. We obtain analysis results of four different grayscale images that agree well with the expected theoretical results for Laplacian filtering.

Similar content being viewed by others

References

Shepherd, G. M. (2003). The synaptic organization of the brain. Oxford: Oxford University Press.

van Hateren, J. H. (1992). A theory of maximizing sensory information. Biological Cybernetics, 68(1), 23–29.

Zaghloul, K. A., & Boahen, K. (2004). Optic nerve signals in a neuromorphic chip I: Outer and inner retina models. IEEE Transactions on Biomedical Engineering, 51(4), 657–666.

Cook, P. B., & McReynolds, J. S. (1998). Lateral inhibition in the inner retina is important for spatial tuning of ganglion cells. Nature Neuroscience, 1(8), 714.

Indiveri, G., Linares-Barranco, B., Hamilton, T. J., et al. (2011). Neuromorphic silicon neuron circuits. Frontiers in Neuroscience, 5, 73.

Mead, C. (1990). Neuromorphic electronic systems. Proceedings of the IEEE, 78(10), 1629–1636.

Babacan, Y., Kaçar, F., & Gürkan, K. (2016). A spiking and bursting neuron circuit based on memristor. Neurocomputing, 203, 86–91.

Babacan, Y., & Kaçar, F. (2017). Memristor emulator with spike-timing-dependent-plasticity. AEU-Int. J. Electron. Commun., 73, 16–22.

Irizarry-Valle, Y., & Parker, A. C. (2015). An astrocyte neuromorphic circuit that influences neuronal phase synchrony. IEEE Transactions on Biomedical Circuits and Systems, 9(2), 175–187.

Li, Z., Liu, C., Wang, Y., et al. (2015). An overview on memristor crossabr based neuromorphic circuit and architecture. In IEEE/IFIP International Conference on VLSI Syst. VLSI-SoC (pp. 52–56).

Barzegarjalali, S., Parker, A. C. (2016). A neuromorphic circuit mimicking biological short-term memory. In Proceedings of the Annual International Conference of the IEEE Engineering in Medicine Biology Society EMBS (pp. 1401–1404).

Yoon, K., Choi, S., Shin, Y. (2016). Area efficient neuromorphic circuit based on stochastic computation. In ISOCC 2016—Intenational SoC Design Conference Smart SoC Intelligent Things, 2016 (pp. 73–74).

Barzegarjalali, S., Parker, A. C., Fellow, L. (2016). Noisy neuromorphic circuit modeling obsessive compulsive disorder. In 29th IEEE International System-on-Chip Conference (SOCC), 2016 (pp. 327–332) IEEE.

Zhang, J., Wang, Y., Zhang, X., Huang, R. (2017) Compact digital-controlled neuromorphic circuit with low power consumption. In IEEE International Symposium on Circuits Systems (pp. 1–4).

Fayyazi, A., Ansari, M., Kamal, M., Afzali-Kusha, A., & Pedram, M. (2018). An ultra low-power memristive neuromorphic circuit for internet of things smart sensors. IEEE Internet Things J, 5(2), 1011–1022.

Mahowald, M. A., & Mead, C. (1991). The silicon retina, 264, 76–82.

Zaghloul, K. A., & Boahen, K. (2006). A silicon retina that reproduces signals in the optic nerve. Journal of Neural Engineering, 3(4), 257.

Mhani, A., Bouvier, G., Herault, J. (1995). A contrast and motion-sensitive silicon retina. In ESSCIRC’95 Twenty-first European Solid-State Circuits Conference (pp. 326–329).

Andreou, A. G., Boahen, K. A. (1994). A 48,000 pixel, 590,000 transistor silicon retina in current-mode subthreshold CMOS. In Proceedings of the 37th Midwest Symposium onCircuits and Systems (pp. 97–102).

Publio, R., Oliveira, R. F., & Roque, A. C. (2006). A realistic model of rod photoreceptor for use in a retina network model. Neurocomputing, 69(10), 1020–1024.

Cosp, J., Madrenas, J., & Fernández, D. (2006). Design and basic blocks of a neuromorphic VLSI analogue vision system. Neurocomputing, 69(16–18), 1962–1970.

Delbruck, T. (1993). Silicon retina with correlation-based, velocity-tuned pixels. IEEE Transaction on Neural Networks, 4(3), 529–541.

Ahmadi, H., Sayedi, S. M. (2012). Design of a neuromorphic edge detector vision chip with color and intensity change disambiguation. In 25th IEEE Canadian Conference (IEEE, 2012) on Electrical & Computer Engineering (CCECE) (pp. 1–5).

Chiang, C. T., & Wu, C. Y. (2004). Implantable neuromorphic vision chips. Electronics Letters, 40(6), 361–363.

Yildirim, M., Babacan, Y., & Kacar, F. (2018). Memristive retinomorphic grid architecture removing noise and preserving edge. AEU - International Journal of Electronics and Communications, 97, 38–44.

Boahen, K. (1996). Retinomorphic vision systems. Microelectronics for neural networks. In Proceedings of Fifth International Conference (IEEE, 1996) (pp. 2–14).

Siskos, S. (2010). Low voltage analog median filters implementation. In 2010 Proceedings of the IEEE International Conference on Imaging Systems and Techniques, IST 2010 (pp. 166–170).

Taguchi, T., Ogawa, M., Shibata, T. (2003). An analog image processing LSI employing scanning line-parallel processing. In European Solid-State Circuits Conference (pp. 65–68).

Shimmi, T., Kobayashi, H., Yagi, T., Sawaji, T., Matsumoto, T., Abidi, A.A. (1992). A parallel analog CMOS signal processor for image contrast enhancement. In ESSCIRC’92 Eighteenth European Solid-State Circuits Conference (pp. 163–166).

Vornicu, I., Goraş, L. (2010). Image processing using a CMOS analog parallel architecture. In CAS 2010 Proceedings International Semiconductor Conference (pp. 461–464).

Marr, D., & Hildreth, E. (1980). Theory of edge detection. Proceedings of the Royal Society B: Biological Sciences, 207(1167), 187–217.

Almazrooie, M., Venkat, I. (2014). Parallel Laplacian Filter using CUDA on GP-GPU’2014 (pp. 60–65).

Hajiaboli, M. R., Ahmad, M. O., & Wang, C. (2012). An edge-adapting Laplacian Kernel for nonlinear diffusion filters. IEEE Transactions on Image Processing, 21(4), 1561–1572.

Shen, D. F., Chiu, C. W., Huang, P. J. (2006). Modified Laplacian Filter and intensity correction technique for image resolution enhancement. In Proceedings of the IEEE International Conference on Multimedia and Expo, ICME 2006 (pp. 457–460).

Gonzalez, R. C., & Woods, R. E. (2002). Digital image processing. Beijing: Publishing House of Electronics Industry.

Sasivarnan, C., Jagan, A., Kaur, J., Jyoti, D., & Rao, D. S. (2011). Image quality assessment techniques pn spatial domain. IJCST., 2(3), 177–184.

Wang, Z., Bovik, A. C., Sheikh, H. R., & Simoncelli, E. P. (2004). Image quality assessment: from error visibility to structural similarity. IEEE Transactions on Image Processing, 13(4), 600–612.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Yildirim, M., Kacar, F. Adapting Laplacian based filtering in digital image processing to a retina-inspired analog image processing circuit. Analog Integr Circ Sig Process 100, 537–545 (2019). https://doi.org/10.1007/s10470-019-01481-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01481-3