Abstract

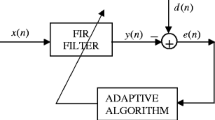

An adaptive decision feedback equalizer (DFE) in 0.18 µm CMOS process for 2.5 GB/s data rate is proposed in this paper which is comprised of three taps. Adaptive DFE circuit is used for the purpose of automatic inter-symbol interference cancellation in cords with different lengths. The status of the high frequency components and low frequency components (LFC) of the signal adjust the coefficient of each tap continuously in online manner. In order to extract the clock, the clock and data recovery circuit is interfused within the DFE. Using the proposed DFE, the status of eye diagram varies from the almost closed to wide open. Total power consumption of the receiver circuit is approximately 50 mW and it occupies the area about 350 µm × 350 µm. Simplicity and less hardware requirements are features of the designed circuit in comparison with the similar circuits.

Similar content being viewed by others

References

Emami-Neyestanak, A., Varzaghani, A., Bulzacchelli, J., Rylyakov, A., Ken Yang, Ch., & Friedman, D. (2007). A 6.0-mW 10.0-Gb/s receiver with switched-capacitor summation DFE. IEEE Journal of Solid-State Circuits, 42(4), 889–896.

Lee, J. (2006). A 20-Gb/s adaptive equalizer in 0.13-um CMOS technology. IEEE Journal of Solid-State Circuits, 41(9), 2058–2066.

Jackie Wong, K., Rylyakov, A., & Ken Yang, Ch. (2007). A 5-mW 6-Gb/s quarter-rate sampling receiver with a 2-tap DFE using soft decisions. IEEE Journal of Solid-State Circuits, 42(4), 881–888.

Kim, B., Liu, Y., Dickson, T., Bulzacchelli, J., & Friedman, D. (2009). A 10-Gb/s compact low-power serial I/O with DFE-IIR equalization in 65-nm CMOS. IEEE Journal of Solid-State Circuits, 44(12), 3526–3538.

Wang, H., & Lee, J. (2010). A 21-Gb/s 87-mW transceiver with FFE/DFE/analog equalizer in 65-nm CMOS technology. IEEE Journal of Solid-State Circuits, 45(4), 909–920.

Proakis, J. (2007). Digital communications (4th ed., p. 621). New York: McGraw-Hill Education.

Moradi, T., Naghavi, S., Nematzade, M., Hadidi, Kh, Abrishamifar, A., & Khoei, A. (2014). A fast and low settling error continuous-time common-mode feedback circuit based in differential difference amplifier. Journal of Circuits, Systems, and Computers, 1, 1. https://doi.org/10.1142/S0218126614500650.

Gondi, S., & Razavi, B. (2007). Equalization and clock and data recovery techniques for 10-Gb/s CMOS serial-link receivers. IEEE Journal of Solid-State Circuits, 42(9), 1999–2011.

Kim, Y. H., Kim, Y. J., Lee, T. H., & Kim, L. S. (2015). An 11.5 Gb/s 1/4th baud-rate CTLE and two-tap DFE with boosted high frequency gain in 110-nm CMOS. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 23(3), 588–592.

Seong, Ch K, Rhim, J., & Choi, W. Y. (2012). A 10-Gb/s adaptive look-ahead decision feedback equalizer with an eye-opening monitor. IEEE Transactions on Circuit and Systems—II: Express Briefs, 59(4), 209–213.

Al-Taee, A. R., Yuan, F., & Ye, A. (2015). Adaptive decision feedback equalizer with hexagon EOM and jitter detection. Circuits, Systems, and Signal Processing(CSSP), 37(5), 2487–2501.

Yong-Hun, K., Young-Ju, K., Taeho, L., & Lee-Sup, K. (2015). A 21-Gbit/s 1.63-pJ/bit adaptive CTLE and one-tap DFE with single loop spectrum balancing method. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 24(2), 789–793.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Babazadeh, A., Moradi Khanshan, T. & Esmaili, A. An improved adaptive DFE structure based on ISI detection. Analog Integr Circ Sig Process 100, 453–468 (2019). https://doi.org/10.1007/s10470-019-01437-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01437-7