Abstract

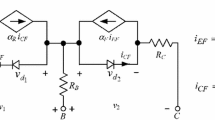

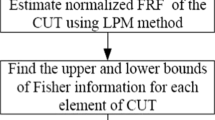

The subject of this paper is the fault diagnosis of analog circuits based on the use of nullor concept. The fault location technique presented in the paper can be implemented in the general-purpose analysis program which provides many advantages, of which the most important is the automation of the diagnosis process. A simulation based diagnosis model can be obtained by introducing the norators across the potentially faulty elements and the fixators at the accessible nodes. A practical problem that arises when using this nullor diagnosis model is a lack of an efficient procedure for localization of multiple faults. In the proposed diagnosis technique, the online computational requirements are reduced by introducing a diagnosis model that contains accessible nodes only. The diagnosis model is obtained from the original circuit using relationships among the measured voltages and compensated currents of the faulty elements. The proposed faulty location technique is validated on a benchmark example.

Similar content being viewed by others

References

Fontana, G., Luchetta, A., Manetti, S., & Piccirilli, M. (2017). A fast algorithm for testability analysis of large linear time-invariant networks. IEEE Transactions on Circuits and Systems I, 64(6), 1564–1575.

Tadeusiewicz, M., & Hałgas, S. (2015). A new approach to multiple soft fault diagnosis of analog BJT and CMOS circuits. IEEE Transactions on Instrumentation and Measurement, 64(10), 2688–2695.

Dai, H., & Souders, T. M. (1990). Time-domain testing strategies and fault diagnosis for analog systems. IEEE Transactions on Instrumentation and Measurement, 39(1), 157–162.

Robotycki, A., & Zielonko, R. (2002). Fault diagnosis of analog piecewise linear circuits based on homotopy. IEEE Transactions on Instrumentation and Measurement, 51(4), 876–881.

Cannas, B., Fanni, A., & Montisci, A. (2010). Algebraic approach to ambiguity-group determination in nonlinear analog circuits. IEEE Transactions on Circuits and Systems I, 57(2), 438–447.

Starzyk, J., & Dai, H. (1992). A decomposition approach for testing large analog networks. Journal of Electronic Testing: Theory and Applications, 3(3), 181–195.

Fedi, G., Manetti, S., Piccirilli, M., & Starzyk, J. (1999). Determination of an optimum set of testable components in the fault diagnosis of analog linear circuits. IEEE Transactions on Circuit and Systems—I Fundamental Theory and Applications, 46(7), 779–787.

He, Y., & Sun, Y. (2001). Neural network-based L/sub 1/-norm optimisation approach for fault diagnosis of nonlinear circuits with tolerance. IEE Proceedings—Circuits, Devices and Systems, 148(4), 223–228.

Peng, W., & Shiyuan, Y. (2005). A new diagnosis approach for handling tolerance in analog and mixed-signal circuits by using fuzzy math. IEEE Transactions on Circuits and Systems I, 52(10), 2118–2127.

Farchy, S., Gadzheva, E., Raykovska, L., & Kouyoumdjiev, T. (1995). Nullator–norator approach to analogue circuit diagnosis using general-purpose analysis programmes. International Journal of Circuit Theory and Applications, 23(6), 571–585.

Nenov, G., Sotirov, S., & Nenova, M. (2003). Nullor network diagnosis by using multilayer perceptron. IEEE Conference EUROCON 2003. Computer as a Tool, 1, 67–70.

Straube, B., & Vermeiren, W. (2002). A nullator–norator-based analogue circuit DC-test generation approach. In 8th international mixed-signal testing workshop, Montreux, Switzerland, 18–21 June (pp. 133–136).

Gadjeva, E., & Gadzhev, N. (2009). A nullator–norator model-based approach to analog circuit diagnosis. Facta Universitatis, Series: Electronics and Energetics, 22(2), 253–260.

Gadjeva, E., & Gadzhev, N. (2012). A nullor approach to computer-aided analogue circuit diagnosis. Inverse Problems in Science and Engineering, 20(1), 127–136.

Filaretov, V., Kurganov, S., & Gorshkov, K. (2016). Generalized parameter extraction method for analog circuit fault diagnosis. In 2016 2nd international conference on industrial engineering, applications and manufacturing (ICIEAM) (pp. 1–6).

Biernacki, R. M., & Bandler, I. W. (1981). Multiple-fault location of analog circuits. IEEE Transaction on Circuits and System, 28(5), 361–367.

Huang, Z. F., Lin, C. S., & Liu, R. W. (1983). Topological conditions for single-branch-fault. IEEE Transaction on Circuits and System, 30(6), 376–381.

Starzyk, J., & Bandler, J. (1983). Multiport approach to multiple-fault location in analog circuits. IEEE Transaction on Circuits and System, 30(10), 762–765.

Minfang, P., Yigang, H., Yi, T., Hongli, H., & Xueyi, S. (2003). Line fault location in a distribution network based on K-fault diagnosis method. In Proceedings of 2003 IEEE international conference on robotics intelligent systems and signal processing 2003 (Vol. 1, pp. 571–575).

Huang, J.-L., & Cheng, K.-T. (2000). Test point selection for analog fault diagnosis of unpowered circuit boards. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 47(10), 977–987.

Kumar, P., & Senani, R. (2002). Bibliography on nullors and their applications in circuit analysis, synthesis and design. Analog Integrated Circuits and Signal Processing, 33(1), 65–76.

Carlin, H. (1964). Singular network elements. IEEE Transactions on Circuit Theory, 11(1), 67–72.

Sanches-Lopez, C., Fernandez, F., Tlelo-Cuautle, E., & Tan, S. (2011). Pathological element-based active device models and their application to symbolic analysis. IEEE Transactions on Circuits and Systems I, 58(6), 1382–1395.

Pierzchala, M., & Fakhfakh, M. (2014). Symbolic analysis of nullor-based circuits with the two-graph technique. Circuits, Systems and Signal Processing, 33(4), 1053–1066.

Saad, R., & Soliman, A. (2008). Use of mirror elements in the active device synthesis by admittance matrix expansion. IEEE Transactions on Circuits and Systems I, 55(9), 2726–2735.

Kumngern, M., Khateb, F., & Kulej, T. (2017). Fully-balanced four-terminal floating nullor for ultra-low voltage analogue filter design. IET Circuits, Devices and Systems, 11(2), 173–182.

Sánchez-López, C., Cante-Michcol, B., Morales-López, F., & Carrasco-Aguilar, M. (2013). Pathological equivalents of CMs and VMs with multiple outputs. Analog Integrated Circuits and Signal Processing, 75(1), 75–83.

Hashemian, R. (2014). Fixator–norator pairs versus direct analytical tools in performing analog circuit designs. IEEE Transactions on Circuits and Systems II: Express Briefs, 61(8), 569–573.

Djordjevic, S. (2017). Analog circuit sizing using local biasing. Analog Integrated Circuits and Signal Processing, 93(2), 299–308.

Jiang, B. L., Wey, C. L., & Fan, L. J. (1988). Fault prediction for analog circuits. Journal of Circuits Systems and Signal Processing, 7(1), 95–109.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Djordjevic, S.D. Analog circuit diagnosis based on the nullor concept and multiport description of the circuit. Analog Integr Circ Sig Process 95, 141–149 (2018). https://doi.org/10.1007/s10470-018-1123-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-018-1123-7