Abstract

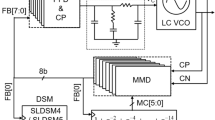

A wide band fractional-N digital PLL which uses a high resolution 2-dimension gated-Vernier time-to-digital converter (TDC) with 5.2 ps resolution is presented. The quantization noise shaping of the TDC greatly improves the in-band phase noise. While, in the same time, the 2-dimension structure makes the digital PLL (DPLL) be able to process large phase errors almost without the influence of latency time. Combined with a high figure-of-merit (FOM) class-D digitally controlled oscillator (DCO) and digital ΣΔ quantization noise cancellation based least mean square (LMS) algorithm, the DPLL achieves -110dBc/Hz and -140dBc/Hz for in-band and 10 MHz-offset phase noise, respectively, with carrier frequency of 3.5 GHz and 1 MHz bandwidth. The digital PLL is simulated in a 65 nm CMOS process, consuming 11.2 mW from a 1.0 V supply.

Similar content being viewed by others

Notes

In ring Vernier TDCs, the taps differ by integer times of ring stage number..

References

Staszewski, R. B., Chih-Ming Hung, K., Maggio, J., Wallberg, D., Leipold & P. T. Balsara, (2004) All-digital phase-domain TX frequency synthesizer for Bluetooth radios in 0.13 μm CMOS. Solid-State Circuits Conference, 2004. Digest of Technical Papers. ISSCC. 2004 IEEE International, 2004, pp. 272–527 Vol. 1.

Dudek, P., Szczepanski, S., & Hatfield, J. V. (2000). A high-resolution CMOS time-to-digital converter utilizing a Vernier delay line. IEEE Journal of Solid-State Circuits, 35(2), 240–247.

Yu, J., Dai, F. F., & Jaeger, R. C. (2010). A 12-Bit Vernier Ring Time-to-Digital Converter in 0.13 um CMOS technology. IEEE Journal of Solid-State Circuits, 45(4), 830–842.

Straayer, M. Z., & Perrott, M. H. (2009). A multi-path gated ring oscillator TDC with first-order noise shaping. IEEE Journal of Solid-State Circuits, 44(4), 1089–1098.

Lu, P., Liscidini, A., & Andreani, P. (2012). A 3.6 mW, 90 nm CMOS Gated-Vernier Time-to-Digital Converter With an equivalent resolution of 3.2 ps. IEEE Journal of Solid-State Circuits, 47(7), 1626–1635.

Lu, P., Andreani, P., & Liscidini, A. (2013) A 2-D GRO vernier time-to-digital converter with large input range and small latency. Radio Frequency Integrated Circuits Symposium (RFIC), 2013 IEEE, Seattle, WA, 2013, pp. 151-154.

Pamarti, S., Jansson, L., & Galton, I. (2004). A wideband 2.4-GHz delta-sigma fractional-NPLL with 1-Mb/s in-loop modulation. IEEE Journal of Solid-State Circuits, 39(1), 49–62.

Gupta, M., & Song, B. S. (2006). A 1.8-GHz Spur-Cancelled Fractional-N Frequency Synthesizer With LMS-Based DAC Gain Calibration. IEEE Journal of Solid-State Circuits, 41(12), 2842–2851.

Meninger, S. E., & Perrott, M. H. (2006). A 1-MHZ bandwidth 3.6-GHz 0.18-μm CMOS fractional-N synthesizer utilizing a hybrid PFD/DAC structure for reduced broadband phase noise. IEEE Journal of Solid-State Circuits, 41(4), 966–980.

Tasca, D., Zanuso, M., Marzin, G., Levantino, S., Samori, C., & Lacaita, A. L. (2011). A 2.9–4.0-GHz fractional-N digital PLL With bang–bang phase detector and 560-fsrms integrated Jitter at 4.5-mW power. IEEE Journal of Solid-State Circuits, 46(12), 2745–2758.

Hsu, C. M., Straayer, M. Z., & Perrott, M. H. (2008). A low-noise wide-BW 3.6-GHz digital um fractional-N frequency synthesizer with a noise-shaping time-to-digital converter and quantization noise cancellation. IEEE Journal of Solid-State Circuits, 43(12), 2776–2786.

Samori, C., Zanuso, M. S., Levantino & Lacaita A. L. (2011). Multipath adaptive cancellation of divider non-linearity in fractional-N PLLs. Circuits and Systems (ISCAS), 2011 IEEE International Symposium on, Rio de Janeiro, 2011, pp. 418–421.

Fanori, L., & Andreani, P. (2013). A 2.5-to-3.3 GHz CMOS Class-D VCO. Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013 IEEE International, San Francisco, CA, 2013, pp. 346–347.

Fanori, L., Mattsson, T., & Andreani, P. (2014). A Class-D CMOS DCO with an on-chip LDO. European Solid State Circuits Conference (ESSCIRC), ESSCIRC 2014 - 40th, Venice Lido, 2014, pp. 335–338.

Hegazi, E., Sjoland, H., & Abidi, A. A. (2001). A filtering technique to lower LC oscillator phase noise. IEEE Journal of Solid-State Circuits, 36(12), 1921–1930.

Chen, Y., et al. (2007). A 9 GHz dual-mode digitally controlled oscillator for GSM/UMTS transceivers in 65 nm CMOS. Solid-State Circuits Conference, 2007. ASSCC ‘07. IEEE Asian, Jeju, 2007, pp. 432–435.

Pavlovic, N., & Bergervoet, J. (2011). A 5.3 GHz digital-to-time-converter-based fractional-N all-digital PLL. Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2011 IEEE International, San Francisco, CA, 2011, pp. 54–56.

Weltin-Wu, C., Zhao, G., & Galton, I. (2015). A 3.5 GHz Digital Fractional-N PLL Frequency Synthesizer Based on Ring Oscillator Frequency-to-Digital Conversion. IEEE Journal of Solid-State Circuits, 50(12), 2988–3002.

Banerjee, D. (1998). PLL Performance, Simulation, and Design. Santa Clara, CA: Nat. Semicond., 1998. [Online]. http://www.national.com.

Acknowledgments

The authors are deeply grateful to ST Microelectronics for the generous silicon donation. This work was supported by the Swedish Foundation for Strategic Research (SSF) under the DARE project.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Mahmoud, A., Andreani, P. & Lu, P. A wide band fractional-N digital PLL with a noise shaping 2-D time to digital converter for LTE-A applications. Analog Integr Circ Sig Process 89, 337–345 (2016). https://doi.org/10.1007/s10470-016-0786-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0786-1