Abstract

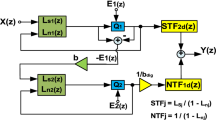

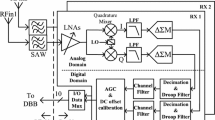

This paper proposes a new low-power MOS parametric integrator (MPI) for the design of wideband discrete time sigma-delta (ΣΔ) modulators. The MPI is implemented with MOS capacitors, which provide the required gain by switching from inversion in the sampling phase into depletion in the amplification phase. Analysis along with simulation results illustrate that MPI consumes very low power dissipation compared to the conventional active integrators with some negligible performance changes. To verify this, the MPI is used in two wideband ΣΔ modulators, one with 8-bit resolution and the other with 13-bit resolution with input bandwidth and sampling frequency of 12.5 and 200 MHz, respectively. The first one is a second order single stage ΣΔ modulator and the second one is a MASH 2-2 modulator, both implemented in 0.18-μm CMOS technology. Simulation results indicate that these modulators save a significant amount of power consumption when their second integrator is replaced by MPI.

Similar content being viewed by others

References

Ortmanns, M., & Gerfers, F. (2006). Continuous-time sigma-delta A/D conversion: fundamentals, performance limits and robust implementations. Springer.

Breems, L. J., Rutten, R., & Wetzker, G. (2004). A cascaded continuous-time ΣΔ modulator with 67-dB dynamic range in 10-MHz bandwidth. IEEE Journal Solid State Circuits, 39, 2152–2160.

Lee, K. (2009). Mixed CT/DT cascaded sigma-delta modulator. Journal of Semiconductor Technology and Science, 9, 233–239.

Fiorenza, J. K., Sepke, T., Holloway, P., Sodini, C. G., & Lee, H.-S. (2006). Comparator-based switched-capacitor circuits for scaled CMOS technologies. IEEE Journal of Solid-State Circuits, 41(12), 2658–2668.

Yang, H., & Sarpeshkar, R. (2005). A time-based energy-efficient analog-to-digital converter. IEEE Journal of Solid-State Circuits, 40(8), 1590–1601.

Chen, F., Chen, F., Bakkaloglu, B., & Ramaswamy, S. (2008). Design and analysis of a CMOS passive ΣΔ ADC for low power RF transceivers. Analog Integrated Circuits and Signal Processing, 59(2), 129–141. Springer.

Sai, T., & Sugimoto, Y. (2009). Design of a 1-V operational passive sigma-delta modulator. IEEE ECCTD. doi:10.1109/ECCTD.2009.5275088.

Zanbaghi, R., & Fiez, T. S. (2009). A novel low power hybrid loop filter for continuous-time sigma-delta modulators. IEEE ISCAS. doi:10.1109/ISCAS.2009.5117735.

Hussain, A., Sai-Weng, S., Seng-Pan, U., & Martins, R. P. (2011). Hybrid loop filter sigma delta modulator with NTF zero compensation. In IEEE ISOCC (pp. 76–79).

Song, T., Cao, Zh, & Yan, Sh. (2008). A 2.7-mW 2-MHz continuous-time modulator with a hybrid active–passive loop filter. IEEE Journal of Solid-State Circuits, 43(2), 330–341.

Collin, R. (1992). Foundations for microwave engineering (2nd ed.). New York: McGraw-Hill.

Oliveira, J., Goes, J., Figueiredo, M., Santin, E., Fernandes, J., & Ferreira, J. (2010). An 8-bit 120-MS/s interleaved CMOS pipeline ADC based on MOS parametric amplification. IEEE Transactions on Circuits and Systems II, 57(2), 105–109.

Shylu, D. S., Moni, D. J., Prasad, D. D. R., Suganya, T., & Prakash, N. (2011). Noiseless MOS parametric amplification in pipeline ADC. In IEEE ICECT (pp. 292–296).

Figueiredo, P. M., & Vital, J. C. (2004). The MOS capacitor amplifier. IEEE Transactions on Circuits and Systems II, 51(3), 111–115.

Shrimali, H., & Chatterjee, Sh. (2011). Distortion analysis of a three-terminal MOS-based discrete-time parametric amplifier. IEEE Transactions on Circuits and Systems II, 58(12), 902–905.

Meyer, R., & Stephens, M. (1975). Distortion in variable-capacitance diodes. IEEE Journal of Solid-State Circuits, 10(1), 47–54.

Abdelfattah, K., & Razavi, B. (2006). Modeling opamp nonlinearity in switched-capacitor sigma-delta modulators. In IEEE CICC (pp. 197–200).

Schreier, R., Silva, J., Steensgaard, J., & Temes, G. C. (2005). Design-oriented estimation of thermal noise in switched-capacitor circuits. IEEE Transactions on Circuits and Systems I, 52(11), 2358–2368.

Ranganathan, S., & Tsividis, Y. (2003). Discrete-time parametric amplification based on a three-terminal MOS varactor: Analysis and experimental results. IEEE Journal of Solid-State Circuits, 38(12), 2087–2093.

Murmann, B. (2012). Thermal noise in track-and-hold circuits analysis and simulation techniques. IEEE Solid-State Circuits Magazine, 4(2), 46–54.

Yukawa, A. (1985). A CMOS 8-bit high-speed A/D converter IC. IEEE Journal of Solid-State Circuits, 20(3), 775–779.

Dezzani, A., & Andre, E. (2003). A 1.2-V dual-mode WCDMA/GPRS sigma-delta modulator. International Solid-State Circuits Conference Digest of Technical Papers, 1(3), 58–59.

Nam, K., Lee, S.-M., Su, D. K., & Wooley, B. (2005). A low-voltage low power sigma-delta modulator for broadband analog-to-digital conversion. IEEE Journal of Solid-State Circuits, 40(9), 1855–1864.

Schreier, R., & Temes, G. C. (2005). Understanding delta-sigma data converters. New York: IEEE Press/Wiley.

Bult, K., & Geelen, G. (1990). A fast-settling CMOS opamp for SC circuits with 90-dB dc gain. IEEE Journal of Solid-State Circuits, 25(12), 1379–1384.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Seyedhosseinzadeh, B.H., Nabavi, A. A low-power parametric integrator for wideband switched-capacitor ΣΔ modulators. Analog Integr Circ Sig Process 78, 453–464 (2014). https://doi.org/10.1007/s10470-013-0232-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-013-0232-6