Abstract

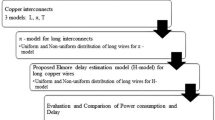

A general platform to generate the RC, RLC and RLCG models of interconnects using global approximation method, two-port networks, and asymptotic waveform evaluation (AWE) is presented. Using the delay of transmission-line-modeled interconnects from HSPICE as a bench mark, we show that among all 18 models studied, the π-configuration of AWE-RLC model yields the best accuracy. To reduce complexity subsequently computational cost without sacrificing accuracy, the AWE-RLC model is mapped to a complex RC model using moment matching. The complex RC model is further mapped to an improved RC model utilizing the principle of charge reservation. The improved RC model is employed to estimate the delay of long interconnects with buffer insertion. As compared with the conventional RC model, the improved RC model reduces the delay of interconnects with buffer insertion, the number of buffers, and the size of the buffer by 20.5, 24, and 32 %, respectively.

Similar content being viewed by others

References

Wei, S. (1997). Simple RLCG model for category-5 cables. IEE Electronics Letters, 33(25), 2108–2109.

Canuto, C. (1988). Spectral methods in fluid dynamics. New York: Springer-Verlag.

Harington, R. (1962). Field computation by moment method. New York: Macmillan.

Huelsman, L. (1991). Basic circuit theory (3rd ed.). New York: Prentice-Hall.

Pillage, L., & Rohrer, R. (1990). Asymptotic waveform evaluation for timing analysis. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 9(4), 352–366.

Kar, R., Maheshwari, V., Pathak, S., Reddy, M., Mal, A., & Bhattacharjee, A. (2010). An explicit approach for delay evaluation for on-chip RC interconnects using Beta distribution function by moment matching technique. In: Proceedings of the international conference on recent trends in information, telecommunication and computing (pp. 5–8).

Ma, J., & Rutenbar, R. (2006). Fast interval-valued statistical modeling of interconnect and effective capacitance. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 25(4), 710–724.

Hu, J., & Sapatnekar, S. (2000). Algorithms for non-Hanan-based optimization for VLSI interconnect under a higher-order AWE model. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 19(4), 446–458.

Sun, J., Ye, T., & Qiu, S. (2005). Interconnect delay and slew computation with the first three moments. In: Proceedings of the international conference on ASIC (Vol. 2, pp. 987–990).

Qinwei, X., Mazumder, P., & Ding, L. (2002). Novel macromodeling for on-chip RC/RLC interconnects. In: Proceedings of the IEEE international symposium on circuits and systems (pp. 189–192).

Rong, P., Lingling, S., & Xiaoyong, Z. (2005). New improved macromodelings for on-chip RLC interconnects. In: Proceedings of the IEEE international symposium on microwave, antenna, propagation and EMC technologies for wireless communications (pp. 919–922).

Weste, N., & Harris, D. (2005). CMOS VLSI design: A circuit and systems perspective (3rd ed.). New York: Addison-Wesley.

Xu, Q., Mazumder, P., & Ding, L. (2002). Novel macromodeling for on-chip RC/RLC interconnects. In: Proceedings of the IEEE international symposium on circuits and systems (Vol. 4, pp. 189–192).

Zhao, X., Sun, L., & Zhou, L. (2006). Improved macromodelings for coupled on-chip RLC interconnects. In: Proceedings of the IET international conference on wireless, mobile, and multimedia networks (pp. 1–4).

Rong, P., Sun, L., & Zhao, X. (2005). New improved macromodelings for on-chip RLC interconnects. In: Proceedings of the IEEE international symposium on microwave, antenna, propagation and EMC technologies for wireless communications (Vol. 2, pp. 919–921).

Bakoglu, H. (1990). Circuits, interconnections, and packaging for VLSI. New York: Addison-Wesley.

Ginneken, L. (1990). Buffer placement in distributed RC-tree networks for minimal elmore delay. In: Proceedings of the IEEE international symposium on circuits and systems (pp. 865–868).

Kang, K., Nan, L., Rustagi, S., Mouthaan, K., Shi, J., Kumar, R., et al. (2008). A wideband scalable and Spice-compatible model for on-chip interconnects up to 110 GHz. IEEE Transactions on Microwave Theory and Techniques, 56(4), 942–951.

Acknowledgements

This project was financially supported by the Natural Science and Engineering Research Council (NSERC) of Canada. Computer-aided design tools for analysis and design of integrated circuits were provided by CMC Microsystems, Kingston, ON, Canada.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Al-Taee, A.R., Yuan, F. & Ye, A. An improved RC model for VLSI interconnects with applications to buffer insertion. Analog Integr Circ Sig Process 79, 105–113 (2014). https://doi.org/10.1007/s10470-013-0135-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-013-0135-6