Abstract

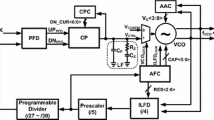

This paper presents a low phase noise integer-N phase-locked loop (PLL) for V-band signal generation. To enhance the frequency stability, we use a new class of Vackar voltage-controlled oscillator (VCO) in the PLL. The Vackar VCO achieves a low phase noise performance by effectively suppressing the AM-PM conversion. To properly align the locking range with the output of the VCO, a divider with wide locking range is realized by the current-mode logic (CML) D-flip-flops with tunable load. For spur reduction, an enhanced charge-pump structure is used to reject transient current glitches. With good static and dynamic current matching achieved in the charge pump, the reference spur is suppressed down to −50 dBc. The designed PLL is implemented in a 65 nm RFCMOS process, and the measurement demonstrates a low phase noise signal up to 17 GHz. The in-band phase noise (at 1 MHz offset) and out-band phase noise (at 50 MHz offset) are −103.6 and −126.8 dBc/Hz, respectively. The PLL consumes 50.7 mW and occupies a chip area of 0.9 mm2.

Similar content being viewed by others

References

Kim, J., Kim, J. K., Lee, B. J., Kim, N., Jeong, D. K., & Kim, W. (2006). A 20-GHz phase-locked loop for 40-Gb/s serializing transmitter in 0.13-μm CMOS. IEEE Journal of Solid-State Circuits, 41(4), 899–908.

Lee, J., Mingchung, L., & Huaide, W. (2008). A 75-GHz phase-locked loop in 90-nm CMOS technology. IEEE Journal of Solid-State Circuits, 43(6), 1414–1426.

Cao, C., Ding, Y., & O, K. K. (2007). A 50-GHz phase-locked loop in 0.13 μm CMOS. IEEE Journal of Solid-State Circuits, 42, 1649–1656.

Voinigescu, S. P., Aroca, R., Dickson, T. O., Nicolson, S. T., Chalvatzis, T., Chevalier, P., Garcia, P., Garnier, C. & Sautreuil, B. (2007). Towards a sub-2.5 V, 100-Gb/s serial transceiver. In: IEEE Custom Integrated Circuits Conference (pp 471–478).

Plouchart, J. O., Kim, J., Recoules, H., Zamdmer, N., Yue Tan, Sherony, M., Ray, A., & Wagner L. (2003, June). A power-efficient 33 GHz 2:1 static frequency divider in 0.12-μm SOI CMOS. In: Proc. IEEE Radio Frequency Integrated Circuits Symposium, (pp. 329–332).

Knapp, H., Wohlmuth, H.-D., Wurzer, M., & Rest M. (2002, Feb). 25 GHz static frequency divider and 25 Gb/s multiplexer in 0.12 μm CMOS. In: IEEE ISSCC Dig. Tech. Papers (pp. 302–468).

Lee, J., & Razavi, B. (2003, June). A 40-GHz frequency divider in 0.18-μm CMOS technology. In: Symposium on VLSI Circuits Digest of Technical Papers (pp. 259–262).

Nguyen, T.-N., & Lee, J.-W. (2010). Low phase noise differential Vackar VCO in 0.18 μm CMOS process technology. IEEE Microwave Wireless Components Letter, 20(2), 88–90.

Rhee, W. (1999, July). Design of high-performance CMOS charge pumps in phase-locked loops. In: IEEE International Symposium on Circuits and Systems (pp. 545–548).

Lau, C. Y., & Perrott, M. H. (2003, June). Fractional-N frequency synthesizer design at the transfer function level using a direct closed loop realization algorithm. In: Design Automation Conference (pp. 526–531).

Perrott, M. H. http://www-mtl.mit.edu/researchgroups/perrottgroup/HSCS/cppsim3.html. Accessed 3 July 2012.

Vackar, J. (1949, December). LC oscillators and their frequency stability. Tesla Technical Reports (pp. 1–9).

Nguyen, T.-N., & Lee, J.-W. (2012). A K-band CMOS differential Vackar VCO with the gate inductive feedback. IEEE Transactions on Circuit and Systems-II, 59(5), 257–261.

Plouchart, J.O., Kim, J., Karam, V., Trzcinski, R., & Gross, J. (2006, Feb). Performance variations of a 66 GHz static CML divider in 90 nm CMOS. IEEE ISSCC Dig. Tech. Papers (pp. 2142–2151).

Mijuskovic, D., Bayer, M., Chomicz, T., Garg, N., James, F., McEntarfer, P., et al. (1994). Cell-based fully integrated CMOS frequency synthesizers. IEEE Journal of Solid-State Circuits, 29(3), 271–279.

Gardner, F. M. (1980). Charge-pump phase-lock loops. IEEE Transactions on Communications, 28(11), 1849–1858.

Lee, J.-S., Keel, M.-S., Lim, S.-I., & Kim, S. (2000). Charge pump with perfect current matching characteristics in phase-locked loops. Electronics Letters, 23(36), 1907–1908.

Rhee, W., Song, B. S., & Ali, A. (2000). A 1.1-GHz CMOS fractional-N frequency synthesizer with a 3-b third-order ΔΣ modulator. IEEE Journal of Solid-State Circuits, 35(10), 1453–1460.

Ding, Y., & O, K. K. (2007). A 21-GHz 8-modulus prescaler and a 20-GHz phase-locked loop fabricated in 130-nm CMOS. IEEE Journal of Solid-State Circuits, 42(6), 1300–1309.

Ding Y., & O, K. K. (2007, June). A 21-GHz fractional-N synthesizer in 130-nm CMOS. Symposium on VLSI Circuits Digest of Technical Papers (pp. 264–265).

Ng, A. W. L., Leung, G. C. T., Kwok, K.-C., Leung, L. L. K., & Luong, H. C. (2006). A 1-V 24-GHz 17.5-mW phase-locked loop in a 0.18 μm CMOS process. IEEE Journal of Solid-State Circuits, 41(6), 1236–1244.

Saavedra, C. E. (2011). Frequency multiplier design techniques and applications in nanometer CMOS and GaAs: RF, high-speed and high-precision circuits (pp. 163–184). New York: McGraw-Hill.

Acknowledgments

This study was supported in part by the Basic Research Program through the National Research Foundation of Korea (No. 2012-001327) and in part by the ETRI SW-SoC R&BD Center, Human Resource Development Project.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Bui, L.T., Chau, TT. & Lee, JW. A low phase noise PLL using Vackar VCO and a wide-locking range tunable divider for V-band signal generation in 65-nm CMOS. Analog Integr Circ Sig Process 76, 91–102 (2013). https://doi.org/10.1007/s10470-013-0075-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-013-0075-1