Abstract

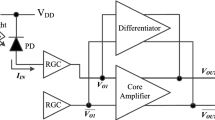

A high-scale integrated optical receiver including a preamplifier, a limiting amplifier, a clock and data recovery (CDR) block, and a 1:4 demultiplexer (DEMUX) has been realized in a 0.25 μm CMOS technology. Using the loop parameter optimization method and the low-jitter circuit design technique, the rms and peak-to-peak jitter of the recovered 625-MHz clock are 9.4 and 46.3 ps, respectively, which meet the jitter specifications stipulated in ITU-T recommendation G.958. The recovered and frequency divided 625 MHz clock has a phase noise of −83.8 dBc/Hz at 20 kHz offset in response to 2.5 Gb/s PRBS input data (223–1), and the 2.5 Gb/s PRBS data has been demultiplexed into four 625 Mb/s data. The power dissipation is only 0.3 W under a single 3.3 V supply (excluding output buffers).

Similar content being viewed by others

References

Razavi, B. (2002). Challenges in the design high-speed clock and data recovery circuits. IEEE Communications Magazine, 40(8), 94–101.

Razavi, B. (1996). Monolithic phase-locked loops and clock recovery circuits: theory and design. New York: IEEE Press.

Sato, F., et al. (1996). A 2.4 Gb/s receiver and a 1:16 demultiplexer in one chip using a super self-aligned selectively grown SiGe base (SSSB) bipolar transistor. IEEE Journal of Solid-State Circuits, 31(10), 1451–1457.

Pallotta, A., Centureli, F., & Triletti, A. (2000). A low-power clock and data recovery circuit for 2.5 Gb/s SDH receivers. In Proceedings of the 2000 International Symposium on Low Power Electronics and Design, Rapallo, Italy (pp. 67–72).

Kishine, K. et al. (1999). A low-jitter, low-power 2.5-Gb/s one-chip optical receiver IC with 1:8 DEMUX. In Proceedings of bipolar/BiCMOS circuits and technology meeting (BCTM) (pp. 177–180).

Hauenschild, J., et al. (1996). A plastic packaged 10-Gb/s BiCMOS clock and data recovery 1:4-Demultiplexer with external VCO. IEEE Journal of Solid State Circuits, 31, 2056–2059.

Chen, Y., et al. (2005). Monolithic IC of SDH STM-16 optical receiver core circuits. International Conference on Communications Circuits and Systems, 2, 27–30.

Rogers, J. E., & Long, J. R. (2002). A 10 Gb/s CDR/DEMUX with LC delay line VCO in 0.18-μm CMOS. IEEE Journal of Solid-State Circuits, 37(12), 1781–1789.

Kishine, K., Ishii, K., & Ichino, H. (2002). Loop-parameter optimization of a PLL for a low-jitter 2.5-Gb/s one-chip optical receiver IC with 1:8 DEMUX. IEEE Journal of Solid State Circuits, 37(1), 38–50.

Makie-Fukuda, K., Kikuchi, T., & Hotta, M. (1993). Measurement of digital noise in mixed-signal integrated circuits. In VLSI Circuits Symposium Digest of Technical Papers (pp. 23–24).

Acknowledgements

Project supported by the National Natural Science Foundation of China (No.60976029).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chen, Y., Wang, Z., Zhang, L. et al. 2.5-Gb/s low-jitter low-power monolithically integrated optical receiver. Analog Integr Circ Sig Process 71, 445–451 (2012). https://doi.org/10.1007/s10470-011-9698-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-011-9698-2