Abstract

To obtain a high performance CMOS resistor string digital-to-analog converter (DAC), one of the key design issues is the mismatch in the resistor ratio. This mismatch causes nonlinearity errors such as integral nonlinearity (INL) and differential nonlinearity (DNL), degrading the performances of the converter. Usually these matching properties are taken into account during the design phase by using time consuming and computational intensive transistor-level Monte Carlo simulations for the process technology corner. Recent research aims at reducing the design time by exploiting high-level modeling of converters as a trade-off between simulation time and modelling accuracy. In this work an analytical model for resistor mismatch in DACs is presented and implemented in MATLABTM environment. The model utilizes geometrical size of resistors and statistical data of the technology process. Starting from random process variations on geometries it was possible to estimate DNL and INL with very short time simulations. The proposed model is valid both for single stage resistor string DACs or segmented ones. The model can be used to speed up the design of resistor-string based DACs, or as a starting point to develop more accurate models by taking into account high-order effects. The model was successfully used to design a 10bit resistor string DAC in a 0.18 μm BCD technology with DNL and INL lower than 1 LSB (in absolute value). Since the complexity of the DAC is dominated by the resistor string, its optimization since the early design steps, enabled by the proposed high-level model, allowed to minimize area versus state of the art.

Similar content being viewed by others

References

Chen, C. C., Lu, N. K., Lin, W. R., Hsu, C. H., Huang, Z. Y., & Zeng, Y. Z. (2006). A 10-bit folded multi-LSB decided resistor string digital to analog converter. In Proceedings of IEEE international symposium on Intelligent signal processing and communications, ISPACS ’06, Tottori, Japan, pp. 123–126, 12–15 December 2006.

Liu, D. J., Lin, C. H., Yi, S. C., & Chen, J. J. (2007). A resistor string DAC for video processing. In national conference on Intelligent information hiding and multimedia signal processing (IIH-MSP 2007), Kaohsiung, Taiwan, pp. 503–506, 26–28 November 2007.

Baronti, F., Petri, E., Saponara, S. Fanucci, L., Roncella, R., Saletti, R., D’Abramo, P., & Serventi, R. (2009). Design and verification of hardware building blocks for high-speed and fault-tolerant in-vehicle networks. doi:10.1109/TIE.2009.2029583.

Saponara, S., Fanucci, L., & Terreni, P. (2007). Architectural-level power optimization of microcontroller cores in embedded systems. IEEE Transactions on Industrial Electronics, 54(1), 680-683.

Saponara, P. Nuzzo, P. D’Abramo, S., & Fanucci, L. (2010). Design methodologies and innovative architectures for mixed-signal embedded systems. Eurasip Journal on Embedded Systems, Art. no. 641261.

Shi, C., & Mostafa, I. M. (2001). Data converters for wireless standards (pp. 91–100). Springer, Berlin: Springer.

Van den Bosch, A., Steyaert, M., & Sansen, W. (2000). An accurate statistical yield model for CMOS current-steering D/A converters. In Proceedings of IEEE international symposium on Circuits and systems, Vol. 4, pp. 105–108, Geneva, Switzerland, May 2000.

Kosakowski, M., Wittmann, R., & Schardein, W. (2008). Statistical averaging based linearity optimization for resistor string DAC architectures in nanoscale processes. In Proceedings of 21st annual IEEE international SoC conference, Newport Beach, CA, pp. 261–266, September 2008.

Saponara, S., Fanucci, L., Nuzzo, P., Nani, C., & Van der Plas, G. (2009). Architectural exploration and design of time-interleaved SAR arrays for low-power and high speed A/D converters. IEICE Transactions on Electronics, E-92C(6), 843–851.

Nuzzo, F., De Bernardinis, P., & Sangiovanni-Vincentelli, A. (2006). Platform-based mixed-signal design: Optimizing a high-performance pipelined ADC. Analog Integrated Circuits and Signal Processing 3, 343–358.

Razavi, B. (2004). Principles of data conversion system design. New York: Wiley-IEEE Press.

Kuboki, S., Kato, K., Miyakawa, N., & Matsubara, K. (1982). Nonlinearity analysis of resistor string A/D Converters. IEEE Transactions on Circuits and Systems, 29, 383–390.

Riccardi, D., Causio, A., Filippi, I., Pregnolato, L.V.A., Galbiati, P., & Contiero, C. (2007). BCD8 from 7 V to 70 V: A new 0.18 μm technology platform to address the evolution of applications towards smart power ICs with high logic contents. In IEEE ISPSD ’07, Jeju, Korea, pp. 73–76.

Kester, W. (2005). Data conversion handbook. Analog devices series. Burlington, MA: Newnes and Elsevier.

Boylston, K., Brown, J. L. E., & Geiger, R. (2002). Enhancing performance in interpolating resistor string DACs. In The 2002 45th midwest symposium on Circuits and systems, 2002. MWSCAS-2002, Vol. 2, pp. II-541–II-544, August 2002.

Rivoir, R., Maloberti, F., & Torelli, G. (1997). Digital to analog converter with dual resistor string. US Patent No. 5,703,588, December 1997.

Hofman, U., Oldsen, M., Janes, H. J., Heller, M., Weiss, M., Fakas, G., Ratzmann, L., Marchetti, E., D’Ascoli, F., Melani, M., Bacciarelli, L., Volpi, E., Battini, F., Mostardini, L., Sechi, F., De Marinis, M., & Wagner, B. (2008). Wafer-level vacuum packaged micro-scanning mirrors for compact laser projection displays. In Proceedings of SPIE, Vol. 6887, pp. 110–114, San Jose, CA, USA.

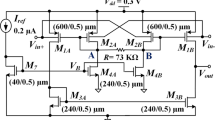

Volpi, E., Fanucci, L., & D’Ascoli, F. (2009). Design of a high voltage fully differential driver for a double axis scanning micromirror. Ph.D., Research in microelectronics and electronics, PRIME 2009, Cork, Ireland, pp. 112–115, July 2009.

Ge, F., Trivedi, M., Thomas, B., Jiang, W., & Song, H. (2008). 5 V 0.5 mW 2MSPS 10b DAC with rail-to-rail output in 0.13 μm CMOS technology. In IEEE SOCC, pp. 257–260.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Saponara, S., Baldetti, T., Fanucci, L. et al. High-level modeling of resistor string based digital-to-analog converters. Analog Integr Circ Sig Process 66, 407–416 (2011). https://doi.org/10.1007/s10470-010-9544-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-010-9544-y