Abstract

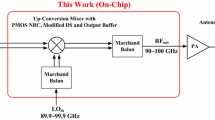

The design and implementation of an 8 GHz CMOS quadrature downconverter, achieving simultaneously low voltage supply operation and good linearity is presented in this paper. This is achieved by relaxing the inherent tradeoff between power conversion gain and linearity governing all active mixers and implementing a mixer using a new version of the bias-offset technique. The quadrature generator uses active inductors embodied in the LO buffer, and provides easy tuning by relaxing the coupling between amplitude and phase tuning of the outputs. It also provides reduced power consumption by eliminating the buffers located between the quadrature generator and the mixers. A prototype implemented in a 0.18 μm CMOS technology occupies an area of 0.44 × 0.3 mm2, operates from a 1V power supply and features an IIP3 of +3.5 dBm, an IIP2 of better than +48 dBm, an input compression point of −5.5 dBm, a power conversion gain of +6.5 dB for the mixers and a quadrature phase and amplitude matching of better than 1.5° and 1 dB respectively over a bandwidth of 100 MHz after tuning. The overall power consumption of the quadrature downconverter is 25.8 mW.

Similar content being viewed by others

References

M. Lefevre and P. Okrah, “Making the leap to 4G wireless.” EE Times Network, Communication System Design, July 2001.

Y. Mochida, T. Takano, H. Gambe, “Future directions and technology requirements of wireless communications.” IEEE International Electron Devices Meeting (IEDM), Technical Digest, pp. 1.3.1–1.3.8, 2001.

M. Steyaert, “Single Chip CMOS RF transceivers: Wishful thinking or reality.” IEE Seminar on Low Power Integrated Circuit Design, Proceedings, pp. 1/1–1/6, 2001.

B. Razavi, “Design considerations for direct-conversion receivers.” IEEE Transactions on Circuit and Systems - II: Analog and Digital Signal Processing, vol. 44, pp. 428–435, 1997.

S. Mattisson, “Architecture and technology for multi-standard transceivers.” Proceedings of the Bipolar/BiCMOS Circuits and Technology Meeting, pp. 82–85, 2001.

IEEE Std 802.11a, Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications: High-speed physical layer in the 5 GHz band, IEEE, 1999.

R.C. Sagers, “Intercept point and undesired responses.” IEEE Transactions on Vehicular Technology, vol. 32, pp. 121–133, 1983.

L.E. Larson, “The impact of emerging ‘4G’ systems on the performance and complexity requirements of RF ICs.” IEEE Radio Frequency Integrated Circuits Symposium, RFIC, pp. 15–18, 2003.

A.A. Abidi, “RF CMOS comes of age.” IEEE Symposium on VLSI Circuits, Digest of Technical Papers. pp. 113–116, 2003.

E. Terrovidis and R.G. Meyer, “Intermodulation distortion in current commutating CMOS mixers.” IEEE Journal of Solid-State Circuits, vol. 35, pp. 1461–1473, Oct. 2000.

Y. Kim, Y. Kim and S. Lee, “Linearized mixer using predistortion technique.” IEEE Microwave and Wireless Components Letters, vol. 12, pp. 204–205, 2002.

Q. Li, J. Zhang, W. Li, and J.S. Yuan, “CMOS RF mixer non-linearity design.” IEEE 43rdMidwest symposium on Circuits and Systems, Proceedings, pp. 808–811, 2001.

T.W. Kim, B. Kim, and K. Lee, “Highly linear RF CMOS amplifier and mixer adopting MOSFET transconductance linearization by multiple gated transistors.” IEEE Radio Frequency Integrated Circuits Symposium, Proceedings, pp. 107–110, 2003.

Z. Wang and W. Guggenbuhl, “A voltage-controllable linear MOS transconductor using bias offset technique.” IEEE Journal of Solid-State Circuits, vol. 25, pp. 315–317, 1990.

F. Mahmoudi and C.A.T. Salama, US Patent, Applied for, 2003.

F. Mahmoudi and C. AT. Salama, “8 GHz, 1V, high linearity, low power CMOS active mixer.” IEEE Radio Frequency Integrated Circuit Symposium, RFIC, pp. 401–404, 2004.

T. Tsukahara, M. Harada, M. Ugajin, J. Kodate, and A. Yamagishi, “Design methodology of low-power CMOS RF-ICs.” Proceedings of the Asia and South Pacific Design Automation Conference, ASP-DAC, pp. 394–399, 2003.

A.N. Karanicolas, “A 2.7V 900 MHz CMOS LNA and mixer.” IEEE Journal of Solid-State Circuits, vol. 31, pp. 1939–1944, 1996.

P. Antognetti and G. Massobrio, Semiconductor Device Modeling with SPICE, Mc Graw-Hill, 1992.

T. Manku, “Low voltage topology for radio frequency circuit design.” US-Patent #6,232,848, 2001.

F. Maloberti and M. Signorelli, “Quadrature waveform generator with enhanced performances.” IEEE Symposium on VLSI Circuits, Digest of Technical Papers, pp. 222–226, 1998.

M.J. Gingell, “Polyphase symmetrical network.” US-Patent 3,559,042, 1971.

I.A. Koullias, J.H. Havens, I.G. Post, and P.E. Bronner, “A 900 MHz transceiver chip set for dual-mode cellular radio mobile terminals.” IEEE International Solid-State Circuit Conference (ISSCC), Digest of Technical Papers, 278, pp. 140–141, 1993.

B. Razavi, “Challenge in the design of frequency synthesizers for wireless applications.” IEEE Custom Integrated Circuit Conference, Proceedings, pp. 395–402, 1997.

S. Hwang, G. Moon, and S. Song, “A GHz I-Q quadrature signal generator using cellular oscillator network.” IEEE Asia Pacific Conference on Application Specific Integrated Circuits (ASIC), pp. 91–94, 1999.

J. Cabanillas, L. Dussopt, J.M. Lopez-Villegas, and G.M. Rebeiz, “A 900 MHz low phase noise CMOS quadrature oscillator.” IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, pp. 63–66, 2002.

M. Steyaert and R. Roovers, “A 1-GHz single-chip quadrature modulator.” IEEE Journal of Solid-State Circuits, vol. 27, pp. 1194–1197, 1992.

F. Mahmoudi and C. AT. Salama, “8 GHz tunable CMOS quadrature generator using differential active inductors.” submitted and accepted for publication, International Symposium on Circuits and Systems, ISCAS, 2005.

R. Akbari-Dilmaghani, A. Payne, and C. Toumazou, “A high Q RF CMOS differential active inductor.” Proceedings of ICECS, pp. 157–160, 1998.

J. Schechtman, A.C.M. De Queiroz, and L.P. Caloba, “A high performance balanced MOS transconductor.” Proceedings IEEE 36th Midwest Symposium on Circuits and Systems, pp.1378–1381, 1993.

S.H. Wang, J. Gil, I. Kwon, and H.K. Ahn, “A 5-GHz band I/Q clock generator using a self-calibration technique.” European Solid-State Circuits Conference, pp. 807–810, 2002.

Author information

Authors and Affiliations

Corresponding author

Additional information

Farsheed Mahmoudi was born in Tehran, Iran. He received his B.Sc. and M.Sc. degrees in Electronics from the University of Tehran, Tehran, Iran in 1997 and 2000 respectively. He is currently working toward the Ph.D. degree at the University of Toronto, Toronto, Canada. His research interests include the design and analysis of RF circuits and systems for wireless applications.

C. Andre T. Salama received the B.A.Sc. (Hons.) M.A.Sc. and Ph. D. degrees, all in Electrical Engineering, from the University of British Columbia in 1961, 1962 and 1966 respectively.

From 1962 to 1963 he served as a Research Assistant at the University of California, Berkeley. From 1966 to 1967 he was employed at Bell Northern Research, Ottawa, as a Member of Scientific Staff working in the area of integrated circuit design. Since 1967 he has been on the staff of the Department of Electrical and Computer Engineering, University of Toronto where he held the J.M. Ham Chair in Microelectronics from 1987 to 1997. In 1992, he was appointed to his present position of University Professor for scholarly achievements and preeminence in the field of microelectronics. In 1989–90, he was awarded the ITAC/NSERC Research Fellowship in information technology. In 1994, he was awarded the Canada Council I.W. Killam Memorial Prize in Engineering for outstanding career contributions to the field of microelectronics. In 2000, he received the IEEE Millenium Medal. In 2003, he received the Outstanding Lifetime Achievement Award from the Canadian Semiconductor Technology Conference for seminal and outstanding contributions to semiconductor device research and promotion of Canadian University research in microelectronics. In 2004, he received the NSERC Lifetime Achievement Award of Research Excellence for outstanding and sustained contributions to the field of microelectronics and the Networks of Centres of Excellence (NCE) Recognition Award for research excellence and outstanding leadership.

He was associate editor of the IEEE Transactions on Circuits and Systems in 1986–88 and a member of the International Electron Devices Meeting (IEDM) Technical Program Committee in 1980–82, 1987–89 and 1996–98. He was the chair of the Solid State Devices Subcommittee for IEDM in 1998 and was a member of the editorial board of Solid State Electronics from 1984 to 2002. He is presently a member of the editorial board of the Analog IC and Signal Processing Journal and the Technical Program Committee of the International Symposium on Power Semiconductor Devices and ICs (ISPSD) and the Technical Program Committee of the International Symposium on Low Power Electronics and Design (ISLPED). He chaired the technical program committee of ISPSD in 1996 and was the general chair for the conference in 1999.

Dr. Salama is the Scientific Director of Micronet, a network of centres of excellence focussing on microelectronics research and funded by the Canadian Government and Industry.

He has published extensively in technical journals, is the holder of eleven patents and has served as a consultant to the semiconductor industry in Canada and the U.S. His research interests include the design and fabrication of semiconductor devices and integrated circuits with emphasis on deep submicron devices as well as circuits and systems for high speed, low power signal processing applications.

Dr. Salama is a Fellow of the Institute of Electrical and Electronics Engineers, a Fellow of the Royal Society of Canada, a Fellow of the Canadian Academy of Engineering, a member of the Association of Professional Engineers of Ontario, the Electrochemical Society and the Innovation Management Association of Canada.

Rights and permissions

About this article

Cite this article

Mahmoudi, F., Salama, C.A.T. 8 GHz 1V, CMOS quadrature downconverter for wireless applications. Analog Integr Circ Sig Process 48, 185–197 (2006). https://doi.org/10.1007/s10470-006-7630-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-006-7630-y