Abstract

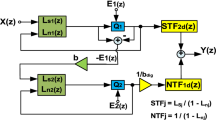

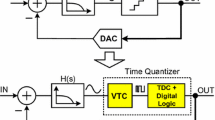

A domino free 4-path time-interleaved second order sigma-delta modulator is proposed. This time-interleaved scheme uses only one integrator channel along with incomplete integrator output terms to completely eliminate the quantizer domino which is a key limit for the practical circuit implementation of conventional multi-path time-interleaved sigma-delta modulators. In addition, the single integrator channel leads to considerable hardware reduction as well as path mismatch insensitivity, since only one global feedback path is required. As a result, the switched capacitor implementation of the 4-path time-interleaved second order sigma-delta modulator is enabled with the conventional 2-phase clocking scheme by using only 5 op-amps.

Similar content being viewed by others

References

J.C. Candy and G.C. Temes, Oversampling Delta-Sigma Data Converters: Theory, Design and Simulation: IEEE Press, New York, 1996.

P.M. Aziz, H.V. Sorenson, and J.V. Spiegel, “An overview of sigma-delta converters,” IEEE Signal Processing Mag., pp. 61–84, Jan. 1996.

R. del Rio et al., “Highly linear 2.5-V CMOS Σ Δ modulator for ADSL+,” IEEE Trans. Circuits Syst. I, vol. 51, no. 1, pp. 47–62, 2004.

M.R. Miller and C.S. Petrie, “A multi-bit sigma-delta ADC for multimode receivers,” IEEE J. Solid-State Circuits, vol. 38, no. 3, pp. 475–482, 2002.

R. Gaggl, M. Inversi, and A. Wiesbauer, “A power optimized 14-bit Σ Δ modulator for ADSL CO applications,” in ISSCC Dig. Tech. Papers, Feb. 2004, pp. 82–83.

K.H. Choa, S. Nadeem, W.L. Lee, and C.G. Sodini, “A higher order topology for interpolative modulators for oversampling A/D converters,” IEEE Trans. Circuits Syst., vol. 37, no. 3, pp. 309–318, 1990.

R. Schreier, “An empirical study of high order single-bit delta-sigma modulators,” IEEE Trans. Circuits Syst. II, vol. 40, no. 8, pp. 461–466, 1993.

F. Chen and B.H. Leung, “A high resolution multibit sigma-delta modulator with individual level averaging,” IEEE J. Solid-State Circuits, vol. 30, no. 4, pp. 453–459, 1995.

Y. Geerts, M. Steyaert, and W. Sansen, “A high-performance multibit Σ Δ CMOS ADC,” IEEE J. Solid-State Circuits, vol. 35, no. 12, pp. 1829–1840, 2000.

A.A. Hamoui and K.W. Martin, “High-order multibit modulators and pseudo data-weighted-averaging in low oversampling Σ Δ ADCs for broad-band applications,” IEEE Trans. Circuits Syst. I, vol. 51, no. 1, pp. 72–85, 2004.

A. Eshraghi and T.S. Fiez, “A comparative analysis of parallel delta-sigma ADC architectures,” IEEE Trans. Circuits Syst. I, vol. 51, no. 3, pp. 450–458, 2004.

P. Aziz, H. Sorenson, and V. Spiegel, “Multiband sigma-delta modulation,” Electron. Lett., vol. 29, pp. 760–762, 1993.

R. Cormier, T. Sculley, and R. Bamberger, “Combining sub-band decomposition and sigma-delta modulation for wide band A/D conversion,” in Proc. IEEE Int. Symp. Circuits and Systems, June 1994, vol. 5, pp. 357–360.

I. Galton and H. Jenson, “Delta-sigma modulation based A/D conversion without oversampling,” IEEE Trans. Circuits Syst. II, vol. 42, no. 12, pp. 773–784, 1995.

L. Sumanen, M. Waltari, and K. Halonen, “A 10-bit 200-MS/s CMOS parallel pipeline A/D converter,” IEEE J. Solid State Circuits, vol. 36, no. 7, pp. 1048–1055, 2001.

R.K. Poorfard and D.A. Johns, “Time-interleaved oversampling converters,” Electron. Lett., vol. 29, pp. 1673–1674, 1993.

R.K. Poorfard, L.B. Lim, and D.A. Johns, “Time-interleaved oversampling A/D converters: Theory and practice,” IEEE Trans. Circuits Syst. II, vol. 44, no. 8, pp. 634–645, 1997.

M. Kozak and I. Kale, “Novel topologies for time-interleaved delta-sigma modulators,” IEEE Trans. Circuits Syst. II, vol. 47, no. 7, pp. 639–654, 2000.

M. Kozak, M. Karaman, and I. Kale, “Efficient architectures for time-interleaved oversampling delta sigma data converters,” IEEE Trans. Circuits Syst. II, vol. 47, no. 8, pp. 802–810, 2000.

H.R. Srinivas and K.K. Parhi, “A fast VLSI adder architecture,” IEEE J. Solid State Circuits, vol. 27, no. 5, pp. 761–767, 1992.

Z. Wang, G.A. Jullien, W.C. Miller, J. Wang, and S.S. Bizzan, “Fast adders using enhanced multiple-output domino logic,” IEEE J. Solid State Circuits, vol. 32, no. 2, pp. 206–214, 1997.

J.C. Lo, “A fast binary adder with adder conditional carry generation,” IEEE Trans. Computers, vol. 32, no. 2, pp. 206–214, 1997.

P. Malcovati et al., “Behavioral modeling of switch-capacitor sigma-delta modulators,” IEEE Trans. Circuits Syst. I, vol. 50, no. 3, pp. 352–364, 2003.

B. Li and H. Tenhunen, “A structure of cascading multi-bit modulators without dynamic element matching or digital correction,” in Proc. IEEE Int. Symp. Circuits and Systems, May 2002, vol. 3, pp. 711–714.

M.J. McNutt, S. LeMarquis, and J.L. Dunkey, “Systematic capacitor matching errors and corrective layout procedures,” IEEE J. Solid State Circuits, vol. 29, no. 5, pp. 611–616, 1994.

L.A. Williams and B.A. Wooley, “A third order sigma-delta modulator with extended dynamic range,” IEEE J. Solid State Circuits, vol. 29, no. 3, pp. 193–202, 1994.

Author information

Authors and Affiliations

Corresponding author

Additional information

Kye-Shin Lee received the B.S. degree in electrical engineering from Korea University, Seoul, Korea, in 1992 and the M.S. degree in electrical engineering from Texas A&M University, College Station, in 2002. He is currently working toward the Ph.D. degree in electrical engineering at the University of Texas at Dallas.

He was with LG Semicon Co. (now Hynix Semicon Inc.), Seoul, Korea from 1994 to 1999, where he was involved in mixed signal circuit design and testing of BW/Color CCD chipsets including timing/sync. signal generator, camera signal processor, USB camera interface, and sigma-delta CODECs for audio and voice band applications. His research has been focused on switched-capacitor circuits, sigma-delta modulators, and pipeline ADCs.

Yunyoung Choi received the B.S. degree from Kwangwoon University, Seoul, Korea, in 1999 and the M.S. degree in electrical engineering from Texas A&M University, College Station, in 2002. He is currently working toward the Ph.D. degree in electrical engineering at the University of Texas at Dallas. He worked for Texas Instruments, Dallas, from May to December 2003 at the Wireless Business Unit. His research interest includes sigma-delta A/D and D/A converters for audio systems and RF applications.

Franco Maloberti received the Laurea Degree in physics (summa cum laude) from the University of Parma, Parma, Italy, in 1968 and the Dr. Honoris Causa degree in electronics from the Instituto Nacional de Astrofisica, Optica y Electronica (Inaoe), Puebla, Mexico, in 1996.

In 1993, he was a Visiting Professor at ETH-PEL, Zurich, Switzerland. He was Professor of Microelectronics and Head of the Micro Integrated Systems Group, University of Pavia, Pavia, Italy, and the TI/J.Kilby Analog Engineering Chair Professor at Texas A&M University, College Station. He is currently with the University of Pavia and an adjunct Professor at the University of Texas at Dallas. His professional expertise is in the design, analysis, and characterization of integrated circuits and analog digital applications, mainly in the area of switched-capacitor circuits, data converters, interfaces for telecommunication and sensor systems, and CAD for analog and mixed A/D design. He has written more than 250 published papers, three books, and holds 15 patents.

Dr. Maloberti was a 1992 recipient of the XII Pedriali Prize for his technical and scientific contributions to national industrial production. He was co-recipient of the 1996 Institution of Electrical Engineers (U.K.) Fleming Premium for the paper “CMOS triode transistor transconductance for high-frequency continuous time filters.” He has been responsible at both technical and management levels for many research programs including ten ESPRIT projects and has served the European Commission as ESPRIT Projects’ Evaluator and Reviewer and as a European Union expert in many Initiatives. He served the Academy of Finland on the assessment of electronic research in Academic institutions and on the research programs’ evaluator. He was Vice-President, Region 8, of the Editor of IEEE Circuits and Systems (CAS) Society from 1995 to 1997 and an Associate Editor of the IEEE Transcations on Circuits and Systems II. He received the 1999 IEEE CAS Society Meritorious Service Award, the 2000 CAS Society Golden Jubilee Medal, and the IEEE Millennium Medal. He is the President of IEEE Sensors Council and a member of the Board of Governors of the IEEE CAS Society. He is also the member of the Italian Electrotechnical and Electronic Society (AEI) and the Editorial Board of Analog Integrated Circuits and Signal Processing.

Rights and permissions

About this article

Cite this article

Lee, Ks., Choi, Y. & Maloberti, F. Domino Free 4-Path Time-Interleaved Second Order Sigma-Delta Modulator. Analog Integr Circ Sig Process 43, 225–235 (2005). https://doi.org/10.1007/s10470-005-1604-3

Received:

Revised:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/s10470-005-1604-3