Abstract

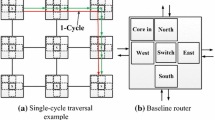

With booming intricacy in applications, optimizing latency is a key requirement in Network-on-Chip (NoC). Bypassing the routers in the intermediate path, the Single Cycle Multi-Hop Asynchronous Repeated Traversal (SMART) NoC is offered as a solution. However, SMART requires a bypass arrangement, contributing to additional wires and stages in the pipeline. In this paper, the Turn-to-west-first technique is used to establish express bypass channels where all the requests for bypass are jointly sent with the flits. The techniques including adaptive routing, combined wormhole switching, and virtual cut-through have been integrated into the router design. The mathematical modeling is done to calculate the wire overhead for the proposed design. Based on these considerations, a novel router architecture is designed to allow the flits to traverse both in one or two-dimensional paths without latching in any bypass router. The presented design has been compared with the baseline router and other popular bypass methods for the average packet latency and wire overhead. Both the synthetic traffic and specific traces of realistic traffic taken from the PARSEC benchmark suite have been considered for evaluation of the proposed design. In comparison to SMART NoC around 85% of the additional wires are reduced and over 40.51% reduction in latency is observed. The latency-optimized NoC is suitable to be used for high-speed applications.

Similar content being viewed by others

References

Patil T, Sandi A (2022) Design and implementation of asynchronous NOC architecture with buffer-less router. Mater. Today Proc. 49(3):756–763. https://doi.org/10.1016/j.matpr.2021.05.282

Kamal R, Juan M, Arostegui M (2018) A multi-synchronous bi-directional NoC (MBiNoC) architecture with dynamic self-reconfigurable channel for the GALS infrastructure. Alex Eng J 57:739–754. https://doi.org/10.1016/j.aej.2017.02.019

Jung DC, Davidson S, Zhao C, Richmond D, Taylor M and Ruche B (2020) Networks: wire-maximal, no-fuss NoCs: special session paper. In: Proceedings of the 2020 14th IEEE/ACM international symposium on networks-on-chip (NOCS), Hamburg, Germany, pp 1–8

Kamal R, Juan M, Arostegui M (2021) Network-on-chip topologies: potentials, technical challenges. Recent Adv Res Direct 57:739–754. https://doi.org/10.5772/intechopen.97262

Masahiro N, Maaki S, Yoshiko H, Hitoshi M, Mitsuhisa S (2021) Graph optimization algorithm for low-latency interconnection networks. Parallel Comput 106:102805. https://doi.org/10.1016/j.parco.2021.102805

Li Y, Wang K, Gu H, Yang Y, Su N, Chen Y, Zhang H (2018) A joint optimization method for NoC topology generation. J Supercomput 74(7):2916–2934

Zulkefli FWB, Ehkan P, Warip MNM (2019) A efficacy of different buffer size on latency of network on chip (NoC). Bull Electr Eng Inf 8:739–754. https://doi.org/10.11591/eei.v8i2.1422

Passas G, Katevenis M, Pnevmatikatos D (2012) Crossbar NoCs are scalable beyond 100 nodes. IEEE Trans Comput Aided Des Integr Circuits Syst 31:573–585

Chemli B, Zitouni A (2016) Design and evaluation of optimized router pipeline stages for network on chip. Int Image Process Appl Syst. https://doi.org/10.1109/IPAS.2016.7880067

Prasad BMP, Parane K, Talawar B (2021) FPGA friendly NoC simulation acceleration framework employing the hard blocks. Computing 103:1791–1813. https://doi.org/10.1007/s00607-020-00901-x

Guo P, Liu Q, Chen R, Yang L, Wang D (2019) A bypass-based low latency network-on-chip router. IEICE Electr Express. https://doi.org/10.1587/elex.16.20181147

Parane K, Prabhu BM, Talawar B (2020) LBNoC: design of low-latency router architecture with lookahead bypass for network-on-chip using FPGA. ACM Trans Des Autom Electr Syst TODAES 25:1–26. https://doi.org/10.1145/3365994

Bao DL, Xiaoming X, Yizong Y, Jiuru R, Xiangshi F et al (2017) A virtual channel allocation algorithm for NoC. ICST Trans Amb Syst 4:153307

Gangwar R, Sreedharan A, Prasad N, Agarwal K, Gade SH (2021) Topology agnostic virtual channel assignment and protocol level deadlock avoidance in a network-on-chip. In: 58th ACM/IEEE design automation conference (DAC) 58, pp 61–66. https://doi.org/10.1109/DAC18074.2021.9586196

Zhou Y, Pingqiang Z, Jieming S et al (2011) NoC frequency scaling with flexible-pipeline routers. In: Low power electronics and design (ISLPED) international symposium, pp 403-408. https://doi.org/10.1109/ISLPED.2011.5993674

Ejaz P, Ahsen S, Ioannis V (2018) FreewayNoC: a DDR NoC with pipeline bypassing. In: Twelfth IEEE/ACM international symposium on networks-on-chip (NOCS), pp 1–8. https://doi.org/10.1109/NOCS.2018.8512160

Chang Y-Y, Huang YS-C, Poremba M, Narayanan V, Xie Y, King C (2013) TS-router: on maximizing the quality-of-allocation in the on chip network. In: Proceedings of IEEE 19th International symposium on high performance computer architecture (HPCA), pp 390–399

Vinodhini M, Murty NS, Ramesh TK (2020) Transient error correction coding scheme for reliable low power data link layer in NoC. IEEE Access 8:174614–174628

Vinodhini M, Murty NS, Ramesh TK (2021) A crosstalk aware transient error correction coding technique for NoC links. Microelectr Reliab 124:114296. https://doi.org/10.1016/j.microrel.2021.114296

Mullins R, West A, Moore S (2004) Low-latency virtual-channel routers for on-chip networks. In: Proceedings of the 31st annual international symposium on computer architecture, Munich, Germany, pp 188–197. https://doi.org/10.1016/j.matpr.2021.05.282

George M, Jiang N, Daniel B, William D (2021) Packet chaining: efficient single-cycle allocation for on-chip networks. In Proceedings of the 44th annual IEEE/ACM international symposium on microarchitecture, pp 83–94. https://doi.org/10.1016/j.matpr.2021.05.282

Katta M, Ramesh T K (2021) Maximizing switch allocation matching to reduce latency in network-on-chip. In: IEEE PhD colloquium on ethically driven innovation & technology for society (PhD EDITS), pp 1–2

Katta M, Ramesh TK (2020) Virtual channel and switch traversal in parallel to improve the latency in Network on Chip. In: 2nd PhD colloquium on ethically driven innovation and technology for society (PhD EDITS), pp 1–2

Katta M, Ramesh TK (2021) Latency improvement by using fill VC allocation for network on chip. In: Data engineering and communication technology, pp 561–569

Katta M, Ramesh TK, Plosila J (2021) SB-router: a swapped buffer activated low latency network-on-chip router. IEEE Access. https://doi.org/10.1109/ACCESS.2021.3111294

Kumar A, Peh L, Kundu P, Jha NK (2008) Toward ideal on-chip communication using express virtual channels. IEEE Micro 28:80–90

Perez I, Vallejo E, Beivide R (2018) Efficient router bypass via hybrid flow control. In: Proceedings of the 2018 11th international workshop on network on chip architectures (NoCArc), Fukuoka, Japan, pp 1–6

Krishna T, Chen CO, Kwon WC, Peh L (2013) Breaking the on-chip latency barrier using SMART. In: Proceedings of the 2013 IEEE 19th international symposium on high performance computer architecture (HPCA), Shenzhen, China, pp 378–389

Krishna T, Chen CO, Kwon WC, Peh L (2014) Smart: single-cycle multihop traversals over a shared network on chip. IEEE Micro 34:43–56

Psarras A, Seitanidis I, Nicopoulos C, Dimitrakopoulos G (2016) ShortPath: a network-on-chip router with fine-grained pipeline bypassing. IEEE Trans Comput

Psarras A, Lee J, Mattheakis P, Nicopoulos C, Dimitrakopoulos G (2016) A low-power network-on-chip architecture for tile-based chip multi-processors. In: ACM great lakes symposium on VLSI (GLSVLSI)

Chen X, Jha NK (2016) Reducing wire and energy overheads of the SMART NoC using a setup request network. IEEE Trans Very Large Scale Integr VLSI Syst 24:3013–3026

Park S, Krishna T, Chen C, Daya B, Chandrakasan A, Peh L (2012) Approaching the theoretical limits of a mesh NoC with a 16-node chip prototype in 45 nm SOI. In: Proceedings of the DAC design automation conference, San Francisco, CA, USA, pp 398–405

Krishna T, Postman J, Edmonds C, Peh L, Chiang P (2010) SWIFT: a SWing-reduced interconnect for a token-based network-on-chip in 90nm CMOS. In: Proceedings of the 2010 IEEE international conference on computer design, Amsterdam, The Netherlands, pp 439–446

Ma W, Gao X, Gao Y et al (2021) A latency-optimized network-on-chip with rapid bypass channels. Micromachines 12:621. https://doi.org/10.3390/mi12060

Agarwal N, Krishna T, Peh L, Jha NK (2009) A detailed on-chip network model inside a full-system simulator. In: Proceedings of the 2009 IEEE international symposium on performance analysis of systems and software, Boston, MA, USA, pp 33-42

Gebhart M, Hestness J, Fatehi E, Gratz P, Keckler SW (2009) Running PARSEC 2.1 on M5. Department of Computer Science, University of Texas Austin, Austin, TX, USA, Technical Report TR-09-32

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

Conflict of interest

All authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Katta, M., Ramesh, T.K. & Plosila, J. A novel technique for flit traversal in network-on-chip router. Computing 105, 2647–2673 (2023). https://doi.org/10.1007/s00607-023-01200-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00607-023-01200-x