Abstract

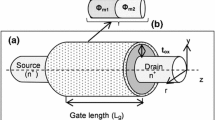

In this present work, we explore the hot carrier fidelity of gate electrode workfunction engineered silicon nanowire (GEWE-SiNW) MOSFET at 300 K using DEVEDIT-3D device editor and ATLAS device simulation software. TCAD simulation shows reduction in the hot carrier reliability of a GEWE SiNW MOSFET in terms of electron temperature, electron velocity and Hot Electron gate current for reflecting its efficacy in high power CMOS applications. Further, a comparative investigation for different values of oxide thickness and high-k has been done to analyze the performance of GEWE-SiNW MOSFET in terms of electrical parameters such as conduction band, DIBL, electric field, electron temperature, electric velocity and gate current. It has been clearly shown that with oxide thickness 0.5 nm the hot-carrier reliability and device performance improves in comparison to oxide thickness 2.5 nm. In addition, with k = 21(HfO2) device performance in terms of hot-carrier reliability further enhanced due to increased capacitance and thus offer its effectiveness in sub-nm range analog applications.

Similar content being viewed by others

References

Arora N (2012) MOSFET models for VLSI circuit simulation: theory and practice. Springer, New York

ATLAS User’s Manual (2014) SILVACO Int., Santa Clara, CA

Barsan RM (1981) Analysis and modeling of dual-gate MOSFET’s. IEEE Trans Electron Devices 28:523–534. doi:10.1109/T-ED.1981.20377

Chaujar R, Kaur R, Saxena M, Gupta M, Gupta RS (2008) TCAD assessment of gate electrode workfunction engineered recessed channel (GEWE-RC) MOSFET and its multilayered gate architecture—part I: hot-carrier-reliability evaluation. IEEE Trans Electron Devices 55:2602–2612. doi:10.1109/TED.2008.2003085

Chen X, Tan CM (2014) Modeling and analysis of gate-all-around silicon nanowire FET. Microelectron Reliab 54:1103–1108. doi:10.1016/j.microrel.2013.12.009

De V, Borkar S (1999) Technology and design challenges for low power and high performance. In Proceedings of international symposium on low power electronics and design 163–168

Deb S, Singh NB, Islam N, Sarkar SK (2012) Work function engineering with linearly graded binary metal alloy gate electrode for shortchannel SOI MOSFET. IEEE Trans Nanotechnol 11:472–478. doi:10.1109/TNANO.2011.2177669

Dubey S, Santra A, Saramekala G, Kumar M, Tiwari PK (2013) An analytical threshold voltage model for triple material cylindrical gate all around (TMCGAA) MOSFETs. IEEE Trans Nanotechnol 12:766–774. doi:10.1109/TNANO.2013.2273805

Groeseneken GV (2001) Hot carrier degradation and ESD in submicrometer CMOS technologies: how do they interact? IEEE Trans Device Mater Reliab 1:23–32. doi:10.1109/7298.946457

Gupta N, Chaujar R (2014) Implications of transport models on the analog performance of gate electrode work function engineered (GEWE) SiNW MOSFET. IEEE 2nd international conference on devices, circuits and systems (ICDCS), 1–5. doi:10.1109/ICDCSyst.2014.6926154

Iwai H, Natori K, Shiraishi K, Iwata J, Oshiyama A, Yamada K, Ohmori K, Kakushima K, Ahmet P (2011) Si nanowire FET and its modeling. Sci China Inf Sci Springer 54:1004–1011. doi:10.1007/s11432-011-4220-0

Jeon HJ, Kim YB, Choi M (2009) Standby leakage power reduction technique for nanoscale CMOS VLSI systems. IEEE Trans Instrum Meas 59(5):1127–1133. doi:10.1109/TIM.2010.2044710

Kaur R, Chaujar R, Saxena M, Gupta RS (2007) Hot-carrier reliability and analog performance investigation of DMG-ISEGaS MOSFET. IEEE Trans Electron Devices 54:2556–2560. doi:10.1109/TED.2007.902855

Kranti A, Armstrong GA (2006) Engineering source/drain extension regions in nanoscale double gate (DG) SOI MOSFETs: analytical model and design considerations. Solid State Electron 50:437–447. doi:10.1016/j.sse.2006.02.012

Krieger G, Sikora R, Cuevas PP, Misheloff MN (2001) Moderately doped NMOS (M-LDD)-hot electron and current drive optimization. IEEE Trans Electron Devices 38:121–127. doi:10.1109/16.65745

Long W, Chin KK (1997) Dual material gate field effect transistor (DMGFET). Electron devices meeting tech dig 549–552. doi:10.1109/IEDM.1997.650445

Momose HS, Ono M, Yoshitomi T, Ohguro T, Nakamura S, Saito M, Iwai H (1996) 1.5 nm direct-tunneling gate oxide Si MOSFET’s. IEEE Trans Electron Devices 43:1233–1242. doi:10.1109/16.506774

Mukherjee C, Maiti CK (2012) Silicon nanowire FinFETs. In: X. Peng (ed) Nanowires: recent advances. doi: 10.5772/52591

Nirmal D, Vijayakumar P, Thomas DM, Jebalin BK, Mohankumar N (2013) Subthreshold performance of gate engineered FinFET devices and circuit with high-k dielectrics. Microelectron Reliab 53:499–504. doi:10.1016/j.microrel.2012.09.008

Orouji AA, Kumar MJ (2005) Shielded channel double-gate MOSFET: a novel device for reliable nanoscale CMOS applications. IEEE Trans Device Mater Reliab 5:509–514. doi:10.1109/TDMR.2005.853505

Pan Y, Ng KK, Wei CC (1994) Hot-carrier induced electron mobility and series resistance degradation in LDD NMOSFE’s. IEEE Electron Device Lett 15:499–501. doi:10.1109/55.338416

Sharma S (2012) Comparative analysis of low power and high performance PTM models of CMOS with HiK-metal gate technology at 22 nm. Int J Soft Comput Eng 2:257–261

Sharma D, Vishvakarma SK (2013) Precise analytical model for short channel cylindrical gate (CylG) gate-all-around (GAA) MOSFET. Solid-State Electron 86:68–74. doi:10.1016/j.sse.2012.08.006

Sinha SK, Chaudhury S (2013) Impact of oxide thickness on gate capacitance—a comprehensive analysis on MOSFET, nanowire FET, and CNTFET devices. IEEE Trans Nanotechnol 12:958–964. doi:10.1109/TNANO.2013.2278021

Sohn CW, Kang CY et al (2012) Device design guidelines for nanoscale FinFETs in RF/analog applications. IEEE Electron Device Lett 33:1234–1236. doi:10.1109/LED.2012.2204853

Stratton R (1972) Semiconductor current-flow equations (diffusion and degeneracy). IEEE Trans Electron Devices 19:1288–1292. doi:10.1109/T-ED.1972.17592

Suk SD, Lee S-Y, Kim S-M et al (2005) High performance 5 nm radius twin silicon nanowire MOSFET(TSNWFET): fabrication on bulk Si wafer, characteristics, and reliability. IEEE IEDM Tech Digest. doi:10.1109/IEDM.2005.1609453

Venkatesan S, Neudeck GW, Pierret RF (1992) Dual-gate operation and volume inversion in n-channel SOIMOSFET’s. IEEE Electron Device Lett 13:44–46. doi:10.1109/55.144946

Wang R, Zhuge J, Huang R, Tian Y, Xiao H, Zhang L, Li C, Zhang X, Wang Y (2007) Analog/RF performance of Si nanowire MOSFETs and the impact of process variation. IEEE Trans Electron Devices 54:1288–1294. doi:10.1109/TED.2007.896598

Wang T, Lou L, Lee C (2013) A junctionless gate-all-around silicon nanowire FET of high linearity and its potential applications. IEEE Electron Device Lett 34:478–480. doi:10.1109/LED.2013.2244056

Yang G, Wang S, Wang R (2003) An efficient preconditioning technique for numerical simulation of hydrodynamic model semiconductor devices. Int J Numer Simul Electron Netw Devices Fields 16:387–400. doi:10.1002/jnm.507

Yu B, Wann CHJ, Nowak ED, Noda K, Hu C (1997) Short-channel effect improved by lateral channel engineering in deep-submicronmeter MOSFET’s. IEEE Trans Electron Devices 44:627–634. doi:10.1109/16.563368

Acknowledgments

The authors would like to thank the Microelectronics Research Lab, Department of Engineering Physics, Delhi Technological University (formerly DCE) and one of the authors (Neha Gupta) is grateful to the University Grant Commission (UGC) for providing the necessary financial assistance to carry out this research work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Gupta, N., Kumar, A. & Chaujar, R. Oxide bound impact on hot-carrier degradation for gate electrode workfunction engineered (GEWE) silicon nanowire MOSFET. Microsyst Technol 22, 2655–2664 (2016). https://doi.org/10.1007/s00542-015-2557-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-015-2557-9