Summary

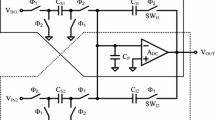

This work focuses on simulation and modeling of integrator leakage in a continuous time (CT) ΔΣ-modulator. The resolution of a ΔΣ-modulator is affected by the integrator leakage that limits the noise characteristics in the low frequency range and at DC. The model describes charge injection and charge sharing when the polarity of the I-DAC (current digital to analog converter) alternates or when the first integrator is chopped for noise and offset cancellation. Charge sharing and charge injection is simulated with Spice. The result of the integrator leakage is an increased noise level at low frequencies and a dead zone at zero input level. A Matlab model describing the charge errors on the first integration capacitor was developed to model the integrator leakage and to estimate the width of the dead zone for small input signals. The simulation model is compared with measurements done on a 3rd order continuous time ΔΣ-modulator.

Zusammenfassung

Dieser Beitrag befasst sich mit der Simulation und Modellierung von Integrator-Leakage in einem zeitkontinuierlichen Sigma-Delta-Modulator. Ladungsverteilung und Ladungsinjektion werden mittels SPICE simuliert. Der Integrator-Leakage bedingt einen erhöhten Wert des Störsignals im unteren Frequenzbereich sowie eine Totzone im Nulldurchgang des Eingangssignals und beeinträchtigt damit die Auflösung des Modulators. Es wurde ein Matlab-Modell entwickelt, das die Ladungsfehler der ersten Integrations-Kapazität modelliert und hierbei eine Abschätzung der Weite der Totzone bei kleinen Eingangssignalen erlaubt. Das entsprechende Modell beschreibt die Ladungsinjektion und die Ladungsteilung, wenn sich die Polarität des I-DACs (Current-Mode DA-Wandler) ändert oder wenn der erste Integrator zur Störsignal- und Offset-Unterdrückung mittels eines Choppers getaktet wird. Die Modellierungsergebnisse zeigen, dass eine Vorladung der parasitären Kapazität am Ausgang des Integrators die Weite der Totzone um den Faktor 10 reduzieren kann. Die Ergebnisse der Modelle (mit implementierter "Vorladung") werden mit Messergebnissen an einem Sigma-Delta-Modulator dritter Ordnung (auf einem Testchip in 0,25-μm-Technologie) verglichen. Die Abweichung zwischen den simulierten und den gemessenen Weiten der Totzone sind auf ein Simulationsmodell zurückzuführen, welches einzelne Einflussgrößen wie Layout-bedingte parasitäre Kapazitäten sowie die Charakteristik der Referenzspannungsquellen unberücksichtigt lässt.

Similar content being viewed by others

References

Feely, O., Chua, L. O. (1991): The effect of integrator leak in ΣΔ-modulation. IEEE Transactions on Circuits and Systems, 38 (11): 1293–1305

Schreier, R., Temes, G. C. (2005): Understanding delta-sigma data converters. Piscataway, NJ: IEEE Press: 50–53

Tiew, Kei-Tee, Chen, Yuan (2005): DAC compensation for continuous-time delta-sigma modulators. Int. Symp. on Circuits and Systems. Digest of technical papers: 3680–3683

Yu, Chong-Gun, Geiger, R. L. (1994): An automatic offset compensation scheme with ping-pong control for CMOS operational amplifiers. IEEE Journal of Solid-State Circuits, 29 (5): 601–610

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Killat, D., Schleifer, H. Modeling of integrator leakage in a continuous time ΔΣ-modulator using Matlab. Elektrotech. Inftech. 125, 118–122 (2008). https://doi.org/10.1007/s00502-008-0520-5

Received:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/s00502-008-0520-5