Abstract

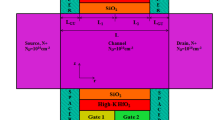

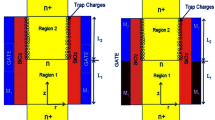

In this work, inclusion of high-k spacer on symmetric underlap S/D junctionless silicon nanowire (SiNW) MOSFET is studied with an aim to analyze more realistic estimation of device performance in sub-20 nm. Comparison made with junctionless silicon nanowire shows that underlap high-k spacer significantly reduces off-current (≈ 64 mV/decade) and achieves high switching ratio > 109 due to fringing field which tends to increase effective channel length. Variation of different high-k spacer values (k = 3.9, 9.1, 11, 25, and 40) is examined and following static and Analog/RF performance is studied: potential, electric field, band diagram, transconductance, device efficiency, quality factor, capacitances, cutoff frequency (fT), intrinsic delay (τ), TFP, EDP, and GBP. It is observed that for high k = 40 (TiO2), device performance of junctionless SiNW MOSFET improves noticeably in comparison to low-k value. In addition, variation of S/D underlap spacer length (Lsp) along with spacer dielectric has also been done and results reveal that TiO2 with 10 nm spacer length is optimum value for upgraded analog/RF performance. Thus, symmetric S/D underlap junctionless SiNW MOSFET can be considered as a promising component in low-power switching component in RFIC circuits.

source voltage (Vgs) and b threshold voltage (Vth) and subthreshold swing (SS) at Vds = 0.2 V for three device structures

Similar content being viewed by others

References

M.T. Abuelmaatti, MOSFET scaling crisis and the evolution of nanoelectronic devices: the need for paradigm shift in electronics engineering education. Proc. Soc. Behav. Sci. 102, 432–437 (2013)

N. Arora, MOSFET Models for VLSI Circuit Simulation Theory and Practice (Springer, New York, 1993).

M. Bohr, MOS transistors: scaling and performance trends. Semicond. Intern. 18, 75–80 (1995)

M. Bohr, K. Mistry, Intel’s revolutionary 22 nm transistor technology. Intel website (2011)

A. Kumar, N. Gupta, R. Chaujar, Analysis of novel transparent gate recessed channel (TGRC) MOSFET for improved analog behaviour. Microsyst. Technol. 22, 1–7 (2015)

A. Kranti, G.A. Armstrong, Engineering source/drain extension regions in nanoscale double gate (DG) SOI MOSFETs: analytical model and design considerations. Solid State Electron. 50(3), 437–447 (2006)

T. Mikolajick, W.M. Weber, Silicon Nanowires: Fabrication and Applications. Anisotropic Nanomaterials (Springer, Berlin, 2015), pp. 1–25

G.L. Priya, N. Balamurugan, New dual material double gate junctionless tunnel FET: subthreshold modeling and simulation. AEU Intern. J. Electron. Commun. 99, 130–138 (2019)

J. Xu, F. Ji, P. Lai, J. Guan, Influence of sidewall spacer on threshold voltage of MOSFET with high-k gate dielectric. Microelectron. Reliab. 48(2), 181–186 (2008)

S. Sahay, M.J. Kumar, Physical insights into the nature of gate-induced drain leakage in ultrashort channel nanowire FETs. IEEE Trans. Electron Dev. 64(6), 2604–2610 (2017)

K. Koley, A. Dutta, B. Syamal, S.K. Saha, C.K. Sarkar, Subthreshold analog/RF performance enhancement of underlap DG FETs with high-k spacer for low power applications. IEEE Trans. Electron. Dev. 60(1), 63–69 (2012)

P.K. Pal, B.K. Kaushik, S. Dasgupta, Investigation of symmetric dual-k spacer trigate FinFETs from delay perspective. IEEE Trans. Electron. Dev. 61(11), 3579–3585 (2014)

C. Shan, Y. Wang, X. Luo, M.-T. Bao, C.-H. Yu, F. Cao, A high-performance channel engineered charge-plasma-based MOSFET with high-k spacer. Superlattices Microstruct. 112, 499–506 (2017)

D. Gracia, D. Nirmal, D.J. Moni, Impact of leakage current in germanium channel based DMDG TFET using drain-gate underlap technique. AEU Intern. J. Electron. Commun. 96, 164–169 (2018)

L. Ansari, B. Feldman, G. Fagas, J.-P. Colinge, J.C. Greer, Simulation of junctionless Si nanowire transistors with 3 nm gate length. Appl. Phys. Lett. 97(6), 062105 (2010)

J.-P. Colinge, C.-W. Lee, A. Afzalian, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. Oneill, A. Blake, M. White, Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

B.-H. Lee, J. Hur, M.-H. Kang, T. Bang, D.-C. Ahn, D. Lee, K.-H. Kim, Y.-K. Choi, A vertically integrated junctionless nanowire transistor. Nano Lett. 16(3), 1840–1847 (2016)

A. Garg, B. Singh, Y. Singh, A new trench double gate junctionless FET: a device for switching and analog/RF applications. AEU Intern. J. Electron. Commun. 118, 153140 (2020)

C.-J. Su, T.-I. Tsai, Y.-L. Liou, Z.-M. Lin, H.-C. Lin, T.-S. Chao, Gate-all-around junctionless transistors with heavily doped polysilicon nanowire channels. IEEE Electron. Dev. Lett. 32(4), 521–523 (2011)

T. Wang, L. Lou, C. Lee, A junctionless gate-all-around silicon nanowire FET of high linearity and its potential applications. IEEE Electron. Dev. Lett. 34(4), 478–480 (2013)

D.-I. Moon, S.-J. Choi, J.P. Duarte, Y.-K. Choi, Investigation of silicon nanowire gate-all-around junctionless transistors built on a bulk substrate. IEEE Trans. Electron. Dev. 60(4), 1355–1360 (2013)

R.D. Trevisoli, R.T. Doria, M. de Souza, M.A. Pavanello, Threshold voltage in junctionless nanowire transistors. Semicond. Sci. Technol. 26(10), 105009 (2011)

I. SILVACO, ATLAS user’s manual. Santa Clara, CA, Ver, vol. 5, 2016

N. Gupta, R. Chaujar, Implications of transport models on the analog performance of gate electrode workfunction engineered (GEWE) silicon nanowire MOSFET. pp. 1–5

G. Iannaccone, G. Curatola, G. Fiori, Effective Bohm quantum potential for device simulators based on drift-diffusion and energy transport, in Simulation of semiconductor processes and devices. ed. by G. Wachutka, G. Schrag (Springer, Berlin, 2004), pp. 275–278

D.-I. Moon, S.-J. Choi, C.-J. Kim, J.-Y. Kim, J.-S. Lee, J.-S. Oh, G.-S. Lee, Y.-C. Park, D.-W. Hong, D.-W. Lee, Silicon nanowire all-around gate MOSFETs built on a bulk substrate by all plasma-etching routes. IEEE Electron. Dev. Lett. 32(4), 452–454 (2011)

S. D. Suk, S.-Y. Lee, S.-M. Kim, E.-J. Yoon, M.-S. Kim, M. Li, C. W. Oh, K. H. Yeo, S. H. Kim, D.-S. Shin, High performance 5 nm radius twin silicon nanowire MOSFET (TSNWFET): Fabrication on bulk Si wafer, characteristics, and reliability. IEDM Tech. Dig. 717–720 (2005)

A. Kumar, B. Tiwari, S. Singh, M.M. Tripathi, R. Chaujar, Radiation analysis of N-channel TGRC-MOSFET: an X-ray dosimeter. IEEE Trans. Electron. Dev. 65(11), 5014–5020 (2018)

O. Moldovan, D. Jimenez, J.R. Guitart, F.A. Chaves, B. Iniguez, Explicit analytical charge and capacitance models of undoped double-gate MOSFETs. IEEE Trans. Electron. Dev. 54(7), 1718–1724 (2007)

G. Doornbos, M. Passlack, Benchmarking of III–V n-MOSFET maturity and feasibility for future CMOS. IEEE Electron. Dev. Lett. 31(10), 1110–1112 (2010)

N. Gupta, R. Chaujar, Optimization of high-k and gate metal workfunction for improved analog and intermodulation performance of Gate Stack (GS)-GEWE-SiNW MOSFET. Superlattices Microstruct. 97, 630–641 (2016)

N. Gupta, A. Kumar, Assessment of high-k gate stack on sub-10nm SOI-FinFET for high-performance analog and RF applications perspective. ECS J. Solid State Sci. Technol. 9(12), 123009 (2020)

N. Gupta, A. Kumar, R. Chaujar, Impact of device parameter variation on RF performance of gate electrode workfunction engineered (GEWE)-silicon nanowire (SiNW) MOSFET. J. Comput. Electron. 14, 798–810 (2015)

N. Gupta, A. Kumar, R. Chaujar, Design considerations and capacitance dependent parametric assessment of gate metal engineered SiNW MOSFET for ULSI switching applications. Silicon 12, 1–10 (2019)

Acknowledgements

The authors are thankful to MER Lab DTU, JIIT and ASH department (ADGITM) for supporting this work.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gupta, N., Kumar, A. Numerical assessment of high-k spacer on symmetric S/D underlap GAA junctionless accumulation mode silicon nanowire MOSFET for RFIC design. Appl. Phys. A 127, 76 (2021). https://doi.org/10.1007/s00339-020-04234-6

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-020-04234-6