Abstract

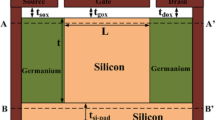

The submitted work presents a designed and analyzed dopingless double-gate tunnel field effect transistor. In the designed dopingless structure, doping is introduced by charge plasma technique and silicon is used as a choice of material. Initially, gate misalignment was done by shifting the bottom gate away from the drain region and toward the drain region by 50% and 100% amount. Further, both gates (top and bottom) have been misaligned by 50% and 100% for analyzing the device for analog and linearity performance. Analog parameters, device parameters and linearity parameters were calculated in order to understand the device behavior. By misaligning gates, it is found that when the bottom gate is shifting away from the source region, both gates have been misaligned by 100% showing that analog and linearity performance of the devices degrades. When the bottom gate is shifted toward the source, both gates have been misaligned by 50% providing better analog and linearity performance. Among all the misaligned structures, when both gates have been misaligned by 50% gives the best result such as ON-state current, OFF-state current, ION/IOFF, and subthreshold slope are 2.3 µA, 5.07 aA, 4.5 × 1011 and 32 mV/decade respectively.

Similar content being viewed by others

References

W. Haensch, E.J. Nowak, R.H. Dennard, P.M. Solomon, A. Bryant, O.H. Dokumaci, M.V. Fischetti, Silicon CMOS devices beyond scaling. IBM J. Res. Dev. 50(45), 339–361 (2006). https://doi.org/10.1147/rd.504.0339

K.K. Young, Short-channel effect in fully depleted SOI MOSFETs. IEEE Trans. Electron Devices 36(2), 399–402 (1989). https://doi.org/10.1109/16.19942

X. Huang, W.C. Lee, C. Kuo, D. Hisamoto, L. Chang, J. Kedzierski, E. Anderson, H. Takeuchi, Y.K. Choi, K. Asano, V. Subramanian, Sub-50 nm P-channel FinFET. IEEE Trans. Electron Devices 48(5), 880–886 (2001). https://doi.org/10.1109/16.918235

S. Saurabh, M. Jagadesh Kumar, Fundamental of tunnel field effect transistors (CRC Press, 2016)

K. Boucart, A.M. Ionescu, Double-gate tunnel FET With high-k gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007). https://doi.org/10.1109/TED.2007.899389

W.Y. Choi, B.G. Park, J.D. Lee, T.J.K. Liu, Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007). https://doi.org/10.1109/LED.2007.901273

A.M. Ionescu, H. Riel, Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(7373), 329 (2011). https://doi.org/10.1038/nature10679

T. Krishnamohan, D. Kim, S. Raghunathan, K. Saraswat, Double-gate strained-ge heterostructure tunneling FET (TFET) With record high drive currents and ≪ 60 mV/dec subthreshold slope. IEEE Int. Electron Devices Meet. (2008). https://doi.org/10.1109/iedm.2008.4796839

J. Madan, R. Chaujar, Gate drain-overlapped-asymmetric gate dielectric-GAA-TFET: a solution for suppressed ambipolarity and enhanced ON state behavior. Appl. Phys. A 122(11), 973 (2016). https://doi.org/10.1007/s00339-016-0510-0

N. Kumar, A. Raman, Design and investigation of charge-plasma-based work function engineered dual-metal-heterogeneous gate Si–Si 0.55 Ge 0.45 GAA-cylindrical NWTFET for ambipolar analysis. IEEE Trans. Electron Devices 66(3), 1468–1474 (2019). https://doi.org/10.1109/ted.2019.2893224

S. Singh, A. Raman, A dopingless gate-all-around (GAA) gate-stacked nanowire FET with reduced parametric fluctuation effects. J. Comput. Electron. 17(3), 967–976 (2018). https://doi.org/10.1007/s10825-018-1166-0

D.H. Morris, U.E. Avci, R. Rios, I.A. Young, Design of low voltage tunneling-FET logic circuits considering asymmetric conduction characteristics. IEEE J. Emerg. Sel. Top. Circuits Syst. 4(4), 380–388 (2014). https://doi.org/10.1109/JETCAS.2014.2361054

S. Yadav, D. Sharma, D. Soni, M. Aslam, Controlling ambipolarity with improved RF performance by drain/gate work function engineering and using high-k dielectric material in electrically doped TFET: proposal and optimization. J. Comput. Electron. 16(3), 721–731 (2017). https://doi.org/10.1007/s10825-017-1019-2

K.E. Moselund, H. Schmid, C. Bessire, M.T. Bjork, H. Ghoneim, H. Riel, InAs–Si nanowire heterojunction tunnel FETs. IEEE Electron Device Lett. 33(10), 1453–1455 (2012). https://doi.org/10.1109/LED.2012.2206789

B.R. Raad, K. Nigam, D. Sharma, P.N. Kondekar, Performance investigation of bandgap, gate material work function and gate dielectric engineered TFET with device reliability improvement. Superlattices Microstruct. 94, 138–146 (2016). https://doi.org/10.1016/j.spmi.2016.04.016

S. Ananad, R.K. Sarin, Hetero-material gate doping-less tunnel FET and its misalignment effects on analog/RF parameters. J. Electron. Mater. 47(5), 2988–2996 (2018). https://doi.org/10.1007/s11664-018-6174-0

T. Han, H. Liu, S. Chen, S. Wang, W. Li, A doping-less tunnel field-effect transistor with Si0.6Ge0.4 hetero junction for the improvement of the on–off current ratio and analog/RF performance. Electronics 8(5), 574 (2019). https://doi.org/10.3390/electronics8050574

A.N. Hanna, H.M. Fahad, M.M. Hussain, InAs/Si hetero-junction nanotube tunnel transistors. Sci. Rep. 5, 9843 (2015). https://doi.org/10.1038/srep09843

L. Gajal, N. Kumar, S.I. Amin, S. Anand, Design and performance enhancement of doping-less field effect transistor with the help of negative capacitance technique. Appl. Phys. A 126(1), 45 (2020). https://doi.org/10.1007/s00339-019-3229-x

N. Kumar, A. Raman, Low voltage charge-plasma based dopingless tunnel field effect transistor: analysis and optimization. Microsyst. Technol (2019). https://doi.org/10.1007/s00542-019-04666-y

S. Anand, A. Singh, S.I. Amin, A.S. Thool, Design and performance analysis of dielectrically modulated doping-less tunnel FET-based label free biosensor. IEEE Sens. J. 19(12), 4369–4374 (2019). https://doi.org/10.1109/JSEN.2019.2900092

H.S. Wong, K.K. Chan, Y. Taur, Self-aligned (top and bottom) double-gate MOSFET with a 25 nm thick silicon channel, in International Electron Devices Meeting. IEDM Technical Digest (1997), pp. 427–430. https://doi.org/10.1109/iedm.1997.650416

C. Yin, P.C. Chan, Investigation of the source/drain asymmetric effects due to gate misalignment in planar double-gate MOSFETs. IEEE Trans. Electron Devices 52(1), 85–90 (2004). https://doi.org/10.1109/TED.2004.841349

H.Y. Wong, K. Shin, M. Chan, The gate misalignment effects of the sub-threshold characteristics of sub-100 nm DG-MOSFETs, in Proceedings 2002 IEEE Hong Kong Electron Devices Meeting (2002), pp. 91–94. https://doi.org/10.1109/hkedm.2002.1029164

S.K. Dargar, A. Dargar, V.M. Srivastava, Effect of gate-underlap lengths in high-k dielectric based Silicon-nanowire gate-all-around TFET, in Proceedings Book (2019)

J. Widiez, J. Lolivier, M. Vinet, T. Poiroux, B. Previtali, F. Daugé, M. Mouis, S. Deleonibus, Experimental evaluation of gate architecture influence on DG SOI MOSFETs performance. IEEE Trans. Electron Devices 52(8), 1772–1779 (2005). https://doi.org/10.1109/TED.2005.851824

S.I. Amin, R.K. Sarin, Analog performance investigation of misaligned double gate junctionless transistor. J. Comput. Electron. 14(3), 675–685 (2015). https://doi.org/10.1007/s10825-015-0705-1

S. Anand, R.K. Sarin, Gate misalignment effects on analog/RF performance of charge plasma-based doping-less tunnel FET. Appl. Phys. A 123(6), 413 (2017). https://doi.org/10.1007/s00339-017-1029-8

R.J. Hueting, B. Rajasekharan, C. Salm, J. Schmitz, The charge plasma PN diode. IEEE Electron Device Lett. 29(12), 1367–1369 (2008). https://doi.org/10.1109/LED.2008.2006864

Sahay S, Kumar MJ, Junctionless devices without any chemical doping. In: Junctionless field-effect transistors: design, modeling, and simulation. pp 281–325, IEEE (2019). https://doi.org/10.1002/9781119523543.ch7

S. Anand, S.I. Amin, R.K. Sarin, Analog performance investigation of dual electrode based doping-less tunnel FET. J. Comput. Electron. 15(1), 94–103 (2016). https://doi.org/10.1007/s10825-015-0771-4

Manual, ATLAS User’S. “Silvaco.” Santa Clara, CA (2010)

M.J. Kumar, S. Janardhanan, Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 60(10), 3285–3290 (2013). https://doi.org/10.1109/TED.2013.2276888

M. Luisier, G. Klimeck, Simulation of nanowire tunneling transistors: from the Wentzel–Kramers–Brillouin approximation to full-band phonon-assisted tunneling. J. Appl. Phys. 107(8), 084507 (2010). https://doi.org/10.1063/1.3386521

J.H. Kim, S. Kim, B. Park, Double-gate TFET with vertical channel sandwiched by lightly doped Si. IEEE Trans. Electron Devices 66(4), 1656–1661 (2019). https://doi.org/10.1109/TED.2019.2899206

P.N. Kondekar, K. Nigam, S. Pandey, D. Sharma, Design and analysis of polarity controlled electrically doped tunnel FET with bandgap engineering for analog/RF applications. IEEE Trans. Electron Devices 64(2), 412–418 (2016). https://doi.org/10.1109/TED.2016.2637638

B.V. Chandan, S. Dasari, S. Yadav, D. Sharma, Approach to suppress ambipolarity and improve RF and linearity performances on ED-Tunnel FET. Micro & Nano Letters 13(5), 684–689 (2018). https://doi.org/10.1049/mnl.2017.0814

S.M. Biswal, B. Baral, D. De, A. Sarkar, Study of effect of gate-length downscaling on the analog/RF performance and linearity investigation of InAs-based nanowire Tunnel FET. Superlattices Microstruct. 91, 319–330 (2016). https://doi.org/10.1016/j.spmi.2016.01.021

A.K. Gupta, A. Raman, N. Kumar, Design and investigation of a novel charge plasma-based core-shell ring-TFET: analog and linearity analysis. IEEE Trans. Electron Devices 66(8), 3506–3512 (2019). https://doi.org/10.1109/TED.2019.2924809

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Shekhar, D., Raman, A. Design and analysis of dual-gate misalignment on the performance of dopingless tunnel field effect transistor. Appl. Phys. A 126, 441 (2020). https://doi.org/10.1007/s00339-020-03615-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-020-03615-1