Abstract

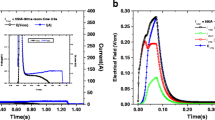

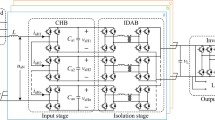

The increase in distribution power demand and distributed generation may lead to a rise in power substation fault current levels. One possible solution to this problem is the use of a solid-state fault current limiter (SS-FCL). In this context, this paper proposes the concept of a bridge-type solid-state device switching an air-core reactor as an SS-FCL topology. The overvoltage protection system details are presented, along with an explanation of the fault detection algorithm control's principle. An experimental setup is designed to evaluate various events in addition to the short-circuit, such as load-steps, harmonic loads, motor startups, and transformer’s inrush. Fault current is detected within one millisecond, with a total reduction of 42%. The overvoltage protection system clamped the peak voltage across the semiconductor switch and kept the dV/dt below the maximum stipulated. The load input tests showed a proper limiting operation and provided that the device is within the parameterization range.

Similar content being viewed by others

References

Morandi A (2013) State of the art of superconducting fault current limiters and their application to the electric power system. Phys C Supercond 484:242–247. https://doi.org/10.1016/j.physc.2012.03.004

Alam M, Abido M, El-Amin I (2018) Fault current limiters in power systems: a comprehensive review. Energies 11(5):1025. https://doi.org/10.3390/en11051025

Chewale M, Savakhande V, Jadhav R, Kupwade R, Siddha P (2019) “A comprehensive review on fault current limiter for power network. In: 2019 International conference on recent advances in energy-efficient computing and communication (ICRAECC), Nagercoil, India, pp. 1–7. https://doi.org/10.1109/ICRAECC43874.2019.8995098.

Barzegar-Bafrooei MR, Akbari Foroud A, Dehghani Ashkezari J, Niasati M (2019) On the advance of SFCL: a comprehensive review. IET Gener Transm Distrib 13(17):3745–3759. https://doi.org/10.1049/iet-gtd.2018.6842

Abramovitz A, Smedley M (2012) Survey of solid-state fault current limiters. IEEE Trans Power Electron 27(6):2770–2782. https://doi.org/10.1109/TPEL.2011.2174804

Hamada AM, Ghoneim SSM, Abdelwahab SAM, Abdellatif WSE (2021) Performance analysis of three-phase hybrid fault current limiter with one commutation circuit. Int J Electr Power Energy Syst 133:107297. https://doi.org/10.1016/j.ijepes.2021.107297

Naphade V, Ghate V, Dhole G (2021) Experimental analysis of saturated core fault current limiter performance at different fault inception angles with varying DC bias. Int J Electr Power Energy Syst 130:106943. https://doi.org/10.1016/j.ijepes.2021.106943

Khorasaninejad M, Radmehr M, Firouzi M, Koochaki A (2022) Application of a resistive mutual-inductance fault current limiter in VSC-based HVDC system. Int J Electr Power Energy Syst 134:107388. https://doi.org/10.1016/j.ijepes.2021.107388

Heidary A, Rouzbehi K, Mehrizi-Sani A, Sood VK (2022) A self-activated fault current limiter for distribution network protection. IEEE J Emerg Sel Top Power Electron 10(4):4626–4633. https://doi.org/10.1109/JESTPE.2021.3109217

Heidary A, Yazdani-Asrami M, Hesami M, Sood V (2022) The TRV improvement of fast circuit breakers using solid-state series superconducting reactor. IEEE Trans Power Deliv. https://doi.org/10.1109/TPWRD.2022.3211778

Leung EM et al (1997) High temperature superconducting fault current limiter development. IEEE Trans App Supercond 7(2):985–988. https://doi.org/10.1109/77.614670

Morandi A, Imparato S (2009) A DC-operating resistive-type superconducting fault current limiter for AC applications. Supercond Sci Technol 22(4):045002. https://doi.org/10.1088/0953-2048/22/4/045002

Imparato S et al (2010) Experimental evaluation of AC losses of a DC restive SFCL prototype. IEEE Trans Appl Supercond 20(3):1199–1202. https://doi.org/10.1109/TASC.2010.2043726

Morandi A et al (2010) Design of a DC resistive SFCL for application to the 20 kV distribution system. IEEE Trans Appl Supercond 20(3):1122–1126. https://doi.org/10.1109/TASC.2010.2043723

Rezaee M, Harley RG (2018) Resonance-based fault current limiters: theory, applications, and assessment. IEEE Trans Ind Appl 54(4):3066–3076. https://doi.org/10.1109/TIA.2018.2817626

Martins Lanes M, Carvalho Braga HA, Gomes Barbosa P (2007) Fault current limiter based on resonant circuit controlled by power semiconductor devices. IEEE Lat Am Trans 5(5):311–320. https://doi.org/10.1109/TLA.2007.4378523

Sarmiento HG (2007) “A fault current limiter based on an LC resonant circuit: design, scale model and prototype field tests”. In: 2007 iREP symposium—bulk power system dynamics and control—VII. revitalizing operational reliability, Charleston, SC, USA, pp. 1–5. https://doi.org/10.1109/IREP.2007.4410570

Naderi SB, Jafari M, Tarafdar Hagh M (2013) Parallel-resonance-type fault current limiter. IEEE Trans Ind Electron 60(7):2538–2546. https://doi.org/10.1109/TIE.2012.2196899

Genji T, Nakamura O, Isozaki M, Yamada M, Morita T, Kaneda M (1994) 400 V class high-speed current limiting circuit breaker for electric power system. IEEE Trans Power Deliv 9(3):1428–1435. https://doi.org/10.1109/61.311172

Ahmed MMR, Putrus G, Ran L, Penlington R (2006) Development of a prototype solid-state fault-current limiting and interrupting device for low-voltage distribution networks. IEEE Trans Power Deliv 21(4):1997–2005. https://doi.org/10.1109/TPWRD.2006.874584

Guo W et al (2014) Multicell fault current limiter. IEEE Trans Ind Electron 61(4):2071–2080. https://doi.org/10.1109/TIE.2013.2263773

Adapa R, Piccone D (2012) “Solid-state fault current limiter development : design and testing update of a 15kV SSCL power stack DOE/CH/11354. 1043100. https://doi.org/10.2172/1043100

Tseng H-T, Jiang W-Z, Lai J-S (2018) A modified bridge switch-type flux-coupling nonsuperconducting fault current limiter for suppression of fault transients. IEEE Trans Power Deliv 33(6):2624–2633. https://doi.org/10.1109/TPWRD.2018.2820428

Nourmohamadi H, Sabahi M, Babaei E, Abapour M (2018) A new structure of fault current limiter based on the system impedance with fast eliminating method and simple control procedure. IEEE Trans Ind Electron 65(1):261–269. https://doi.org/10.1109/TIE.2017.2721909

Nourmohamadi H, Sabahi M, Balsara PT, Babaei E, Hosseini SH, Fakhim-Babaei A (2020) New concept for fault current limiter with voltage restoration capability. IEEE Trans Ind Electron 67(12):10001–10010. https://doi.org/10.1109/TIE.2019.2962418

Bitencourt A, Dias DHN, França BW, Sass F, Sotelo GG (2021) Design and tests of solid-state fault current limiters prototypes. Int Trans Electr Energy Syst 31(2):e12738. https://doi.org/10.1002/2050-7038.12738

Acknowledgements

The authors would like to thank Light Serviços de Eletricidade S/A by granting the ANEEL 133/20 R and D project entitled "Development of a Medium Voltage Prototype Fault Current Limiter for Distribution Systems." This study was financed in part by the Brazilian Federal Agency for Support and Evaluation of Graduate Education (Coordenação de Aperfeiçoamento de Pessoal de Nível Superior—Brasil, CAPES)—Finance Code 001. The authors would also like to thank the National Council for Scientific and Technological Development (Conselho Nacional de Desenvolvimento Científico e Tecnológico, CNPq), the National Institute of Science and Technology in Electricity (Instituto Nacional de Ciência e Tecnologia em Energia Elétrica, INCT-Inerge), the Rio de Janeiro Research Support Foundation (Fundação de Amparo à Pesquisa do Estado do Rio de Janeiro, FAPERJ), and Centro Integrado de Tradução e Escrita (CITE/UFF) for assistance with English language translation and developmental editing.

Funding

This study was financed in part by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior—Brasil (CAPES)—Finance Code 001, and an ANEEL 133/20 R and D project entitled "Development of a Medium Voltage Prototype Fault Current Limiter for Distribution Systems."

Author information

Authors and Affiliations

Contributions

AB helped in conceptualization, investigation, methodology, writing—original draft, writing—review and editing, data curation, visualization, and formal analysis; CN helped in conceptualization, investigation, and methodology; GS helped in conceptualization, investigation, and methodology; DD worked in supervision, validation, and funding acquisition; BF worked in supervision, validation, and funding acquisition; FS worked in supervision, validation, and funding acquisition; and GS worked in supervision, validation, and funding acquisition.

Corresponding author

Ethics declarations

Competing interests

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Bitencourt, A., Nogueira, C., dos Santos, G. et al. Analysis and experimental tests of a solid-state fault current limiter. Electr Eng 105, 3219–3228 (2023). https://doi.org/10.1007/s00202-023-01880-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00202-023-01880-w