Abstract

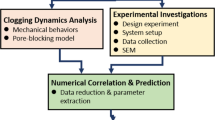

Control and dummy (C/D) wafers are indispensable materials used in a semiconductor fab. C/D wafers stored in a high-grade buffer can be downgraded to several low-grade buffers. The downgrade decision is to determine the amount to downgrade for each of these low-grade buffers. Previous literature solves the downgrade decision by considering only the instantaneous WIP information, which is a short-term approach and may not yield the optimum solution in the long run. This paper presents an LP model to solve the downgrade decision problem, which aims to minimize the long-term daily usage of brand-new C/D wafers in a fab. The formulated problem assumes that the storage cost of C/D wafers is much less than the usage cost. This assumption has been justified by analyzing the cost structure of C/D wafers in a typical fab site.

Similar content being viewed by others

References

Wong CY, Hood SJ (1994) Impact of process monitoring in semiconductor manufacturing. IEEE/CPMT International Electronics Manufacturing Technology Symposium, pp 221–225

Wu JE (1997) The construction of dispatching rule for control wafer in diffusion area. Dissertation, National Chiao Tung University, Hsin-Chu, Taiwan

Popovich SB, Chilton SR, Kilgore B (1997) Implementation of a test wafer inventory tracking system to increase efficiency in monitor wafer usage. IEEE/SEMI Advanced Semiconductor Manufacturing Conference, pp 440–443

Chu YF (1998) The inventory management model for control and dummy wafers. Dissertation, National Chiao Tung University, Hsin-Chu, Taiwan

Watanabe A, Kobayashi T, Egi T, Yoshida T (1999) Continuous and independent monitor wafer reduction in DRAM fab. IEEE International Symposium on Semiconductor Manufacturing Conference, pp 303–306

Foster B, Meyersdorf D, Padillo JM, Brenner R (1998) Simulation of test wafer consumption in a semiconductor facility. IEEE/SEMI Advanced Semiconductor Manufacturing Conference, pp 298–302

Chen HC, Lee CE (2000) Downgrading management for control and dummy wafers. J Chin Inst Ind Eng 17:437–449

Chen HC (2003) Control and dummy wafers management. Dissertation, National Chiao Tung University, Hsin-Chu, Taiwan

Liu CP (2002) Control wafer planning for semiconductor wafer fabrication. Dissertation, National Tsing Hua University, Hsin-Chu, Taiwan

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wu, MC., Chien, C. & Lu, K. Downgrade decision for control/dummy wafers in a fab. Int J Adv Manuf Technol 26, 585–590 (2005). https://doi.org/10.1007/s00170-003-2031-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00170-003-2031-1