Abstract

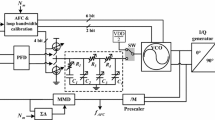

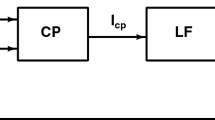

A novel delay cell circuit for differential ring oscillator (DRO) with large tuning range along with application in charge pump phase lock loop (CP-PLL) frequency synthesizer has been presented in this paper. Using 0.18\(\mu \)m CMOS technology with power supply of 1.8 V, the two DRO architectures: 3-stage and 5-stage, were built and simulated. In both 3-stage and 5-stage DROs, single controlled voltage is employed. The suggested 3-stage and 5-stage DRO circuits generate a tuning range of 96.77 MHz\(-\)5.296 GHz and 36.33 MHz\(-\)2.803 GHz, respectively. The % total harmonic distortion (%THD) of both DRO architectures is also evaluated. The suggested 3-stage and 5-stage DROs consume 6.63 mW and 11.05 mW power at an oscillation frequency of 4.76 GHz and 2.479 GHz, respectively. At an offset frequency of 10 MHz from the oscillation frequency, the proposed circuits have phase noise of \(-\)119.93 dBc/Hz and \(-\)128.24 dBc/Hz, respectively. The layout of proposed design has been drawn and pre- and post-layout simulation results show satisfactory variations of tuning range and phase noise of proposed design. The suggested circuit’s robustness is verified with the help of PVT and Monte Carlo analysis. When compared to contemporary research, the proposed DROs have the widest tuning range. Proposed DRO application in CP-PLL frequency synthesizer has locking time of 1.17 \(\upmu \)s and shows good settling behaviour with dynamic parameter variations.

Similar content being viewed by others

Data Availability

The datasets generated during and/or analysed during the current study are available from the corresponding author on reasonable request.

References

R. Ahmad, A.M. Joshi, D. Boolchandani, T. Varma, Novel programmable readout amplifier and potentiostat for glucose sensing applications. SN Comput. Sci. 4(2), 100 (2022)

A. Basaligheh, P. Saffari, W. Winkler, K. Moez, A wide tuning range, low phase noise, and area efficient dual-band millimeter-wave CMOS VCO based on switching cores. IEEE Trans. Circuits Syst. I: Regul. Pap. 66(8), 2888–2897 (2019)

Z.-Z. Chen, T.-C. Lee, The design and analysis of dual-delay-path ring oscillators. IEEE Trans. Circuits Syst. I: Regul. Pap. 58(3), 470–478 (2010)

J. Choi, K. Lim, J. Laskar, A ring VCO with wide and linear tuning characteristics for a cognitive radio system, in 2008 IEEE Radio Frequency Integrated Circuits Symposium (2008), pp. 395–398

C. Danfeng, R. Junyan, D. Jingjing, L. Wei, L. Ning, A multiple-pass ring oscillator based dual-loop phase-locked loop. J. Semicond. 30(10), 105014 (2009)

G. De Luca, P. Bolcato, R. Larcheveque, J. Rommes, W.H. Schilders, Fast and accurate time-domain simulations of integer-N PLLs. IEEE Trans. Circuits Syst. I: Regul. Pap. 64(4), 931–944 (2016)

A. Demir, Computing timing jitter from phase noise spectra for oscillators and phase-locked loops with white and \(1/f \) noise. IEEE Trans. Circuits Syst. I: Regul. Pap. 53(9), 1869–1884 (2006)

Y.A. Eken, J.P. Uyemura, A 5.9-GHz voltage-controlled ring oscillator in 0.18-/spl mu/m CMOS. IEEE J. Solid-State Circuits 39(1), 230–233 (2004)

A. Fahim, Wideband phase-locked-loop-based frequency synthesis, in Radio Frequency Integrated Circuit Design for cognitive radio systems (2015), pp. 139–186

A. Fakhfakh, N. Milet-Lewis, Y. Deval, H. Levi, Study and behavioural simulation of phase noise and jitter in oscillators, in The 2001 IEEE International Symposium on Circuits and Systems (Cat. No. 01CH37196) (2001), vol. 5, pp. 323–326 (2001)

X. Fan, L. Tang, Y. Wang, L. Yu, L. Yuan, Z. Yang, Z. Wang, A 1 V 0.18 \(\mu \)m fully integrated integer-N frequency synthesizer for 2.4 GHz wireless sensor network applications. Analog Integr. Circuits Signal Process. 82(1), 251–264 (2015)

E. Fernández, A. Paredes, V. Sala, L. Romeral, A simple method for reducing THD and improving the efficiency in CSI topology based on SiC power devices. Energies 11(10), 2798 (2018)

P. Gupta, M. Kumar, Design of modified low power CMOS differential ring oscillator using sleepy transistor concept. Analog Integr. Circuits Signal Process. 96(1), 87–104 (2018)

A. Harjimiri, S. Limotyrakis, T. Lee, Jitter and phase noise in ring oscillator. IEEE J. Solid-State Circuits 34(6), 790–804 (1999)

M.H. Kashani, A. Tarkeshdouz, R. Molavi, E. Afshari, S. Mirabbasi, A wide-tuning-range low-phase-noise mm-wave CMOS VCO with switchable transformer-based tank. IEEE Solid-State Circuits Lett. 1(4), 82–85 (2018)

M.R. Khanzadi, A. Panahi, D. Kuylenstierna, T. Eriksson, A model-based analysis of phase jitter in RF oscillators, in 2012 IEEE International Frequency Control Symposium Proceedings (2012), pp. 1–4

B.-S. Kim, A low-noise, 900-MHz VCO in 0.6-m CMOS. IEEE J. Solid-state Circuits 34(5):586–591 (1999)

M. Kim, S. Choi, T. Seong, J. Choi, A low-jitter and fractional-resolution injection-locked clock multiplier using a DLL-based real-time PVT calibrator with replica-delay cells. IEEE J. Solid-State Circuits 51(2), 401–411 (2015)

M. Kumar, D. Dwivedi, A low power CMOS-based VCO design with I-MOS varactor tuning control. J. Circuits Syst. Comput. 27(10), 1850160 (2018)

N. Kumar, M. Kumar, Design of CMOS-based low-power high-frequency differential ring VCO. Int. J. Electron. Lett. 7(2), 143–153 (2019)

H.S. Lee, D.M. Kang, S.J. Cho, C.W. Byeon, C.S. Park, Low-power, low-phase-noise g m-boosted 10-ghz VCO with center-tap transformer and stacked transistor. IEEE Trans. Circuits Syst. II: Express Briefs 67(10), 1710–1714 (2019)

S.-Y. Lee, L.-H. Wang, Q. Fang, A low-power RFID integrated circuits for intelligent healthcare systems. IEEE Trans. Inf. Technol. Biomed. 14(6), 1387–1396 (2010)

G.A. Leonov, N.V. Kuznetsov, M.V. Yuldashev, R.V. Yuldashev, Hold-in, pull-in, and lock-in ranges of PLL circuits: rigorous mathematical definitions and limitations of classical theory. IEEE Trans. Circuits Syst. I: Regul. Pap. 62(10), 2454–2464 (2015)

X. Li, J. Zhang, Y. Zhang, W. Wang, H. Liu, C. Lu, A 5.7–6.0 GHz CMOS PLL with low phase noise and \(-\)68 dBc reference spur. AEU Int. J. Electron. Commun. 85, 23–31 (2018)

H.Q. Liu, W.L. Goh, L. Siek, W.M. Lim, Y.P. Zhang, A low-noise multi-GHz CMOS multiloop ring oscillator with coarse and fine frequency tuning. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 17(4), 571–577 (2009)

H.Q. Liu, L. Siek, W.L. Goh, W.M. Lim, A 7-GHz multiloop ring oscillator in 0.18-\(\mu \)m CMOS technology. Anal. Integr. Circuits Signal Process. 56(3), 179–184 (2008)

Y.-L. Lo, Y.-T. Chiu, A high-accuracy, high-resolution, and low-cost all-digital temperature sensor using a voltage compensation ring oscillator. IEEE Sens. J. 16(1), 43–52 (2015)

J.A. McNeill, Jitter in ring oscillators. IEEE J. Solid-State Circuits 32(6), 870–879 (1997)

Y. Miyake, Y. Sato, S. Kajihara, A selection method of ring oscillators for an on-chip digital temperature and voltage sensor, in 2019 IEEE International Test Conference in Asia (ITC-Asia) (2019), pp. 13–18

T. Nakura, M. Ikeda, K. Asada, Ring oscillator based random number generator utilizing wake-up time uncertainty, in 2009 IEEE Asian Solid-State Circuits Conference (2009), pp. 121—124

R. Ratan, Design of a phase locked loop based clocking circuit for high speed serial link applications (2014)

B. Razavi, Design of CMOS Phase-Locked Loops: From Circuit Level to Architecture Level (Cambridge University Press, Cambridge, 2020)

J.W. Rogers, C. Plett, F. Dai, Integrated Circuit Design for High-Speed Frequency Synthesis (Artech House Boston, London, 2006)

V. Ruparelia, M. Chakraverty, S.S. Desai, P. Harisankar, Performance comparison of commercially available RF analog and mixed signal simulation tools using benchmark circuits, in Microelectronics, Electromagnetics and Telecommunications (2018), pp. 443–451

T.H. Saika,, M.T. Amin, Low power wide tuning range differential ring VCO for RFID transponder, in 2019 22nd International Conference on Computer and Information Technology (ICCIT) (2019), pp. 1–6

S.S.A. Saleh, N. Masoumi, I. Member, Wide-tuning-range, low-phase-noise quadrature ring oscillator exploiting a novel noise canceling technique. AEU Int. J. Electron. Commun. 66(5), 372–379 (2012)

S. Salem, M. Tajabadi, M. Saneei, The design and analysis of dual control voltages delay cell for low power and wide tuning range ring oscillators in 65 nm CMOS technology for CDR applications. AEU Int. J. Electron. Commun. 82, 406–412 (2017)

C. Sánchez-Azqueta, S. Celma, F. Aznar, A 0.18 \(\mu \)m CMOS ring VCO for clock and data recovery applications. Microelectron. Reliab. 51(12), 2351–2356 (2011)

G.K. Sharma, A.K. Johar, D. Boolchandani, Low power, wide range synthesizer for 534 MHz-18.56 GHz band with FoM of- 192.45 dBc/Hz. J. Circuits Syst. Comput. 31(02), 2250032 (2022)

G.K. Sharma, T.B. Kumar, A.K. Johar, D. Boolchandani, A wide tuning range, low noise oscillator with FoM of-188 dBc/Hz in 45 nm CMOS. AEU Int. J. Electron. Commun. 125, 153390 (2020)

M.-L. Sheu, Y.-S. Tiao, L.-J. Taso, A 1-V 4-GHz wide tuning range voltage-controlled ring oscillator in 0.18 \(\mu \)m CMOS. Microelectron. J. 42(6), 897–902 (2011)

C.-C. Sun, A. Hahn, C.-C. Liu, Cyber security of a power grid: state-of-the-art. Int. J. Electr. Power Energy Syst. 99, 45–56 (2018)

Y. Sun, S.H. Ye, Y. Ye, Design of medical wireless sensor network. Adv. Mater. Res. 314, 2486–2490 (2011)

A. Tsitouras, F. Plessas, Ultra-wideband, low-power, inductorless, 3.1–4.8 GHz, CMOS VCO. Circuits Syst. Signal Process. 30(2), 263–285 (2011)

T. Wu, K. Mayaram, U.-K. Moon, An on-chip calibration technique for reducing supply voltage sensitivity in ring oscillators. IEEE J. Solid-State Circuits 42(4), 775–783 (2007)

C. Zhang, Z. Li, J. Fang, J. Zhao, Y. Guo, J. Chen, A Novel high-speed CMOS fully-differentical ring VCO, in 2014 12th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT) (2014), pp. 1–3

H. Zhang, H. Li, Y. Wang, A tunable CMOS ring VCO in a wide frequency range, in 2011 International Conference on Multimedia Technology (2011), pp. 6475–6478

B. Zheng, L. Ding, J. Jin, A filter enhanced capacitively phase-coupled low noise 0.6-to-3 GHz Ring VCO, in 2016 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT) (2016), pp. 1531–1533

Acknowledgements

This research is supported by the Regional Academic Center for Space (RAC-S) sponsored research project. The Grant is received under RAC-S project RAC-S/PRO/21-22/01 at MNIT Jaipur. The authors are grateful to the RAC-S sponsored project, MNIT Jaipur, for providing the support to carry out the present research.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Ahmad, R., Sharma, G.K., Boolchandani, D. et al. A Novel Wide Tuning Range Differential Ring Oscillator Application in Dynamically Stable and 1.17 \(\upmu \)s Lock Time CP-PLL Frequency Synthesizer. Circuits Syst Signal Process 42, 7045–7072 (2023). https://doi.org/10.1007/s00034-023-02466-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-023-02466-4