Abstract

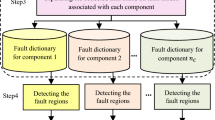

Test node selection for finding faults in complex analog circuits is essential in fault dictionary techniques to reduce test cost in terms of time, to reduce the number of input variables of the circuit under test required for faults detection, and hence to minimize fault dictionary size. The proposed faster regional convolutional neural network-based test node selection procedure evaluates the relationship between the input variables (node voltage) using correlation measures to choose test nodes for fault diagnosis. A fault dictionary is built by measuring node voltages for different fault cases. For the given fault dictionary, initially the correlation coefficient of input variables is determined and the node correlation matrix is obtained. Test node selection proposed here determines the minimum number of nodes required for testing by finding the nodes with the highest number of zero correlations. Then the node correlation matrix is updated by removing the minimum nodes identified, and the nodes with the highest number of zero and weak correlation are found from the updated node correlation matrix for better fault coverage. Simulation results are presented by considering both hard and soft faults cases, and the performance of the proposed approach is evaluated using fault detection efficiency of test nodes of CUT. The comparative analysis is carried out for the proposed approach and various other techniques by evaluating various metrics, namely the computational time, accuracy, precision, recall, f-measure and specificity. The computational time and the accuracy rate attained by the proposed approach are 0.2 s and 97.4%, respectively.

Similar content being viewed by others

Data Availability

The data presented in this study are available on request from the corresponding author.

References

A. Bilski, J. Wojciechowski, Automatic parametric fault detection in complex analog systems based on a method of minimum node selection. Int. J. Appl. Math. Comput. Sci. 26(3), 655–668 (2016). https://doi.org/10.1515/amcs-2016-0045

S. Chauhan, G. Vashishtha, A. Kumar, Approximating parameters of photovoltaic models using an amended reptile search algorithm. J Ambient Intell Human Comput (2022). https://doi.org/10.1007/s12652-022-04412-9

Y. Gao, C. Yang, S. Tian, F. Chen, Entropy-based test point evaluation and selection method for analog circuit fault diagnosis. Math. Probl. Eng. (2014). https://doi.org/10.1155/2014/259430

T. Golonek, J. Rutkowski, Genetic-algorithm-based method for optimal analog test points selection. IEEE Trans. Circuits Syst. II Express Briefs 54(2), 117–121 (2007). https://doi.org/10.1109/TCSII.2006.884112

O. Karaca, K. Kirscher, A. Laroche, A. Tributsch, L. Maurer, G. Pelz, Fault grouping for fault injection based simulation of AMS circuits in the context of functional safety. in 13th International Conference on Synthesis, Modeling, Analysis and Simulation Methods, and Applications to Circuit Design (SMACD), 2016, Lisbon, 1–4. https://doi.org/10.1109/SMACD.2016.7520721

M. Khanlari, M. Ehsanian, A test point selection approach for DC analog circuits with a large number of predefined faults. Analog IntegrCirc Sig Process 102, 225–235 (2020). https://doi.org/10.1007/s10470-019-01550-7

H. Lei, K. Qin, Greedy randomized adaptive search procedure for analog test point selection. Analog IntegrCirc Sig Process 79, 371–383 (2014). https://doi.org/10.1007/s10470-014-0273-5

X. Liu, Y. Lin, H. Jiang, X. Miao, J. Chen, Slippage fault diagnosis of dampers for transmission lines based on faster R-CNN and distance constraint. Electr. Power Syst. Res. 199, 107449 (2021)

Q. Ma, Y. He, F. Zhou, P. Song, Test point selection method for analog circuit fault diagnosis based on similarity coefficient. Math. Probl. Eng. (2018). https://doi.org/10.1155/2018/9714206

S. Mosin, An approach to reducing the complexity of neuromorphic fault dictionary construction for analog integrated circuits. in 28th International Conference Radioelektronika (RADIOELEKTRONIKA), Prague, 2018, pp. 1–6. https://doi.org/10.1109/RADIOELEK.2018.8376404

V.C. Prasad, N.S.C. Babu, Selection of test nodes for analog fault diagnosis in dictionary approach. IEEE Trans. Instrum. Meas. 49(6), 1289–1297 (2000). https://doi.org/10.1109/19.893273

J. Rutkowski, J. Machniewski, Integer-code DC fault dictionary. in 2000 IEEE International Symposium on Circuits and Systems (ISCAS), Geneva, Switzerland, 5, 713–716. https://doi.org/10.1109/ISCAS.2000.857594

S. Saeedi, S.H. Pishgar, M. Eslami, Optimum test point selection method for analog fault dictionary techniques. Analog IntegrCirc. Signal Process. 100, 167–179 (2019). https://doi.org/10.1007/s10470-019-01453-7

J. Shi, Y. Deng, Z. Wang, Q. He, A combined method for analog circuit fault diagnosis based on dependence matrices and intelligent classifiers. IEEE Trans. Instrum. Meas. 69(3), 782–793 (2019)

G. Vashishtha, S. Chauhan, A. Kumar, R. Kumar, An ameliorated African vulture optimization algorithm to diagnose the rolling bearing defects. Meas. Sci. Technol. 33(7), 075013 (2022)

G. Vashishtha, S. Chauhan, N. Yadav, A. Kumar, R. Kumar, A two-level adaptive chirp mode decomposition and tangent entropy in estimation of single-valued neutrosophic cross-entropy for detecting impeller defects in centrifugal pump. Appl. Acoust. 197, 108905 (2022)

G. Vashishtha, R. Kumar, An effective health indicator for the Pelton wheel using a Levy flight mutated genetic algorithm. Meas. Sci. Technol. 32(9), 094003 (2021)

G. Vashishtha, R. Kumar, Autocorrelation energy and aquila optimizer for MED filtering of sound signal to detect bearing defect in Francis turbine. Meas. Sci. Technol. 33(1), 015006 (2021)

G. Vashishtha, R. Kumar, An amended grey wolf optimization with mutation strategy to diagnose bucket defects in Pelton wheel. Measurement 187, 110272 (2022)

C. Yang, Multiple soft fault diagnosis of analog filter circuit based on genetic algorithm. IEEE Access 8, 8193–8201 (2020)

H. Yang, C. Meng, C. Wang, Data-driven feature extraction for analog circuit fault diagnosis using 1-D convolutional neural network. IEEE Access 8, 18305–18315 (2020)

C. Yang, S. Tian, B. Long et al., A Novel test point selection method for analog fault dictionary techniques. J Electron Test 26, 523–534 (2010). https://doi.org/10.1007/s10836-010-5169-4

C. Yang, S. Tian, B. Long et al., A test points selection method for analog fault dictionary techniques. Analog IntegrCirc. Signal Process. 63, 349–357 (2010). https://doi.org/10.1007/s10470-009-9369-8

C. Yang, S. Tian, B. Long, F. Chen, Methods of handling the tolerance and test-point selection problem for analog-circuit fault diagnosis. IEEE Trans. Instrum. Meas. 60(1), 176–185 (2011). https://doi.org/10.1109/TIM.2010.2050356

X. Yuan, Z. Liu, Z. Miao, Z. Zhao, F. Zhou, Y. Song, Fault diagnosis of analog circuits based on IH-PSO optimized support vector machine. IEEE Access 7, 137945–137958 (2019)

D. Zhao, Y.A. He, New test point selection method for analog circuit. J. Electron. Test 31, 53–66 (2015). https://doi.org/10.1007/s10836-015-5506-8

G. Zhao, Y. Liu, Y. Gao, Z. Jiang, C. Hu, A new approach for analog circuit fault diagnosis based on extreme learning machine. in 2018 Prognostics and System Health Management Conference (PHM-Chongqing) (pp. 196–200). IEEE. (2018)

T. Zhong, J. Qu, X. Fang, H. Li, Z. Wang, The intermittent fault diagnosis of analog circuits based on EEMD-DBN. Neurocomputing 436, 74–91 (2021)

Funding

This research received no funding.

Author information

Authors and Affiliations

Contributions

All authors have read and agreed to the published version of the manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no conflict of interest.

Human and Animal Rights

This article does not contain any studies with human or animal subjects performed by any of the authors.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Puvaneswari, G. Test Node Selection for Fault Diagnosis in Analog Circuits using Faster RCNN Model. Circuits Syst Signal Process 42, 3229–3254 (2023). https://doi.org/10.1007/s00034-022-02276-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02276-0