Abstract

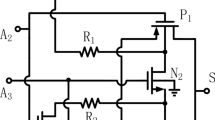

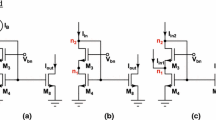

In this paper, a double-pole double-throw analog switch with n-channel architecture driven by a charge pump is described. The architecture proposed in this paper not only can reduce the on-resistance of the complementary metal oxide semiconductor (CMOS) switch, but also can realize a stable on-resistance within the full swing range of the input signal. This analog switch has the characteristics of high-speed, low-voltage, and high linearity, which is suitable for high-speed USB (Universal Serial Bus) 2.0 applications and meets low-speed and full-speed USB requirements. The test chip using a 0.25 μm BCD (bipolar–CMOS–DMOS) process confirms the characteristics of the switch. It uses + 2.8 to + 5.5 V single power supply, and the normal operating temperature range is − 40 to + 85 °C. This switch has an over-voltage protection function, which can prevent damage to the switch from the high input voltage. Besides, the switch port can realize dual-direction transmission. The analog switch designed in this paper solves some problems of traditional analog switches, such as large on-resistance, large supply current, and large parasitic capacitance. The on-resistance of the analog switch architecture in this paper is 5 Ω and the on-resistance flatness is 0.1 Ω. The supply current is as low as 0.87 μA while the whole chip area is 0.65 mm2.

Similar content being viewed by others

Data Availability

Data sharing is not applicable to this article as no new data were created or analyzed in this study.

References

D. Aksin, M. Al-Shyoukh, F. Maloberti, Switch bootstrapping for precise sampling beyond supply voltage. IEEE J. Solid-State Circuits 41(8), 1938–1943 (2006)

M.R. Asgari, O. Hashemipour, Body effect compensation of analog switches using variable voltage function. IEICE Electron. Express 8(3), 189–194 (2011)

Y. Cao, T. Zhang, Y. Chen, F. Ye, J. Ren, An operational amplifier assisted input buffer and an improved bootstrapped switch for high-speed and high-resolution ADCs, in 2018 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–5 (IEEE, 2018)

H. Chen, L. He, H. Deng, A high-performance bootstrap switch for low voltage switched-capacitor circuits, in 2014 IEEE International Symposium on Radio-Frequency Integration Technology, pp. 1–3 (IEEE, 2014)

G.-C.I. Chiranu, C. Tudoran, O. Neagoe, G. Brezeanu, Improved CMOS analog switch, in 2019 International Symposium on Signals, Circuits and Systems (ISSCS), Iasi, Romania, pp. 1–4 (2019)

J. Crols, M. Steyaert, Switched-opamp: an approach to realize full CMOS switched-capacitor circuits at very low power supply voltages. IEEE J. Solid-State Circuits 29(8), 936–942 (1994)

C. Deng, H. Yang, Q.M. Gong, A compact low loss high isolation DC-45GHz SPST switch in 0.13-μm CMOS process. Microelectron. J. 80, 1–6 (2018)

Y. Fu, Design and Research of SOI All Dielectric Isolated COMS Analog Switch (University of Electronic Science and Technology, 2014)

R. Hu, J. Tang, A novel bootstrapped switch, in 2012 2nd International Conference on Consumer Electronics, Communications and Networks (CECNet), pp. 1545–1547 (IEEE, 2012)

G. Huang, P. Lin, A fast bootstrapped switch for high-speed high-resolution A/D converter, in 2010 IEEE Asia Pacific Conference on Circuits and Systems, pp. 382–385 (IEEE, 2010)

K. Ishida, K. Kanda, A. Tamtrakarn, H. Kawaguchi, T. Sakurai, Managing leakage in charge-based analog circuits with low-V/sub TH/ transistors by analog T-switch (AT-switch) and super cut-off CMOS, in Digest of Technical Papers. 2005 Symposium on VLSI Circuits, Kyoto, Japan, pp. 122–125 (2005)

K. Ishida, K. Kanda, A. Tamtrakarn, H. Kawaguchi, T. Sakurai, Managing subthreshold leakage in charge-based analog circuits with low-V/sub TH/transistors by analog T-switch (AT-switch) and super cut-off CMOS (SCCMOS). IEEE J. Solid-State Circuits 41(4), 859–867 (2006)

J. Ju, S. Prentice, Application of analog switches in handheld and portable devices. Glob. Electron. China 02, 30–31 (2004)

H. Kawaguchi, K. Nose, T. Sakurai, A Super Cut-Off CMOS (SCCMOS) scheme for 0.5-V supply voltage with picoampere stand-by current. Solid State Circuits 35, 1498–1501 (2000)

S. Kim, Y.H. Lee, H.J. Chung, Y.C. Jang, A bootstrapped analog switch with constant on-resistance. IEICE Trans. Electron. 94(6), 1069–1071 (2011)

Y.V. Krouglov, V. Barinov, A.G. Timoshenko, The advanced boost circuit for MOS analog switch, in 2008 4th IEEE International Conference on Circuits and Systems for Communications, pp. 568–571 (IEEE, 2008)

D.-G. Li, Y.-J. Cen, P. Yang, The design of high linear bootstrapped S/H switch, in IEEE 3rd International Conference on Integrated Circuits and Microsystems (ICICM), pp. 51–55 (2018)

H. Mizutani, R. Ishikawa, K. Honjo, High isolation MMIC switch design technique based on novel high-low-pass switch concept, in 2015 European Microwave Conference (EuMC), pp. 56–59 (2015)

S. Naghavi, N. Sharifi, A. Abrishamifar, A novel analog switch for high-precision switched-capacitor applications. Int. J. Circuit Theory Appl. 46(4), 764–778 (2018)

T.B. Nazzal, S.A. Mahmoud, Low-power bootstrapped sample and hold circuit for analog-to-digital converters, in 2016 IEEE 59th International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 1–4 (IEEE, 2016)

P. Pouya, A. Ghasemi, H. Aminzadeh, A low-voltage high-speed high-linearity MOSFET-only analog bootstrapped switch for sample-and-hold circuits, in 2015 2nd International Conference on Knowledge-Based Engineering and Innovation (KBEI), pp. 418–421 (IEEE, 2015)

B. Razavi, Design of Analog CMOS Integrated Circuits (Xian Jiaotong University Press, 2002)

B. Razavi, The design of a bootstrapped sampling circuit [the analog mind]. IEEE Solid-State Circuits Mag. 13, 7–12 (2021)

B. Razavi, The bootstrapped switch [a circuit for all seasons]. IEEE Solid-State Circuits Mag. 7, 12–15 (2015)

A. Ramkaj, F. Tavernier, M. Steyaert, Fast switch bootstrapping for GS/s high-resolution analog-to-digital converter, in 2015 11th Conference on Ph. D. Research in Microelectronics and Electronics (PRIME), pp. 73–76 (IEEE, 2015)

Y. Ren, X. Wang, K. Zhang, Analysis and solution of crosstalk mechanism between analog switch channels. J. Ordnan. Equip. Eng. 40(06), 198–201 (2019)

L. Ren, Design of Single-Pole Double-Throw Analog Switch Chip Base on SOI All Dielectric Isolated Technology (University of Electronic Science and Technology, 2020)

S. Sen, K.A. Shaik, J. Mukherjee, A distortion reduction technique for bootstrapped-gate MOS sample-and-hold circuits using body-effect compensation, in 2014 IEEE Faible Tension Faible Consommation, pp. 1–4 (IEEE, 2014)

A. Sepahvand, O. Hashemipour, A low voltage bootstrapped switch based on zero DC offset input voltage. IEICE Electron. Express 5(22), 932–935 (2008)

S. Sinha, D. Bansal, K.J. Rangra, RF MEMS compact T-type switch design for switch matrix applications in space telecommunication, in IEEE-International Conference On Advances In Engineering, Science And Management (ICAESM-2012), pp. 130–135 (IEEE, 2012)

M. Sotoudeh, F. Rezaei, A new dual-network bootstrapped switch for high-speed high-resolution applications. Comput. Electr. Eng. 91, 107–125 (2021)

V.M. Srivastava, K.S. Yadav, G. Singh, Analysis of drain current and switching speed for SPDT switch and DPDT switch with the proposed DP4T RF CMOS switch. J. Circuits Syst. Comput. 21(4), 66 (2012)

J. Steensgaard, Bootstrapped low-voltage analog switches, in 1999 IEEE International Symposium on Circuits and Systems (ISCAS), vol. 2, pp. 29–32 (IEEE, 1999)

C. Su, S. Zhang, H. Shi, A dual single-pole double-throw high speed analog switch. Microelectron. J. 36, 814–816 (2006)

J.J. Su, K.S. Demirci, O. Brand, A low-leakage body-guarded analog switch in 0.35 um BiCMOS and its applications in low-speed switched-capacitor circuits. IEEE Trans. Circuits Syst. II Express Briefs 62(10), 947–951 (2015)

C. Tudoran, O. Neagoe, F. Draghici, G. Brezeanu, Nonvolatile analog switch for low-voltage applications. Electronics 10(6), 736 (2021)

C. Wei, R. Wei, M. He, Bootstrapped switch with improved linearity based on a negative-voltage bootstrapped capacitor. IEICE Electron. Express 18, 66 (2021)

J. Xi, Y. Zhang, Z. Guo, A Low Ripple Charge Pump for Bias Circuit, 52nd edn, vol. 1, pp. 21–28 (Nankai, 2019)

H. Zhang, H. Gao, Y. Ma, A. Forbes, R. Pavio, G.P. Li, A novel high efficiency and linearity power amplifier with over-voltage protection, in 2007 IEEE/MTT-S International Microwave Symposium, pp. 147–150 (2007)

L. Zhang, J. Li, Y. Wang, J. Hao, X. Jin, Y. Peng, J. Luo, Design and verification of a high performance analog switch circuit. Analog Integr. Circuits Signal Process 109(3), 673–681 (2021)

S. Zheng, K. Sheng, J. Chen, W. Gai, A clock-feedthrough compensation technique for bootstrapped switch, in 2017 International Conference on Electron Devices and Solid-State Circuits (EDSSC), pp. 1–2 (IEEE, 2017)

H. Zhuang, Q. Cao, X. Peng, H. Tang, A bootstrapped switch with accelerated rising speed and reduced on-resistance, in 2021 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–5 (IEEE, 2021)

N. Zimmermann, R. Wunderlich, S. Heinen, An over-voltage protection circuit for CMOS power amplifiers, in 2008 15th IEEE International Conference on Electronics, Circuits and Systems, pp. 161–164 (2008)

Acknowledgements

This work is supported by the National Natural Science Foundation of China (Grant Nos. 61774129, 61827812, 61704145), Hunan Science and Technology Department Huxiang High-level Talent Gathering Project (Grant No. 2019RS1037), and Hunan Province Scientific and Technological Breakthrough of Strategic Emerging Industries and Transformation Projects (Grant Nos. 2020GK2018, 2019GK4016, 2020RC1003).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Peng, D., Jin, X. Analysis and Design of High Performance Analog Switch Circuit Based on 0.25 μm BCD Process. Circuits Syst Signal Process 42, 1893–1910 (2023). https://doi.org/10.1007/s00034-022-02206-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02206-0